信号在传输过程中由阻抗变化引起的失真怎么办?这些设计技巧能帮您

描述

阻抗变化受下列变化影响:导线宽度、相邻的导线和器件之间的间距,以及距参考平面的距离。然而,印刷电路板(PCB)发生这些阻抗的变化时,并不总是那么明显。一个非常有用的做法是检查PCB布局或系统图,以快速识别可能通过模拟需要多次分析的任何问题区域。执行这类检查时,您应该跟踪从源到接收器的信号,寻找任何违反表1所列指南的行为,以及我接下来会讨论的故障点。

|

单端型 |

差分型 |

|

导线宽度必须是常量 |

差分导线间距(耦合)和导线宽度必须是常量 |

|

导线和其他器件和导线之间的间距应至少三倍于导线宽度 |

|

|

恒定参考平面必须存在于导体整个长度的相同距离 |

|

表1:最大限度减少反射的检查指南

并非每次都必须遵守表1中有关传输线的指南。以下为可能发生违反这些准则的常见区域:

-

球栅阵列(BGA)走线——尤其针对通向内部行/列的多输入/输出(I / O)器件。

-

导通孔,您必须对此格外小心,以确保当传输线路信号导通孔经过PCB层时,看到一个恒定的固定参考平面。

-

在线器件和连接器。器件和连接器的印刷电路板(PCB)封装与将它们相连的传输线封装相比,通常具有不同尺寸,这导致阻抗变化,从而造成反射变化。

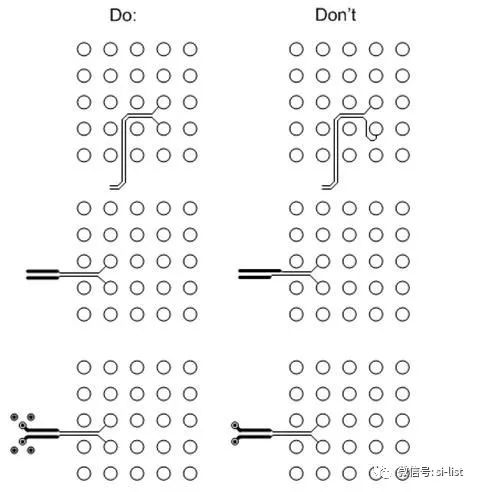

当通向BGA器件或从BGA器件走线时,通过管理走线宽度和相邻的导通孔或焊盘的间距,来保持一个恒定阻抗。图1所示为从DS125DF1610 16通道12.5Gbps重定时器数据表(一个196引脚数BGA器件)中摘录的一些常用注意事项。

可执行项 不可执行项

图1:BGA布线规则

从顶部开始,图1中的首个规则组合向您展示如何正确地管理内部BGA行和列的差分走线收集集和布线。第二个规则组合突出显示一个名为颈缩的常用技术,其中,有时有必要在BGA设备下方传送信号时使用较小的导线宽度。始终对称地执行颈缩行为,其中颈缩长度等于差分对的两条导线长度。

图1中的第三对组合所示为确保信号导通孔具有恒定参照平面的一种可能方法。这种情况下,“可执行事项”图形显示与信号导通孔相邻布置的四个接地导通孔阵列。这使得信号在穿过PCB其它层时可看到一个恒定接地参考。并不总是每次都需要使用4个接地通孔。多数情况下,两个接地导通孔已足够。一定要进行模拟,以验证系统的需求。

管理在线器件和连接器封装焊盘的阻抗非常重要。检查过程中,寻找的一个重点项目是封装焊盘在参考平面中是否存在任何缺口或空隙。空隙或缺口可能每次并非必需项,但若您看到传输线的导线宽度与器件焊盘之间存在显著区别时,您需要进行调查!

图2所示为运行到一个串联式器件(此情况下为一对交流耦合电容器)的导线示例。图3所示为此导线下方的接地层。注意器件焊盘下方的缺口,这有助于使阻抗更靠近传输线,以减少反射。同时图4所示为顶部蚀刻和接地层。

图2:在线器件示例——信号层

图3:串联式器件示例——接地层

图4:在线器件示例——信号层和接地层

最后,有必要进行仿真模拟,以验证您的PCB布局,并确保最小的反射将会发生。使用最佳实践可执行良好的检验,并牢记此篇博文中的指南可以帮助减少仿真次数和模拟时间。

-

如何确保DMA传输过程中的数据都是好的?2024-04-12 452

-

PCB设计中遇到的阻抗不连续问题及解决方法2023-09-22 2382

-

水泵控制使用过程中出现信号报警怎么办2023-07-25 6157

-

相位响应信号在系统中传输过程中的相位变化2023-06-20 7066

-

PCB设计总有几个阻抗没法连续的地方,怎么办?2023-04-10 1519

-

在传输过程的信号要如何描述?2023-03-08 2348

-

PCB设计总有几个阻抗没法连续的地方,怎么办?2022-02-20 1412

-

在I/O端口或内部电路信号传输过程中采用隔离的方式2021-11-11 1376

-

PCB设计总是有阻抗不连续怎么办,一招教你解决烦恼2020-10-27 4424

-

PCB设计阻抗无法连续的解决办法2019-05-31 1504

-

技术分享:PCB设计总有几个阻抗没法连续的地方,怎么办?2019-05-20 1560

-

PCB设计中几个阻抗没法连续的地方怎么办?2018-11-27 2392

-

如何减少SPDIF传输过程中时钟抖动2016-09-28 4684

全部0条评论

快来发表一下你的评论吧 !