基于VHDL语言并选用FPGA设计了一个卷积码编码器

FPGA/ASIC技术

描述

数字信号在有噪声的信道中传输时,由于受到干扰的影响,会发生误码。在设计数字通信系统时,首先应合理设计基带信号,选择调制、解调方式,并采用均衡措施等,使误码率达到指标要求。若仍然不能满足要求时,则必须采用差错控制编码等信道编码技术,使误码率进一步降低。卷积码是深度空间通信系统和无线通信系统中常用的一种差错控制编码。在编码过程,卷积码充分利用了各码字之间的相关性。卷积码广泛应用于卫星通信,GSM,CDMA数字移动通信等通信系统,对其进行研究具有很大的现实意义。

FPGA是可编程逻辑器件,采用FPGA等新型可编程器件进行数字系统设计,不仅使设计的电子产品达到微型化、高集成化和高可靠性,而且开发周期短、成本低、风险小。本设计采用VHDL语言并选用FPGA设计了一个(2,1,9)卷积码编码器。

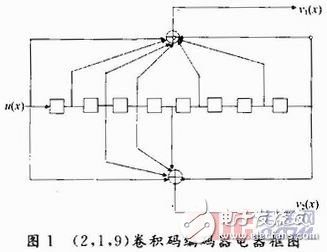

1 卷积码编码器原理 卷积码是1955年由Elias等人提出的一种十分常见且有效的前向纠错码(FEC)。卷积码(n,k,N)主要用来纠随机错误,它的码元与前后码元有一定的约束关系。卷积码(n,k,N)将是个信息比特编为n个比特,N为约束长度。即卷积码的当前码元不仅与当前输入的k个信息码元有关,而且还与前面(N-1)个时刻输入的信息码元有关,卷积码的纠错能力不仅与约束长度有关,还与采用的译码方式有关。总之,由于n,k较小,且利用了各组之间的相关性,在同样的码率和设备的复杂性条件下,无论在理论上还是实践上都证明:卷积码的性能至少不比分组码差。2 卷积码编码器设计2.1 编码设计原理 卷积码(n,k,N),其一般形式为一个由N段组成的输入移位寄存器,每段有k级;一组n个模2和相加器;一个由n级组成的输出移位寄存器。对应于每段k个比特的输入序列,输出n个比特。整个编码过程可以看成是输入信息序列与由移位寄存器与模2和连接方式所决定的另一个序列的卷积。 本设计的卷积码是(2,1,9),编码效率是1/2比率,约束长度为9,码发生器函数为:g(1,1)=(111101011),g(1,2)=(101110001)。对于每个输入到编码器的数据比特产生两个编码符号v1和v2,然后依次输出;编码符号v1,用发生器函数编码g(1,1),第一个输出;编码符号v2用发生器函数g(1,2)编码,第二个输出。卷积码编码器初始状态为全“0”状态。随后第一个输出编码符号为发生器函数g(1,1)产生的编码符号。 电路框图如图1所示。

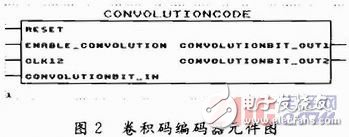

2.2 卷积编码的实现代码 定义输入、输出端口:卷积码的实现电路可由一个8级移位寄存器和2个8级异或门“XOR8”组成。

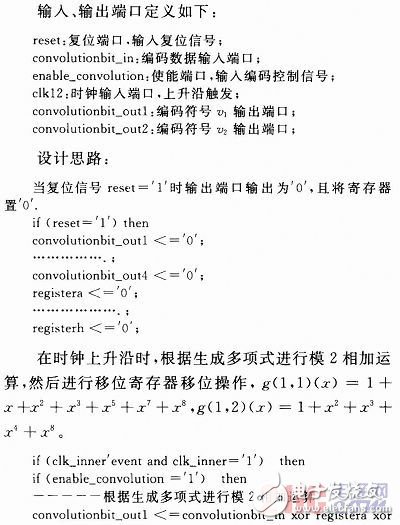

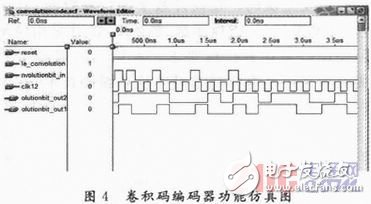

3 卷积码编码器仿真3.1 功能仿真 仿真前设置输入信息序列Convolutionbit-in=“1101001001”,对应时钟为400 ns。图3为(2,1,9)卷积码,码发生器函数是:g0=(111101011),g1=(101110001)的理论编码结果。卷积编码器VHDL功能仿真波形如图4所示。

比较卷积码编码器的理论结果(见图3)和功能仿真图(见图4),仿真结果与理论计算完全一致。

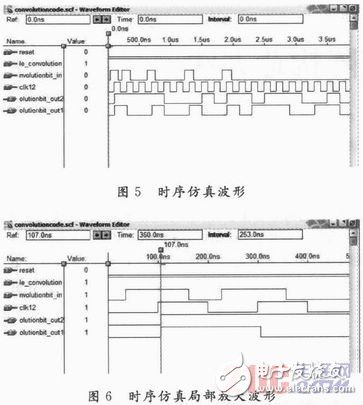

3.2 时序仿真 在不考虑时延的情况下,对照图4与图5,两者仿真波形一样。从图6可以看出卷积编码器的时延为7.0 ns,这是因为功能仿真不考虑信号时延等因素,而时序仿真则是选择了具体器件并完成布局布线后进行的含定时关系的仿真,所以其仿真更接近真实器件运行特性,因而仿真精度更高。由于不同器件的内部时延不一样,不同的布局,布线方案也会给时延造成很大的影响,因此在设计实现后,有必要对网络和逻辑块进行时延仿真,分析定时关系,估计设计性能。

时序仿真后,再进行器件编程和调测。实测结果完全正确,达到了设计要求。4 结语 本文阐述了卷积码编码器的工作原理,利用FPGA器件,设计出了(2,1,9)卷积码编码器。仿真及测试结果表明,达到了预期的设计要求,并用于实际项目中。

-

深度解读VHDL语言的卷积码和Viterbi译码的实现2021-05-12 3489

-

怎么利用VHDL语言实现卷积码编解码器的设计2021-04-29 1375

-

如何设计基于FPGA的卷积码编译码器?2019-10-14 1395

-

在FPGA上实现咬尾卷积码的最优算法设计2019-05-03 6838

-

卷积码编码和维特比译码的原理、性能与仿真分析2018-11-14 14411

-

卷积编码之维特比译码介绍 浅析卷积码之应用2018-08-21 4689

-

卷积码编码器怎么画 浅谈卷积码编码器设计2018-08-20 15455

-

卷积码的Viterbi高速译码方案2010-07-21 1099

-

卷积码,什么是卷积码2010-04-03 7689

-

卷积码,卷积码是什么意思2010-03-19 2281

-

卷积码/Viterbi译码,卷积码/Viterbi译码是什么2010-03-18 2506

-

基于CPLD的卷积码编解码器的设计2009-08-10 3386

-

什么是卷积码? 什么是卷积码的约束长度?2008-05-30 20161

全部0条评论

快来发表一下你的评论吧 !