采用FPGA与IP来实现DDR RAM控制和验证的方法

FPGA/ASIC技术

描述

随着高速处理器的不断发展,嵌入式系统应用的领域越来越广泛,数字信号处理的规模也越来越大,系统中RAM规模不断增加,比如视频监控、图像数据采集等领域,图像处理的实时性对RAM带宽的要求不断增加,传统的SDRAM在带宽上已经逐渐无法满足应用要求,DDR SDRAM(双倍速率SDRAM)采用在时钟CLK信号的上升和下降沿,双沿做数据传输;比传统的SDRAM只在时钟上升沿传输的方式,传输带宽增加了一倍。DDR RAM已开始广泛应用于嵌入式系统中,正逐步取代传统的SDRAM。

DDR RAM操作速度的提高,对设计者来说,对控制时序的设计有了更高的要求;并且,DDR内存采用的是支持2.5V电压的SSTL-Ⅱ标准,不再是SDRAM使用的3.3V电压的LVTTL标准。在很多的处理器上面并不带有DDR RAM控制器,这对设计者来说,使用DDR RAM难度增加。往往需要在设计中插入控制器实现微处理器或DSP对存储器的控制。

现场可编程门阵列(FPGA)已广泛应用于嵌入式系统中。现在很多FPGA都提供了针对DDR SDRAM的接口特性:其输入输出引脚与SSTL-Ⅱ电气特性兼容,内部提供了DDR触发器、锁相环等硬件资源。使用这些特性,可以比较容易地设计性能可靠的高速DDR RAM控制器。本文针对这一问题,介绍一种采用Lattice FPGA与IP来实现DDR RAM控制和验证的方法。

LatticeXP

LatticeXP器件将非易失的FLASH单元和SRAM技术组合在一起,支持瞬间启动和无限可重构的单芯片解决方案。FLASH单元阵列中保存用户配置文件。上电时,配置文件在1毫秒内从FLASH存储器中被传送到配置SRAM中,完成瞬时上电。

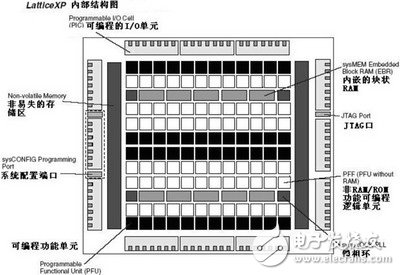

器件内部分为:PIC (可编程的I/O单元),非易失的FLASH MEMORY,SYSCONFIG配置端口,PFU(可编程功能单元),PLL(模拟锁相环),PFF(非RAM/ROM功能可编程逻辑单元),EBR(嵌入式RAM块),JTAG口等几部分(见图1)。

图1 LatticeXP内部结构图

DDR controller IP的生成

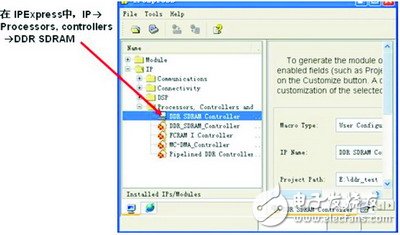

IPExpress是Lattice开发软件中生成IP模块的工具,可根据用户设定的参数生成IP模块,使用非常方便。

点击启动IPexpress进入生成界面(见图2)。在左边选取DDR SDRAM工程,在右边设置工程名称和文件保存地址。

图2 IPexpress界面

点击下一步,开始进入参数设置(见图3)。这里面进行设置DDR RAM的行、列的参数,以及Bank。这些参数都是根据DDR RAM芯片手册进行设置。本文中采用的DDR RAM颗粒是现代公司的HY5DU561622,16M x16,4bank颗粒。

图3 DDR RAM的行、列的参数配置

下一步,进行时序延时上面的设置(见图4)。

图4 DDR RAM颗粒时序参数配置

在这里设置tRAC(行访问周期,RAS Access Cycle/Delay)、tCAC(列访问周期,CAS Access Cycle/ Delay)等参数。这些参数,在DDR RAM颗粒芯片的手册中都有详细的列表。需要特别指出的是,由于芯片提供商会针对不同的DDR标准,例如DDR400,DDR333等,给出不同的延时参数,会是以ns为单位的几个不同的列表,需要根据设计的不同,参考不同的表格。因为IP生成器中采用的是单一参数设置,单位采用了CLK为单位,这就需要根据设计标准以及时钟频率来转换一下,进行设定。本文采用的是DDR266标准,时钟为133MHz,对应的时钟周期为1/133MHz,大约为7.5ns。这样,芯片在DDR266标准的TRCD为20ns(最小值),对应到IP的参数中就是3。其他参数也是类似的换算。

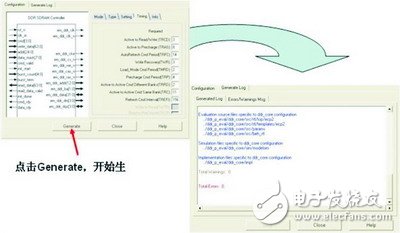

设置完毕以后,点击generate,可以生成IP代码文件,如图5。

图5 IP生成

DDR controller IP的使用与验证

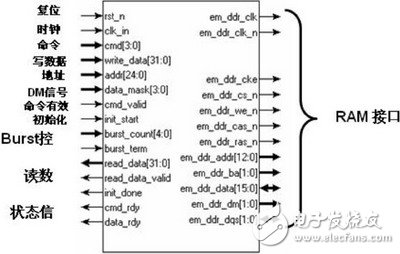

生成的DDR Controller IP的接口结构如图6所示。

图6 DDR Controller接口

RAM接口根据信号的定义,对应DDR RAM接口信号。另一端是用户接口,包括复位、时钟、地址、数据、读写、状态信号等。数据通过用户接口送入,通过IP控制时序送到DDR RAM对用的地址当中。

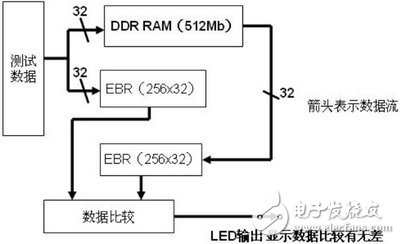

对IP的测试,采用数据写入与读出进行校验的方式来实现。测试框图如图7所示。

图7 测试原理框图

在FPGA内部做两个RAM区域,用于数据的保存。这里使用FPGA内部的RAM块,做了两块256×32b大小的RAM存储区。编写FPGA代码,做一个简单的伪随机序列发生器,通过简单的异或算法,产生32位随机数据序列。产生的数据存入其中一块RAM当中,同时也送到IP的用户接口端,写入DDR RAM。

在256深度的存储区域写满以后,开始从DDR RAM回读数据。并把读取的数据送到FPGA内部另外一块RAM当中。两块RAM中对用地址的数据作比较。如果数据一致,说明DDR RAM读写正常;如果不同,说明DDR RAM读写操作有错误。

由于本设计采用的是DIMM内存条512Mb容量,因此测试时,数据地址采用基址加变址的方式。每一次测试256×32b的数据完成后,循环进入下一次测试时,将起始基地址加256,再进行数据操作。这样最终完整可以扫描512M的数据地址空间,使测试更加完整。这种测试的方法,采用小块地址,多次操作,可以减少FPGA内部RAM的使用量。

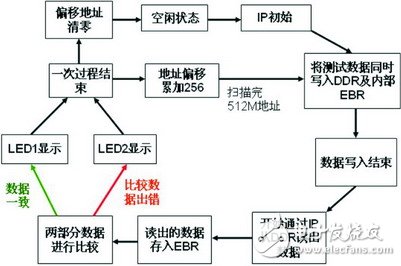

本文中编写的测试代码采用Verilog语言编写,逻辑如图8。

图8 测试代码逻辑状态机

硬件测试结果

本实验是在Lattice的XP ADVANCED版demo板上进行的。

采用的FPGA为LFXP10C-5F384,内存条为Kingston 512M笔记本内存条,RAM颗粒为现代HY5DU561622。测试DDR266连续运行2小时,数据无异常,DDR读写操作完全正常。

结语

在嵌入式系统中应用DDR RAM的越来越多,在设计当中采用FPGA,不仅设计灵活,而且还可以将周边的数字器件综合设计进入FPGA,大大提高系统设计的性价比。

-

基于FPGA的DDR3读写测试2023-09-01 3750

-

基于FPGA的DDR3SDRAM控制器设计及实现简介2021-07-30 983

-

请问如何去实现DDR的读写控制?2021-05-06 1411

-

如何采用EDA或FPGA实现IP保护?2019-09-03 2315

-

基于FPGA器件实现对DDR SDRAM的控制2019-08-14 4685

-

采用EDA软件和FPGA实现IP核保护技术2019-07-29 2808

-

采用Cyclone III FPGA实现DDR2接口设计2019-05-31 2380

-

Xilinx DDR2 IP 核控制器设计方案介绍与实现2017-11-22 6068

-

基于FPGA的验证平台及有效的SoC验证过程和方法2017-11-17 23014

-

DDR2SDRAM控制器IP功能测试与FPGA验证_陈平2017-01-07 931

-

例说FPGA连载39:DDR控制器集成与读写测试之FPGA片内RAM设置与集成2016-10-14 5325

-

【连载视频教程(十三)】小梅哥FPGA设计思想与验证方法视频教程之嵌入式块RAM应用之双口RAM2015-10-23 29712

-

FPGA时分多址的改进型实现方法2011-01-15 466

-

基于FPGA的双口RAM实现及应用2010-04-24 3022

全部0条评论

快来发表一下你的评论吧 !