基于构造的的嵌入式微处理器MicroBlaze的开发与应用

FPGA/ASIC技术

描述

MicroBlaze是一款基于构造的的嵌入式微处理器,它的显著优势在于能满足复杂应用的需求,在除了运行简单的通用应用以外,还能运行操作系统。

设计人员能够在当前所有的赛灵思架构中实施MicroBlaze软处理器,在不同产品系列间实现方便的转换,具有很高的灵活性。但是,MicroBlaze系统设计不仅要在70多种参数中选择,而且还要借助一系列功能强大的嵌入式工具,如果应用只需要简单的微控制器,这种设计方法反倒不实用。

但是,利用适当的技术,用户可以开发构造简单的预配置MicroBlaze微控制器,并方便快捷地将其添加到任何FPGA设计中。可将控制器的实例直接加入HDL。用户能在标准的FPGA设计流程中直接使用,无须特殊的脚本或复杂的步骤。仅需三个文件即可启动设计工作,包括两个硬件实施文件和一个软件定义文件。这种方法使工程师不用学习或者只需很少量的学习就能快速启动FPGA嵌入式设计工作。

在ISE 11.1中启动MicroBlaze软件开发工作,可使用独立的软件开发套件(SDK)进行C和C++应用的创建和调试,而无须全面的嵌入式开发套件(EDK)。

微控制器预配置了两种选项,UART和调试。表1显示了根据微控制器配置不同而给出的各种FPGA系列的尺寸估算值。此外,Virtex器件使用了两个Block RAM,而Spartan器件使用四个Block RAM。对应用代码进行调试后,用户即可移除调试选项,以减小控制器的尺寸。例如,Spartan-6微控制器仅需要220个切片。

微控制器概览简单MicroBlaze微控制器包含的组件有32位MicroBlaze处理器、8KB RAM/ROM、带64KB寻址空间的32位用户接口、中断支持、可选UART,以及可选的JTAG调试接口。图1显示了系统方框图。

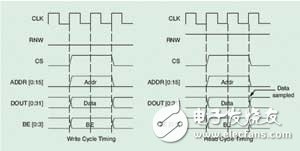

图1 SMM由MicroBlaze处理器、存储器及接口组成根据需要以及实施工具允许的范围,时钟输入可高可低。有效高电平复位输入与输入时钟内部同步。中断输入信号可提供中断支持,微控制器提供服务时用中断确认输出进行确认。此外,简单的地址映射用户接口也同步于时钟,支持用户定制。图2显示了用户接口的时序。可将字节启用用于字节和半字事务处理。

图2 简单的地址映射用户接口同步于时钟

用于可对16位宽的软件映射地址总线进行解码,以将不同的定制接口或外设连接至微控制器。在插入片选(Chip Select)两个时钟周期后对读取数据进行采样。

一些预配置的版本可提供串行16450 UART选项。波特率在软件中进行编程,以保持UART独立于时钟输入。调试选择可使用内部FPGA资源,并直接连接至FPGA JTAG接口,从而通过常规FPGA下载线缆实现应用调试。

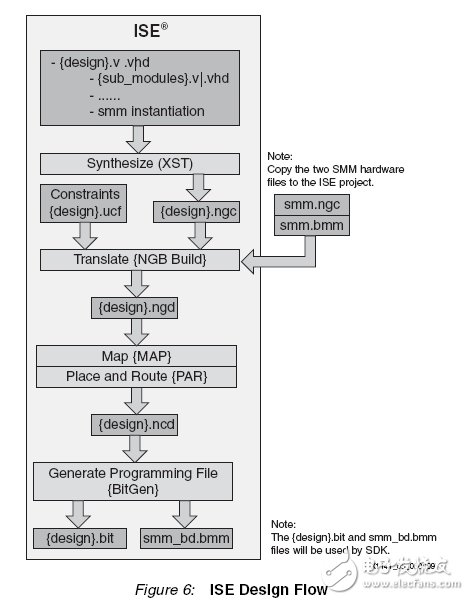

FPGA设计流程FPGA设计流程遵循如图3所示的标准ISE FPGA实施流程。可在FPGA设计中的任何层级级别上通过Verilog或VHDL创建微控制器实例。使用两个与硬件相关的文件微控制器网表(smm.ngc)和Block RAM存储器映射文件(smm.bmm)即能完成FPGA的实施,用户既不必费心学习新的工具,也不用使用复杂的脚本流程。FPGA嵌入式设计从未如此的简单易行。微控制器配置之间的切换非常简单,只需替换所需的网表文件,然后重新实施FPGA即可。

图3 FPGA设计流程遵循标准的ISE FPGA实施流程,无须新工具或脚本

运行实施工具后,将额外生成一个文件,指示微控制器所使用(smm_bd.bmm)的Block RAM的物理位置。

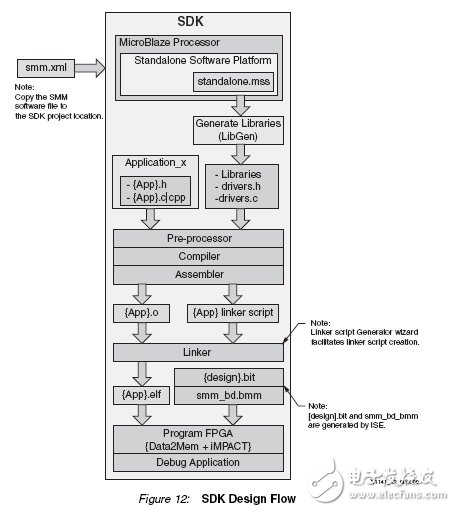

软件应用设计流程单个软件描述文件(smm.xml)包含了启动微控制器应用开发工作所需的全部信息。开发可独立于FPGA设计流程进行,甚至在任何FPGA设计实施之前就能启动。

从ISE 11.1开始,SDK作为独立选项提供,其包含完成软件应用设计所需的全部工具、驱动器、程序库以及实用程序等。

图4 显示了以软件定义文件开始的标准的SDK开发流程。微控制器的地址空间包括8KB的RAM与用户接口,在选择UART选项的情况下,还包括UART寄存器空间。

图4 SDK开发流程始于软件定义文件

设计实例下面介绍一个LCD控制器参考设计实例,这种设计综合采用了简单MicroBlaze微控制器的各种特性。LCD控制器非常适用于小型微控制器实施,因为其硬件接口较慢,也比较简单,初始化序列较长,而且需要大量字符代码。

通过综合采用HDL和C代码,设计可将消息输出至电路板上的字符LCD屏。

HDL可处理硬件接口,而软件则负责初始化和控制LCD屏。

LCD模块的时序较慢,但同时需要指令或数据之间的较大延迟。例如,清空显示的指令需要1.52ms的延迟,然后才能发出下一个指令或数据。部分指令需要40μs的延迟,其他的延迟则需要1μs。我们可在C语言代码中用while回路来处理延迟问题,不过这样做不够准确,而且还会影响编译器的优化。更好的选择是在FPGA中创建软件可载入的32位计数器,以便在到达编程的延迟时触发控制器中断。

MicroBlaze写入地址0x10,以根据用户接口数据总线上的数据启动定时器。MicroBlaze随后将等待中断,以继续执行。MicroBlaze写入用户接口地址0x0会触发LCD控制器硬件接口,硬件接口的时序由HDL处理。用户接口数据总线可捕获指令或数据值。按钮输入能够连接至用户接口地址0x20。

FPGA设计包括顶级模块、LCD硬件时序模块以及软件可寻址可编程定时器。此外,文件还包括简单MicroBlaze微控制器的示例,运行频率为66MHz。

C语言应用包含在单个文件中。该代码不仅可实现MicroBlaze中断、初始化LCD屏幕、管理不同的延迟情况、打印双线LCD、等待按钮输入,同时还可清空屏幕并输出新的消息。

微控制器的定制由于微控制器采用MicroBlaze构建而成,因此设计人员将能获得许多标准的外设和选项,以定制嵌入式系统。用户可能希望部署不同的FPGA架构或添加更多主存储器、浮点单元或标准的SPI或I2C外设。

定制既定的系统需要EDK。它包括众多作为嵌入式项目的不同配置,可根据用户要求进行修改。例如,如果需要16KB的存储器而不是标准的8KB存储器,那么用户可以打开EDK项目,修改MicroBlaze RAM空间并生成新的网表、Block RAM存储器和软件描述文件。用户随后即可将新的文件添加至ISE和SDK项目中。

诚然,虽然简单的MicroBlaze微控制器不能满足所有嵌入式设计的需要,但对于需要简单微控制器来高效提供控制功能的用户来说确实是非常好的选择。此外,其还为希望共享和发布EDK设计的团队提供了一种定则,那就是无论嵌入式设计的尺寸大小,仅需三个文件就能完成整个实施工作。

- 相关推荐

- 热点推荐

- FPGA

- MicroBlaze

-

嵌入式微处理器的功能 嵌入式微处理器原理与应用2024-05-04 2695

-

主流嵌入式微处理器的结构与原理是什么 常见的嵌入式微处理器类型包括2024-04-21 1752

-

什么是嵌入式微处理器?嵌入式微处理器有哪些?2024-03-29 2258

-

嵌入式微处理器的原理和应用2024-03-28 2386

-

嵌入式微处理器与应用2021-07-30 1103

-

嵌入式微处理器MicroBlaze有什么优点?2019-10-11 2022

-

嵌入式微处理器是由什么组成2019-09-11 5437

全部0条评论

快来发表一下你的评论吧 !