堆叠硅片互联技术和28Gbps 收发器引领 FPGA 创新的新时代

FPGA/ASIC技术

描述

超越摩尔定律的堆叠硅片互联技术和28Gbps 收发器引领 FPGA 创新的新时代

赛灵思最近推出了两款最新创新技术,进一步扩展了 FPGA 的应用可能与市场范围。去年 10 月底,赛灵思宣布在即将推出的 28nm 高端Virtex®-7 系列中新增堆叠硅片互联(SSI) FPGA(见《赛灵思中国通讯》第 37 期)。最新创新型架构可在单个硅中介层上连接数个芯片,这使赛灵思的 Virtex-7 FPGA 能够集成多达200 万个逻辑单元(是已宣布推出的任何其他 28nm FPGA 的逻辑容量的两倍),从而在当代工艺技术中实现下一代产品的功能。

随后,赛灵思于去年 11 月底还透露了 Virtex-7 HT 系列器件的相关信息。Virtex-7 HT 器件利用 SSI 技术,在单个芯片上集成了 FPGA 和高速收发器芯片,这对通信领域的客户而言是一个巨大的技术飞跃,而且能满足越来越多应用对高速 I/O 的需求。最新 FPGA 能够在同一器件上容纳众多 28Gbps 收发器以及数 10 个13.1Gbps 收发器,这有助于在新设备标准制定之前为当前 100Gbps 通信设备以及 400Gbps 通信线路卡的开发做好准备。

超越摩尔定律

Intel 联合创始人戈登摩尔于1965 年 4 月 19 日在《电子》杂志上发表了深有远见的《在集成电路上集成更多组件》一文,此后半导体产业每 22 个月更新换代都将晶体管集成量翻一番。与半导体产业中的其他公司一样,赛灵思过去多年来也认识到,要想引领整个市场,就必须跟上摩尔定律的发展速度,每代工艺技术都要达到相应的集成标准,甚至要当引领标准发展的先锋。

目前,随着最新工艺的发展,复杂性、成本和设计风险日益提高,很多公司都应接不暇,而赛灵思则找到了推进新一代产品 Virtex-7 FPGA 容量翻番的独特方法。赛灵思推出了业界首批堆叠硅片架构之一,带来了一系列业界最大型的 FPGA。其中最大型的 FPGA 就是 28nm Virtex-7XC7V2000T,其包括 200 万个逻辑单元和 305,400 个逻辑切片,BRAM容量高达 46,512 kb,还包括 2,160个DSP 切片 和 36 个 GTX 10.3125 Gbps 收发器。Virtex-7 系列包括多

个 SSI FPGA,采用单片 FPGA 配置。Virtex-7 是 7 系列的高端产品,其他 7 系列产品还包括新型低成本低功耗 ArtixTM FPGA 以及中端 KintexTM FPGA,上述所有产品均采用了统一面向应用的模块化模块 (ASMBL) 架构。

最新 SSI 技术不仅能满足用户使用业界最大型 FPGA 的要求,主流逻辑芯片中成功部署堆叠芯片还能带来重大的半导

体设计成果。大多数公司还在评估堆叠芯片架构时,赛灵思就推出了堆叠硅芯片,有望改善容量和集成度,节约 PCB 板级空间,甚至进一步提高产量。大多数公司为了赶上摩尔定律不得不选择堆叠硅片技术,而赛灵思则充分利用该技术让其脱颖而出,在单个 IC 上组合匹配多种不同类型的芯片,从而大幅提升系统性能,降低材料清单成本 (BOM),提高功率效率。

堆叠硅片架构

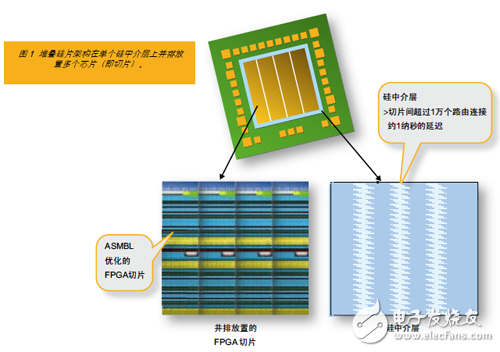

赛灵思负责 FPGA 开发与芯片技术的企业副总裁 Liam Madden 指出:“这种新的堆叠硅片互联技术使赛灵思能够为当代工艺技术带来下一代的高密度性能。随着芯片尺寸的增大,良率将呈指数级下降,因此构建大型芯片相当困难,而且成本不菲。最新架构使我们能够构建一系列较小型芯片,然后通过硅中介层并排连接在该中介层上,看起来就像一体化芯片一样,而且功能一样。”(如图 1 所示)

图 1 堆叠硅片架构在单个硅中介层上并排放置多个芯片(即切片)。

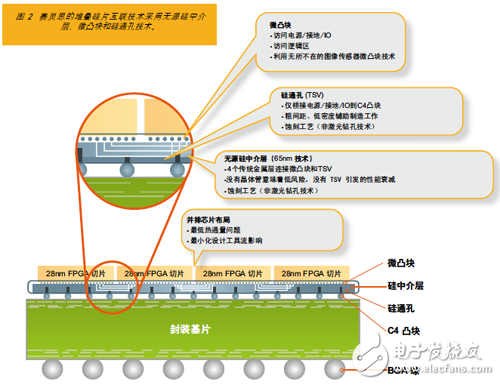

每个芯片通过硅中介层中各层互联,其方式类似于印制电路板上各层分立组件的互联(如图 2 所示)。芯片和硅中介层通过多个微凸块连接。该架构还采用穿过无源硅中介层的硅通孔 (TSV) 协助实现器件上每个芯片不同区域以及片外资源之间的通信(如图 3所示)。相邻 FPGA 芯片间的数据在10,000 多个路由连接之间流动。

图 2 赛灵思的堆叠硅片互联技术采用无源硅中介层、微凸块和硅通孔技术。

图 3 28nm Virtex-7 器件真实的横截面图。我们看到 TSV 通过硅中介层连接微凸块(顶部虚线)。

Madden表示,采用无源硅中介层而非系统级封装或多芯片模块化配置能够带来巨大优势。他说:“我们采用常规硅

片互联或金属化来连接器件上的芯片,这样硅片中的芯片连接数量大大超过系统级封装。而且这种方法的最大优势还在于节能性。由于我们通过硅片互联技术连接芯片,因此功耗远远低于通过大线迹、封装或电路板连接的方式。”

事实上,SSI 技术将单位功耗芯片间连接带宽提升了 100 倍以上,时延减至五分之一,而且不会占用任何高速串行或并行 I/O 资源。

Madden 还指出,微凸块并非直接连接于封装,而是互联到无源硅中介层,进而连接到相邻的芯片。这种设置方法能够避免微凸块受到静电放电的影响,从而带来巨大优势。通过芯片彼此相邻,并连接至球形栅格阵列,该器件避免了采用单纯的垂直硅片堆叠方法出现的热通量、信号完整性和设计工具流问题。

与单片 7 系列器件一样,赛灵思在Virtex-7 系列的 SSI 产品中也采用了台基电的 28nm HPL(高性能低功耗)工艺技术。该技术由赛灵思和台基电联合开发,有助于推出功率效率和性能相平衡的 FPGA(请参见封面故事辅助信息,《赛灵思中国通讯》第 37 期)。

无需新工具

Madden 指出,SSI 技术虽然大幅提升了容量,但不会使客户设计方法产生巨变。他说:“该架构的优势之一在于,我们能明确[器件中不同芯片]每个切片的自然分区边缘,就好像我们在单片FPGA 架构中采用迹线一样。这就意味着我们不必大幅改变工具就能支持新的器件。因此,客户不必对设计方法或流程做大幅修改。”

Madden 同时表示客户将受益于流程新增的平面规划工具,因为现在他们能够使用众多逻辑单元。

供应链优先

设计方案本身独具创新性, 器件推出的最大挑战之一就在于确保制造、组装、测试和分销具有强大的供应链支持。为了生产最终产品,每个芯片都必须在晶圆级进行全面测试,还要分档、分类并连接于中介层。整体结构要进行封装,而且在最终产品发货给客户之前必须进行最终测试以确保可靠连接。

Madden 的工作团队同台基电及其他合作伙伴联合构建了这样一条供应链。Madden 表示:“其他公司在代工厂和OSAT[ 外包半导体组装与测试] 之间还没有建立供应链,我们此举也是业界首创。”

Madden 还指出:“这种方法还有一大优势,就是我们能采用与当前器件基本相同的测试方法。目前的测试技术使我们能生产已知良好的芯片,这对我们非常重要,因为堆叠硅片技术往往面临着晶圆级测试的挑战。”

由于堆叠硅技术在单 IC 上集成了多个赛灵思 FPGA 芯片,因此从逻辑上说,该架构能确保 FPGA 同其他芯片的组合与匹配,从而创建全新的器件,而这正是赛灵思推出超速 Virtex-7 HT 系列的根本所在。该系列产品在 SSI 技术推出后仅几个星期就成功问世。

全新系列 Virtex-7 HT 器件正好面向正在开发 100~400 Gbps 设备的通信公司。Virtex-7 HT 在单个 IC 上集成了多个包括数十个 13.1Gbps 收发器的28nm FPGA 芯片和包含众多 28Gbps 收发器的 ASIC 芯片。这样,最终器件成品就拥有庞大的逻辑单元组合,而且实线了尖端收发器性能和可靠性。

最大型 Vi r e x - 7 HT 器件包括16 个 GTZ 28 Gbps 收发器、72个 13.1-Gbps 收发器以及逻辑单元和存储器, 收发器性能和容量都大大超越了同类竞争产品( 观看视频1: user/XilinxInc#p/c/71A9E924ED61 B8F9/1/eTHjt67ViK0 )。

Madden 指出:“我们采用堆叠互联技术为 Virtex-7 器件提供 28G 功能。我们在分立的 ASIC 芯片上提供收发器可以优化 28 Gbps 收发器性能和电离功能,从而进一步提高可靠性,满足应用对尖端收发器性能和可靠性的需求。”

视频 1 Howard Johnson 博士介绍带 28 Gbps 收发器的Virtex-7 HT。

随着带宽需求的爆炸性增长,通信领域正加紧构建新网络。无线产业目前积极推出支持 40Gbps 数据传输速率的设备,而有线网络速度则已接近 100Gbps。FPGA 自诞生以来在各代网络设备发展中都发挥了重要作用(请见《赛灵思中国通讯》第 37 期和 32 期的封面报道)。

通信设备设计团队此前一直用FPGA 接收发送给设备的多协议信号,并将信号转换为设备和网络的常用协议,然后再将数据转发到下一个目的地。各公司此前会在监控转换输入信号的 FPGA 和向下一站转发信号的 FPGA之间放置一个处理器,但随着 FPGA 容量的扩大以及功能的增强,单个FPGA就能就能完成接收和发送工作,同时还能进行信号处理,从而为系统带来更高的智能和监控能力,也降低了材料清单成本,而更重要的是,这还能降低网络设备的用电和制冷成本,确保设备全天候可靠运行。

在题为《业界最高带宽的 FPGA支持全球首款 400G 通信线路卡单片 FPGA 解决方案》的白皮书中,赛灵思的 Greg Lara 概括介绍了可受益于 Virtex-7 HT 器件的几种通信设备应用(敬请参阅: )。

Virtex-7 HT FPGA可用于多种应用,例如支持OTU-4 (光传输单元)转发器的100Gbps线路卡,也可用于多路转发器或服务整合路由器,并在低成本 120Gbps 包处理线路卡中支持较高数据处理要求,此外也可用于多个 100G 以太网端口和桥接器以及400Gbps 以太网线路卡。其他潜在的应用还包括面向基站和远程无线电前端的 19.6Gbps CPRI(通用公共无线电接口)以及 100Gbps 和 400Gbps 测试设备。

抖动和眼图

用于上述市场应用的关键在于确保FPGA收发器信号的稳健性可靠性,能够抗抖动、干扰以及电源系统噪声产生的波动等。举例来说,CEI-28G规范要求28Gbps网络设备具有极其严格的抖动容限。

赛灵思的高级市场营销经理Panch Chandrasekaran指出,信号完整性对28Gbps 工作极为重要。为了满足严格的 CEI-28G抖动容限要求, 赛灵思新型FPGA中的收发器采用了基于LC谐振回路设计的锁相回路 (PLL) 和高级均衡电路来抵消确定性抖动的影响。

Ch a n dr a s e k a r a n指出:“ 就28Gbps的信号速度而言,噪声隔离是一个非常重要的参数。由于FPGA架构和

收发器分处于不同的芯片上,因此敏感型28Gbps模拟电路与数字FPGA电路隔离,相对于单片实现方案而言实现了出色的隔离效果。”(请见图4a和4b)

图4a — 赛灵思28 Gbps收发器提供了出色的眼开和抖动性能(采用PRBS31数据模式)。

图4b — 同类竞争产品的28 Gbps信号采用的PRBS7模式简单得多。该信号噪声很大,眼开小得多。眼开大小参见相对尺度。

FPGA设计还包括了最小化信道间歪斜的特性,使器件能支持SFI-S等严格的光学标准。

此外,设计人员在进行GTZ收发器设计时,无需采用外部参考电阻器,从而降低了材料清单成本,简化了电路板设计。内置的“眼扫描”功能可自动检测后均衡数据眼高和眼宽。工程师可用诊断工具进行工作通道的抖动容限分析,并优化收发器参数,从而获得最佳信号完整性,同时避免专业化设备的开支成本。

- 相关推荐

- 热点推荐

- 28gbps

-

赛灵思堆叠硅片互联技术2011-03-28 1370

-

详解赛灵思异构 3D 技术2012-07-06 1506

-

如何开创Internet互联新时代?2021-05-20 1532

-

Altera 发布28-nm FPGA技术创新2010-02-02 1106

-

台积电年中将为Altera试产28nm制程FPGA芯片2010-02-05 919

-

基于28nn Stratix V FPGA的100GbE线路2010-05-31 1755

-

赛灵思推出28Gbps串行收发器的Virtex-7 HT F2010-11-19 1462

-

Altera发售世界上第一款具有28-Gbps收发器的FPGA2011-08-26 2214

-

业界首款28 nm FPGA Kintex-7 10Gbps 收发器性能演示2018-06-01 5237

-

Altera发布能够让FPGA和SoC支持高达56 Gbps数据速率的收发器技术2018-08-19 1771

-

MaxLinear推出单通道28Gbps线性互阻抗放大器MxL91032018-10-23 1384

-

Kintex-7 K325T FPGA上的10Gbps收发器展示2018-11-28 4951

-

Altera在FPGA中演示25-Gbps收发器性能,功能上优于竞争ASSP产品2021-01-04 1463

-

开启技术新时代,英特尔Stratix 10收发器亮点介绍2021-04-02 3909

-

Echelon电力线智能收发器:创新技术引领智能家居新时代2026-03-31 158

全部0条评论

快来发表一下你的评论吧 !