具体介绍ISE中通过编辑UCF文件来对FPGA设计进行约束

FPGA/ASIC技术

描述

本文主要通过一个实例具体介绍ISE中通过编辑UCF文件来对FPGA设计进行约束,主要涉及到的约束包括时钟约束、群组约束、逻辑管脚约束以及物理属性约束。

Xilinx定义了如下几种约束类型:

• “Attributes and Constraints”

• “CPLD Fitter”

• “Grouping Constraints”

• “Logical Constraints”

• “Physical Constraints”

• “Mapping Directives”

• “Placement Constraints”

• “Routing Directives”

• “Synthesis Constraints”

• “Timing Constraints”

• “Configuration Constraints”

通过编译UCF(user constraints file)文件可以完成上述的功能。

还是用实例来讲UCF的语法是如何的。

图1 RTL Schematic

图1 是顶层文件RTL图,左侧一列输入,右侧为输出,这些端口需要分配相应的FPGA管脚。

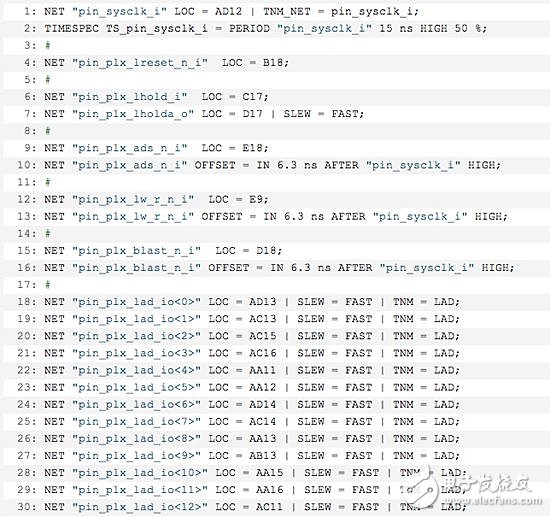

表1. UCF example对上面的UCF文件进行一些注释:

该UCF文件主要是完成了管脚的约束、时钟的约束,以及组的约束。

第一、二行:主要定义了时钟以及对应的物理管脚。

第一行,端口pin_sysclk_i 分配到FPGA管脚AD12,并放到了 pin_sysclk_i group中。那如何得知是AD12的管脚呢,请看图2,FPGA管脚AD12 是一个66MHz的外部时钟。FPGA的开发板肯定有电路原理图供你分配外部管脚。

图2,电路原理图第二行:时钟说明:周期15ns,占空比50%。关键词TIMESPEC(Timing Specifications),即时钟说明。一般的语法是:

TIMESPEC "TSidentifier"=PERIOD "timegroup_name" value [units];

其中TSidentifier用来指定TS(时钟说明)的唯一的名称。

第七行:pin_plx_lholda_o 连接至物理管脚 D17,并配置该管脚电平变化的速率。关键词:SLEW,用来定义电平变化的速率的,一般语法是:

NET "top_level_port_name" SLEW="value";

其中value = {FAST|SLOW|QUIETIO}, QUIETIO仅用在Spartan-3A。

第十行:定义pin_plx_ads_n_i 输入跟时钟的关系。OFFSET IN和OFFSET OUT的约束。OFFSET IN 定义了数据输入的时间和接收数据时钟沿(capture Edge)的关系。

一般的语法是:OFFSET = IN value VALID value BEFORE clock

OFFSET = OUT value VALID value AFTER clock

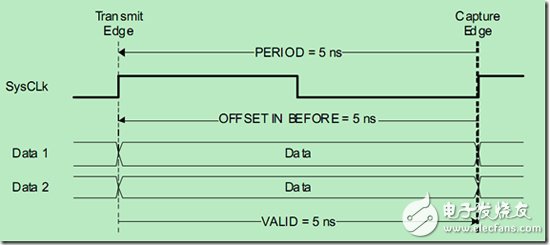

图3 时序图(OFFSET IN)例子:

NET "SysCLk" TNM_NET = "SysClk";

TIMESPEC "TS_SysClk" = PERIOD "SysClk" 5 ns HIGH 50%;

OFFSET = IN 5 ns VALID 5 ns BEFORE "SysClk";

上面的定义了基于SysClk的全局OFFSET IN的属性。时序可看图3.

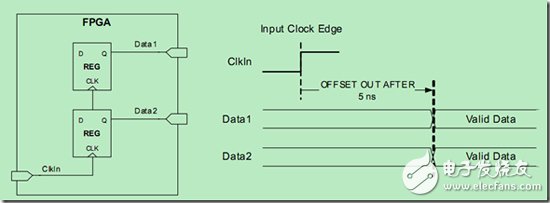

图4 时序图(OFFSET OUT)例子:

NET "ClkIn" TNM_NET = "ClkIn";

OFFSET = OUT 5 ns AFTER "ClkIn";

上面设置主要是定了了时钟跟数据的时间关系,时序图4。可以看到这时一种全局定义,Data1 和Data2输出时间都受到 OFFSET = OUT 5 ns AFTER "ClkIn" 的约束。如果需要单独定义输出端口的OFFSET OUT的,需要制定相应的NET,可参考表1中的第57行。

第18至49行:pin_plx_lad_io<*> 被归到了名称为LAD的TMN(Timing name),这个可以说是GROUP的约束。这样往往给约束带来方便,不用一个一个的NET 或者INST进行约束。

第50至51行:对TIMEGRP 是LAD进行OFFSET IN和OUT的定义。

在时序约束中,在这里还未提及FROM TO的约束。FROM TO的约束主要是用来两个同步模块之间的时间关系的约束。在这里不做深入的讨论。

至此,基本上把一般的UCF文件的作用进行了注释。

注:一般的时间的约束需要通过静态的时序分析,然后再设定相应PERIOD,OFFSET IN 以及OFFEET OUT等的时间参数。

当然在例子中还没有涉及到区域的约束。下面会试图说一下。

ISE进行综合后会将设计代码生成相应的逻辑网表,然后经过translate过程,转换到Xilinx特定的底层结构和硬件原语,MAP过程就是将映射到具体型号的器件上,最后就是就是布线和布局的操作了。

区域的约束相当于将布局过程中指定特定型号的器件的位置,这完全可以通过FloorPlanner的GUI界面进行设置,用图形界面设置完后,配置信息会放到UCF中,这里只介绍UCF的使用。

例如:

INST "Done" LOC = "SLICE_X32Y163" ; #Done映射为一个寄存器,映射到SLICE_X32Y163的位置上。(32,163)相当于一个坐标,可以用FloorPlanner进行查看。

INST"BRAM4/BU2/U0/blk_mem_generator/valid.cstr/ramloop[0].ram.r/v4_init.ram/TRUE_DP.SINGLE_PRIM.TDP"LOC = "RAMB16_X2Y22" ; #RAM16的一个映射。

又例如,X,Y,Z是对应的是寄存器。现在想把它们放在一个指定的区域中,我可以这样写,

INST “X” AREA_GROUP = reg;

INST “X” AREA_GROUP = reg;

INST “X” AREA_GROUP = reg;

AREA_GROUP reg RANGE = SLICE_X1Y1 :SLICE_X1Y6;

注:如何查看INST中的名称呢?在ISE中 Timing constraints editor中可以查看。

注:NET,LOC,TNM_NET,TIMESPEC,PERIOD,OFFSET,IN,OUT,SLEW,HIGH等都是关键字,UCF文件是大小敏感的,端口名称必须和源代码中的名字一致,且端口名字不能和关键字一样。但是关键字NET是不区分大小写的。

其实上述都是约束的入门的内容,如果要想深入的了解的话,请参考Ref1。

-

请教ISE ucf约束文件错误2017-09-23 10199

-

FPGA用 ISE 的开发流程是怎样的流程?2018-09-28 3463

-

【FPGA学习】如何使用 ISE 编写约束文件2018-09-29 6249

-

UCF中的时序约束在组合设计中被忽略了?2018-10-10 2178

-

ISE 12.2读取UCF文件,但所有输入节点都断开连接2019-06-10 2195

-

如何在UCF文件中设置RS232端口的约束?2019-08-23 1808

-

怎么通过时序约束来改进UCF2020-04-15 1631

-

如何通过.ucf约束文件将键盘按钮映射到我的设计中的特定信号?2020-05-15 2074

-

UCF文件出现错误的原因?2020-08-07 1732

-

赛灵思(Xilinx)FPGA用户约束文件的分类和语法说明2017-02-11 2021

-

ISE约束导入vivado总共分几步2017-03-24 9458

-

FPGA设计约束技巧之XDC约束之I/O篇(下)2017-11-17 8133

-

通过一个实例具体介绍ISE中通过编辑UCF文件来对FPGA设计进行约束2017-11-25 7029

-

FPGA约束的详细介绍2018-06-25 7193

-

常用时序约束介绍之基于ISE的UCF文件语法2022-12-28 5196

全部0条评论

快来发表一下你的评论吧 !