MicroBlaze构建了雷达多目标跟踪的嵌入式系统解决了排序的难点

FPGA/ASIC技术

描述

利用FPGA及其片上32位微处理器内核MicroBlaze,构建雷达目标跟踪系统,硬件实现的高速并行性保证了多目标跟踪的实时性,微处理器CPU强大的控制协调功能保证系统的正常运行。针对多目标波门排序这一难点,本文提出了利用顶层软件排序的方法,降低了难度和运算量,提高了灵活性,很好的解决了问题。

1 引言

随着集成电路的不断发展,可编程逻辑器件FPGA因其功能强大,设计灵活,开发周期短等特点,受到越来越广泛的应用.目前在信号处理领域应用系统的设计中,广泛采用的是“FPGA+DSP”的体系结构,其中FPGA完成控制简单,运算量大的算法处理工作,DSP作为系统的处理器进行系统控制,任务协调等工作.然而这种系统需要处理DSP与FPGA之间的通信和数据交换,增加了系统体积和实现复杂度,如果能利用FPGA的逻辑资源来完成这些控制功能,不但提高了系统集成度,也提高了系统的性能.目前FPGA不断朝着实现更高密度,更大容量的千万门级系统发展,同时MCU,DSP,MPU等嵌入式微处理器以IP核的形式嵌入到FPGA中,使得在FPGA上实现算法和控制功能的集成即可编程片上系统(System on Programmable Chip)成为可能.

本文介绍了利用Xilinx最新推出的Spartan 3E系列XC3S500E芯片,及其支持的微处理器软核MicroBlaze构建雷达目标跟踪系统,完成了对多目标的跟踪,波门排序和信息管理存储以及与主机的通信.

2 MicroBlaze简介

MicroBlaze 处理器内核是针对FPGA器件而优化的功能强大的标准32位RISC处理器,运行速度高达150MHz,采用哈佛体系结构,具有独立的32位指令总线和32位数据总线.这两种总线又分为局部存储器总线(Local Memory Bus,LMB)和IBM的片上外围总线(On-chip Peripheral Bus,OPB)两类.LMB总线可提供对片上双端口Block RAM的高速访问,OPB总线可提供对片上外设,存储器,以及基于硬件描述语言编写的算法模块的访问,MicroBlaze可以响应软件和硬件中断,进行异步处理.

3 MicroBlaze的开发环境和开发流程

应用EDK(嵌入式开发套件)可以进行MicroBlaze IP核的开发。工具包中集成了硬件平台产生器、软件平台产生器、仿真模型生成器、软件编译器和软件调试工具等。EDK中提供一个集成开发环境XPS(Xilinx 平台工作室),以便使用系统提供的所有工具,完成嵌入式系统开发的整个流程.EDK中还带有一些外设接口的IP核,如LMB、OPB总线接口、外部存储控制器、SDRAM控制器、UART、中断控制器、定时器等。利用这些资源,可以构建一个较为完善的嵌入式微处理器系统。

图1 MicroBlaze 内核结构图

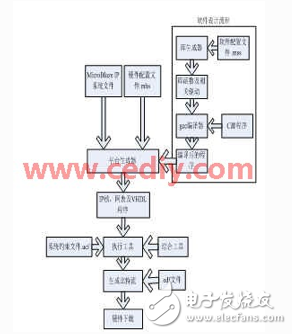

MicroBlaze的开发流程大致有以下四步:

1利用微处理器硬件规范文件(MHS)和微处理器软件规范文件(MSS),定义软件和硬件系统。

2利用系统库生成器,建立相关的库函数和驱动函数,并利用gcc编译器编译编写的C程序源代码。

3利用平台生成器,生成系统网表,HDL代码,片上块存储器初始化代码。

4利用系统硬件模型,综合后的ELF文件和用户约束文件,应用FPGA综合实现工具生成比特流,并利用JTAG接口下载到硬件上进行调试和实现。

图2 MicroBlaze 开发流程图

4.系统总体设计方案

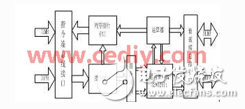

系统总体框图如图三所示,多目标跟踪模块是基于硬件描述语言的底层算法中心,完成多目标的识别,跟踪和预测,它按照OPB总线协议挂在总线上与MicroBlaze通信,MicroBlaze通过配置寄存器,完成对它的控制;A/D转换器采用TLC5540,完成对回波信号的数字化;锁相环CD4046完成对方位脉冲的分频锁相;串口模块完成与主机的通信和交互;中断控制器实现对多中断的协调管理,配置优先级;FLASH采用SST25LF080A,完成最终程序的固化和上电初始化;片上块RAM完成程序的存储和雷达多目标相关信息的存储,基于MicroBlaze的顶层软件算法完成对这些模块的控制和协调,同时完成多目标波门的排序。

图3 系统总体实现方案

5.MicroBlaze在波门排序中的应用

当进行多目标跟踪时,需要对多个目标信息进行存储,同时必须保证多目标波门数据,按其方位和和距离的大小顺序排列,这样才能保证随着雷达方位和距离的扫描,依次对各个目标进行连续的自动跟踪.完全基于硬件的排序,不但时序复杂,而且灵活性很差,在实际中很难实现,一直是全自动跟踪系统实现的难点,而本文通过MicroBlaze顶层算法实现,利用C语言强大的指针功能,很好的克服这些困难.下面就这个问题进行详细的介绍.

为了避免目标录取后由于波门的调整而干扰下一个波门的读取,采用不同雷达扫描周期(2.5s)两张波门表交替存储波门数据(指针Xuint32 *b1为波门表一的首地址指针,Xuint32 *b2为波门表二的首地址指针), 当从波门表1中顺序读取波门数据送入跟踪模块时,将通过雷达目标跟踪模块跟踪滤波得到的下一次探测周期的波门数据存入波门表2中,并进行排序。将片上RAM中的8KB空间挂到OPB总线上用来存储两张波门表,并供CPU调度和访问。

//为两张波门表分配RAM存储空间

b1=(Xuint32*)XPAR_OPB_BRAM_CNTLR_BASEADDR;

b2=(Xuint32*)(XPAR_OPB_BRAM_CNTLR_BASEADDR+0x00000060);

每个32位二进制数存储一个目标的波门信息,具体分配如下:高12位为目标的4096方位脉冲计数,中间16位用来存储目标波门距离计数,最低四位为目标编号。

当正北脉冲信号到来时,表明新一个雷达探测周期开始,触发上升沿中断,在中断程序中,将当前指向波门表一的指针*b1指向波门表二,同时将波门表二的首个目标波门信息送入跟踪模块的寄存器中,并使b1指向下一个目标波门信息,将指向波门表2的指针*b2指向波门表1:

//实现两张波门表的交迭

Temp=b2; b2=b1; b1=temp;

//将当前指针指向的目标波门数据送入底层跟踪模块的寄存器中,同时将指针指向下一个目标波门数据

track_mWriteSlaveReg (baseaddr,*(b1++));

当底层目标跟踪模块完成对当前波门区域目标的探测,会向CPU发出一个探测结束信号,触发上升沿中断,并将当前目标经过α-β外推得到的下一次目标探测周期的波门数据写入指定的寄存器中。在中断程序中,将b1指向的目标波门数据写入跟踪模块的寄存器中,同时b1指向下一个目标波门;将接收到的外推波门数据写入b2指向的波门表中,并与之前得到的多目标外推信息进行距离方位比较排序。这里采用插入排序,因为之前的目标波门数据已经按照扫描周期先后的顺序进行存储了,所以新进入的波门数据递推的与上面的波门数据进行比较,若上一个波门数据大于本波门数据,需要进行相互交换,并向上递推比较,如果上一个波门数据小于本波门数据,则本存储位置正好对应目标的扫描顺序,排序结束。

具体中断程序如下:

//将当前指针指向的目标波门数据送入底层跟踪模块的寄存器中,同时将指针指向下一个目标波门数据

track_mWriteSlaveReg (baseaddr,*(b1++));

//将从底层跟踪模块寄存器中得到的下一周期目标外推波门数据,按照大小排序,插入寄存器中相应的位置

for(i=b2;i>XPAR_OPB_BRAM_CNTLR_BASEADDR;)

{ j=i-1;

If (*i<*j)

{

temp=i; i=j; j=temp;

}

else

exit;

}

当需要增加或删除目标时,我们通过串口模块UART与主机进行命令交互,对串口的操作,

//初始化串口,设置波特率等

XUartLite_Initialize(&UART,XPAR_UARTLITE_DEVICE_ID) ;

//发送和接收数据

XUartLite_Send(&UART,&send_data,1) ;

XuartLite_Recv(&UART,&recv_data,1) ;

当需要增加一个探测目标时,给目标分配新的编号,同时将波门信息存入b2指向的波门表,并如前插入排序,待下一次扫描周期到来时,按顺序进入跟踪寄存器,进行目标的跟踪。

当需要删除某个目标时,在b2指向的波门表中查询目标的编号,并记录下它的存储位置,在下一次扫描周期中,当b1指针指到这个位置时,直接跳过,读取下一个目标的波门数据,这种方法,既取到了效果,又避免了大量数据的移动操作。

6 结束语

利用MicroBlaze微处理器,搭建雷达目标跟踪的嵌入式系统,有效的实现了系统的控制,多任务的协调处理。基于顶层C程序算法实现的多目标波门排序,既利用了软件实现的灵活性和方便性,又兼具嵌入式系统的实时性,有效的解决了问题。随着嵌入式操作系统VxWorks,uc/OSII,uclinux的广泛应用,通过扩充外部存储器,可将这些实时的嵌入式操作系统移植到MicroBlaze软核上,将会在系统多任务,实时性处理的性能上有很大提高,相信将来也会得到广泛的应用。

本文作者创新点:本论文基于FPGA及其片上微处理器软核MicroBlaze构建了雷达多目标跟踪的嵌入式系统,并提出了顶层软件排序的方法,有效的解决了多目标波门排序的难点。

参考文献:

[1]张润泽.船舶导航雷达.人民邮电出版社.1990 02

[2]马建国,孟宪元.电子设计自动化技术基础.清华大学出版社.2004.09

[3]李大军,常青,梅顺良.AIS系统协议栈的研究与实现.微计算机信息,2005,12-2:47-49

[4]Xilinx MicroBlaze Processor Reference Guide April 2, 2005

[5]Xilinx Embedded System Tools Guide June 16, 2004

- 相关推荐

- 热点推荐

- MicroBlaze

- 多目标波门排序

-

基于嵌入式技术的目标跟踪系统设计2022-04-08 7913

-

一种适用于空间观测任务的实时多目标识别算法分享2021-12-21 1739

-

基于KCF的目标跟踪算法研究及嵌入式系统实现2021-08-04 1132

-

多目标跟踪过程中的数据关联技术综述2021-05-08 1043

-

采用FPGA和MicroBlaze进行嵌入式系统设计2021-02-22 1788

-

基于MicroBlaze嵌入式高级应用及设计技巧2018-03-07 1002

-

基于嵌入式PIC32单片机的目标检测与跟踪系统2018-02-15 6417

-

改进霍夫森林框架的多目标跟踪算法2017-12-14 800

-

嵌入式的系统构建2017-10-27 730

-

基于MicroBlaze的嵌入式系统设计2017-03-01 890

-

嵌入式视觉运动目标跟踪技术研究2016-01-06 711

-

基于Xilinx MicroBlaze的嵌入式I/O系统设计2011-05-14 1031

-

嵌入式系统的构建教程2010-03-31 589

-

嵌入式系统的构建2010-03-15 653

全部0条评论

快来发表一下你的评论吧 !