串行背板技术面临新挑战 Xilinx推出串行背板解决方案

可编程逻辑

描述

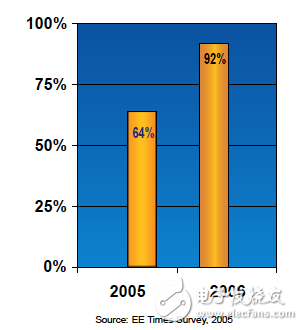

采用串行技术进行高端系统设计已占很大比例。如图1所示,在《EE Times》杂志开展的一次问卷调查中,有92%的受访者表示,2006年已开始设计串行I/O系统,而在2005年从事串行设计的仅占64%。

串行技术在背板应用中的盛行,大大促进了这一比例的提高。随着对系统吞吐量的要求日益提高,陈旧的并行背板技术已经被带宽更高、信号完整性更好、电磁辐射 (EMI) 和功耗更低、PCB设计更为简单的基于SerDes技术的背板子系统所代替。

诸如XAUI和千兆位以太网 (GbE) 等有助于简化设计、实现互通性的标准串行协议的问世,进一步推动了串行技术在高端系统中的应用。此外,PCI工业计算机制造商协会 (PICMG) 制定的AdvancedTCA和MicroTCA等串行背板规格标准,也对串行技术的快速普及起到了重要作用。串行背板技术具有极大的优越性,不但被广泛用于通信系统、计算机系统、存储系统,还被应用到电视广播系统、医疗系统、防御系统和工业/测试系统等。

图1 设计串行I/O系统的工程师的比例

设计“顽症”

尽管串行技术的应用已日益普遍,但许多设计挑战依然横亘在设计人员面前。背板子系统是整个系统的“心脏”,它必须能够在板卡间提供可靠的信号传输。因此,在背板设计中,确保很高的信号完整性 (SI) 是首要任务。

另外,采用能够以极低的误码率驱动背板的、基于SerDes技术的适当芯片集成电路 (IC) 也至关重要。在设计人员重复利用旧背板上的早期元件和设计规则的“早期系统升级”应用中,利用芯片元件来改善SI尤为重要。

开发串行背板协议和交换接口也是设计人员面临的一个挑战。大多数背板设计都利用了采用专有协议的早期专用集成电路 (ASIC) ,甚至一些比较新的背板设计也要求采用专有背板协议。因此,芯片解决方案必须十分灵活,能够支持必要的定制化。虽然ASIC可以实现这一点,但是,ASIC通常成本高,而且存在风险,这是由于产品需求量/销量不确定,可能产生设计缺陷,以及技术规格的更改等。

近来,基于现有标准的模块化交换架构逐渐成为热点技术。这种技术有助于缩短开发周期,但所采用的芯片解决方案必须支持标准协议,并且允许灵活地对最终产品进行独具特色的定制。

当然,还有成本、功耗和上市时间等不可回避的挑战。为了应对串行背板设计中的这一系列挑战,Xilinx推出了Virtex™-5 LXT FPGA平台和IP解决方案。

Xilinx串行背板解决方案

面向串行背板应用的Xilinx® Virtex-5 LXT FPGA的关键技术是嵌入式RocketIO™ GTP低功耗串行收发器。最大的Virtex-5 LXT FPGA中最高可包含24个串行收发器;每个串行收发器的运行速率范围均为100 Mbps至3.2 Gbps。结合可编程架构,该FPGA能够以高达3.2 Gbps的速率,支持几乎所有的串行协议,不论是专有协议,还是标准协议。

对串行背板应用而言,更重要的是内置信号调节特性,包括传输预加重和接收均衡技术。这些特性可以实现速率高达数千兆比特的远距离(通常可达40英寸或更远)信号传输。这两种均衡方法都是通过增强高频信号分量和衰减低频信号分量,来最大限度地降低符号间干扰 (ISI) 的影响。区别在于,预加重是对线路驱动器输出的发射信号执行的,而接收均衡则是对传入IC封装的接收信号执行的。预加重和均衡特性均可编程为不同状态,以实现最优信号补偿。

除了信号调节特性,这些串行接收器还具备其他对背板有用的特性,如可编程输出摆幅 – 可以实现与多种其他基于电流型逻辑电路 (CML) 的器件连接;和内置交流耦合电容器 - 可简化传输线路设计、降低ISI。

IP核

大多数串行背板应用依然采用专有协议。然而,最近的一些新设计已开始采用XAUI和GbE等标准化协议。这主要是因为:一方面这些标准日益成熟,另一方面基于这些协议的交换架构ASSP (专用标准产品) 也不断涌现。利用ASSP实现交换应用可以大大缩短开发周期,但是,设计人员发现,必须通过提供增值功能 (主要是在线卡上) ,来实现产品差异化。

由于这些串行收发器是专为支持大多数串行背板标准协议而设计的,因此FPGA是进行定制的理想平台。这个芯片器件集串行收发器、用于支持兼容标准的设计和各种增值功能的内部资源于一身。

为了帮助缩短设计周期,Xilinx推出了面向XAUI、GbE、SRIO和PCIe等主要串行I/O接口标准的模块化IP核。为了确保互通性,这些IP核经过了一系列兼容性测试和独立的第三方验证。为了简化“轻量级”串行协议设计, Xilinx还推出了Aurora协议 - 特别适用于要求最大限度地降低开销、优化芯片资源利用率的比较简单的设计。

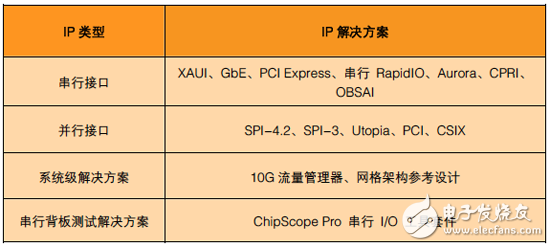

表1 适用于串行背板的Xilinx IP解决方案

由于以太网和PCIe技术的应用范围越来越广,Virtex-5 LXT FPGA也实现了嵌入式三态以太网MAC和PCIe端点模块。这些特性能够帮助那些需要在控制板应用中实现接口的客户节省大量FPGA资源。

除了串行和并行接口IP核,Xilinx还提供了更加完善的IP解决方案,以进一步缩短产品开发周期和上市时间。包括用于优化背板流量的流量管理器和允许板卡之间实现“多对多”连接功能的网格架构参考设计。此外,ChipScope™ Pro串行I/O工具套件可以帮助设计人员快速设置和调试串行收发器,以及进行BERT测试。表1概括性地列出了Xilinx提供的适用于串行背板的IP解决方案。

应用示例

下面,举例说明如何集成所有这些解决方案元件,打造一个适用于星形系统和网格系统的完善的串行背板结构接口FPGA。

星形背板拓扑应用

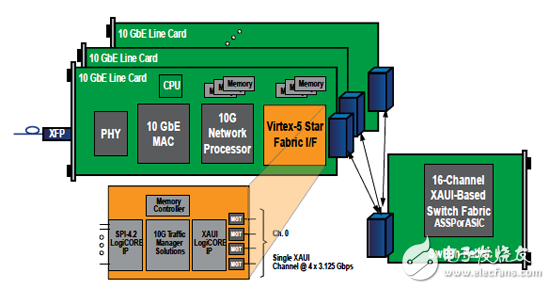

星形背板拓扑十分经济,尤其是在包含大量板卡的系统中,因此,高端基础设备往往采用星形拓扑。图2所示为实现了基于FPGA的星形架构接口的10 GbE线卡示例。该FPGA例化了一个XAUI LogiCORE™ IP核,并利用4个串行收发器连接至16通道XAUI交换架构卡。此外,该FPGA还具备一个LogiCORE SPI-4.2核,以连接至10 Gbps网络处理单元。

图2 10 GbE线卡中的星形架构I/F FPGA

在串行接口和并行接口之间的是流量管理器IP解决方案,它负责对传入和传出业务执行服务质量 (QoS) 相关功能。存储器控制器负责控制主要用作数据包缓冲器的外部存储器。这种架构的优越性包括:提高了SerDes和逻辑电路功能的集成度、借助IP解决方案加快了产品上市时间、同时实现客户特定系统技术规范。还可提供稳定的SI和很低的SerDes功耗 (总功耗仅为400 mW左右) 等。客户可以在低成本/低速度等级的XC5VLX50T器件上实现这一切。

网格架构

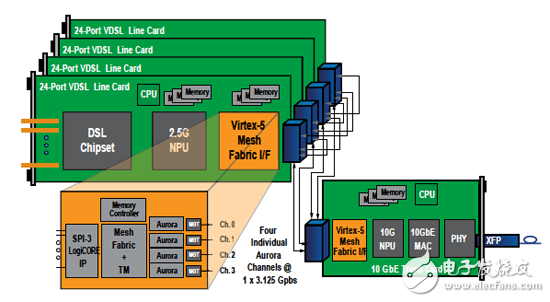

虽然大多数系统都采用星形拓扑,但一些小系统则需要采用网状拓扑。例如,图3所示的5插槽IP DSL接入多路复用器需要在4个24端口VDSL线卡和一个连接至城域以太网的10 GbE回程卡之间实现完全连接。每片板卡都利用1个Virtex-5 LXT器件和4个嵌入式串行收发器来实现4个独立的网格架构物理层通道。这4个链路层基于Aurora协议,以3 Gbps左右的速率传输2.4 Gbps有效负载和编码之类的其它开销。

图3 VDSL线卡中的网格架构I/F FPGA

Trunk卡和线卡分别采用了SPI-4.2和SPI-3 LogiCORE IP核,为网络处理器提供了连接功能。网格架构参考设计和流量管理器解决方案为所有线卡提供了分布式交换和QoS功能。

线卡逻辑接口可以轻松地装入到XC5VLX30T器件上,而trunk卡接口架构则可装入到XC5VLX50T器件上。与星形系统示例类似,利用Virtex-5 LXT解决方案,可以提高集成度、缩短上市时间、优化系统特性、降低功耗和成本等。

结论

如今, 已成为主流技术。随着带宽要求的与日俱增,将有越来越多的应用采用串行背板技术。同时,背板子系统对速率和协议的要求必然会越来越高,设计人员将面临层出不穷的新挑战。

然而,有了Xilinx Virtex-5 LXT FPGA和面向串行背板的现有 IP 解决方案,系统架构设计人员可以在升级早期系统和设计新的背板之间进行选择。具有嵌入式SerDes的Virtex-5 LXT FPGA拥有旨在改善 SI 的关键特性,和实现高度可靠、面积与成本优化的设计所需的高度集成。

此外,Xilinx现有的IP解决方案有助于客户缩短产品开发周期、加快产品上市。有了功能强大的芯片元件与IP核的双剑合璧,Virtex-5解决方案堪称应对最为艰巨的串行背板设计挑战的理想平台。

-

怎样去选择背板总线2021-07-28 3881

-

测试高速串行总线面临哪些挑战?如何应对这些测试挑战?2021-05-10 1920

-

为什么推出Virtex-5LXT FPGA平台和IP解决方案?2021-04-29 1501

-

简述如何利用Virtex-5 LXT应对串行背板接口设计挑战2021-03-22 3087

-

应对串行背板接口设计挑战2019-05-05 1591

-

基于Virtex-5 LXT的串行背板接口设计2019-04-16 1485

-

基于Virtex-5 LXT助力串行背板接口设计2019-04-12 1247

-

Molex推出VITA 66.1耐用光学MT背板互连解决方案2013-04-26 3177

-

背板制造技术2013-03-07 3401

-

串行背板接口设计挑战2011-05-20 1031

-

高速串行接口设计的高效时钟解决方案2010-04-09 1400

-

通讯设计师在高速背板面临的新挑战2009-07-01 861

-

高速背板设计考虑和创新解决方案分析2006-04-16 1469

全部0条评论

快来发表一下你的评论吧 !