基于FPGA的LTE解决方案

可编程逻辑

描述

基带处理信号链带来了严峻挑战,同时也为实现基站收发信机技术的创新创造了大好机会。因此,它成为原始设备生产商实现产品差分的一个关键领域也就不足为奇了。随着人们逐步认识到,用于早期2G和3G系统的许多技术不能满足3GPP 长期演进(LTE)(第4 代无线技术)的性能和延迟要求,基带架构设计领域的竞争变得更加激烈了。

不仅处理链需要比以前强大得多的处理功能,而且所有功能的设计都需要在更短的时间里完成。除了一系列设计挑战外,系统设计人员还需要帮助运营商实现他们的投资和运营成本削减目标。图1显示了基带处理系统设计面临的这些主要压力。

图1 不断演进的基带处理需求带来的挑战

基于FPGA的解决方案可以满足所有这些需求,同时避免常见的性能问题和瓶颈。很多公司正在实施各种计划(如赛灵思新推出的 LTE上行链路通道解码器和 LTE下行链路通道编码器LogiCOREsTM等),希望在单一 IP解决方案中纳入多种关键的第1层功能,进而消除FPGA 普及道路上的种种障碍。

硅技术的进步是推动无线通信取得成功的一个关键因素,因为它可以将更复杂的算法的应用范围从实验室扩大到实际产品中。这方面的一个例子是3G网络中迭代Turbo纠错技术的采用。这是一种新技术,在10年内完成了从最初发现到最终商业推出的整个过程。创新步伐在继续加快。最值得注意的是,空间维度(spatial dimension)通过多种多入多(MIMO)天线技术被应用到无线通信网络中。

然而,随着第4代空中接口的出现,压力不断增加,到了以DSP为中心的传统可编程通道卡架构难以应对的地步。FPGA和DSP之间的传统划分受性能瓶颈的限制。这种限制的影响很大,因为它们之间需要传输的数据量非常大。

那么,我们如何才能消除这种瓶颈?关键在于简化第1层系统架构,消除芯片间所有不必要的数据传输。这种简化流程会带来一些问题——全部与基于数字信号处理器的架构的可扩展性有关。设计人员需要更强大的Intellectual Property(IP)、软件和支持,帮助他们完成向第1层系统架构的迁移。在这种第1层系统架构中,大多数功能在可编

程的硬件中实现而不是在DSP中实现。

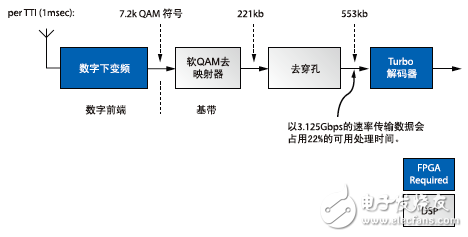

简化第1层设计让我们更深入地分析一下将FPGA单纯用作协处理器时从DSP处理器上卸载Turbo解码功能所带来的问题。在一般的LTE基带设计(见图2)中分析这种分区的有效性时,赛灵思的系统设计工程师们发现,通过SRIO连接在DSP处理器和FPGA之间传输数据就会占用20%以上的延迟和时序预算。令人震惊的是,这还不是最坏情况。如果加上使用更高调制方法(如64-QAM )编码的混合数据,1/3码率的2个MIMO代码字和20-MHz的LTE频带,这一比例很快会变得更高。

一种应对办法是添加更大的“管道”,通过部署速度高达数千兆比特的收发信机连接来传输数据。以这种方式构建系统是完全可行的,但它会导致系统功耗的不必要增加,因为这种情况下需要相对高带宽的高速串行连接来传输数据,而且桥接功能是重复的,因此需要更多硬件资源。

还有一种更理想的解决方案。通过将大部分第1层功能纳入到FPGA中,设计人员就可以避免这部分不必要的开销,用这些资源提高系统吞吐量,缩短延迟,同时降低功耗。功耗的降低这一项就可以直接提高可靠性,降低系统成本并节约运营成本。

图2 常见LTE系统中FPGA和DSP之间需要的数据速率

这种架构方法可以从根本上消除对DSP的需要——当然,如果希望的话也可以使用DSP来执行一些低速率的功能。利用这种分区方法,FPGA就可以实现完整的第1层基带功能,将媒体访问控制和HARQ处理等其它高层功能留给更经济高效的通用处理器或网络处理器完成——这些处理器可以处理额外的远程连接功能。通过将所有高性能、时间关键的功能集成到单一平台上,FPGA可以有效地避开延迟和带宽限制;同时,分区也变成了一项简单得多的任务。

迄今为止,阻碍我们采用这种方法的主要障碍是需要简化从最初的设计到硬件生产的整个流程。此外,对已经习惯DSP设计流程的设计人员来说,他们需要先进的IP和开发工具,帮助他们更容易地利用FPGA 的强大功能,并在其中迅速高效地开发基带功能。赛 灵思的LTE上行链路通道解码器和LTE下行链路通道编码器LogiCOREs可以消除这些障碍,因为它可以将多种关键的第1层功能集成到单一IP解决方案中,而这个解决方案可以通过Xilinx CORE GeneratorTM工具的图形用户界面进行灵活定制。利用这种设计流程,FPGA经验有限的工程师们就可以集中精力于更广泛的系统设计,从而大大减轻开发和集成工作量。

未来发展方向

更快速、低延迟的连接是LTE的一个关键要求,在第4 代以后的未来系统中也将如此。随着这些以数据为中心的无线系统的演进,采用传统的DSP和FPGA分区方法的许多公司将发现,在不同芯片间传输数据的开销高得难以接受。对于希望在产品设计中获得额外优势的设计人员来说,他们可以更轻松地使用基于FPGA的解决方案。摆脱传统系统设计方法束缚的设计人员将能够开发出先进的产品,远离那些将继续困扰竞争对手的性能问题和瓶颈。

-

简化FPGA的电源解决方案2022-11-23 765

-

#硬声创作季 #FPGA FPGA-17-02 按键抖动现象介绍与解决方案分析-1水管工 2022-10-29

-

#硬声创作季 #FPGA Xilinx入门-16 亚稳态现象原理与解决方案-1水管工 2022-10-09

-

LTE系统干扰问题及天线解决方案2021-06-08 1153

-

简述LTE协议测试及解决方案2021-05-26 2482

-

什么是TD-LTE深度覆盖解决方案?2019-08-14 4526

-

求推荐LTE解决方案2018-12-26 2453

-

华为PTN LTE承载解决方案2013-01-10 3666

-

安捷伦推出新款LTE测试解决方案2009-12-28 1255

全部0条评论

快来发表一下你的评论吧 !