基于Xilinx Virtex-5-FXT中的APU简化汽车多媒体系统设计方案详解

可编程逻辑

描述

汽车多媒体系统面临着严峻的技术挑战:如何在漫长的整个产品寿命周期中实现系统的可升级性?轿车和卡车的寿命通常都在十年以上。这就使汽车多媒体系统难以跟上消费电子产品和移动通信标准迅速变化的步伐。在大多数情况下,只更新多媒体软件是不够的,甚至是不可能的。

许多应用,尤其是多媒体编解码器,还需要提高计算性能。然而,为将来的使用而设计具有“后备”计算能力的系统,既不经济,在技术上也不可行,因为许多技术变化是根本无法预见的。

一种解决方案是以某种方式随软件一起升级计算平台,使系统经过升级能够为附加的软件处理负荷提供足够的计算能力。您如果使用 Xilinx® Virtex®-5 FXT器件构建系统,就可以为PowerPC处理器的辅助处理单元 (APU) 增加专用的计算操作,从而为设计赋予更高的计算能力。

Missing Link电子公司致力于打造可重新配置的平台,以便将经久耐用的汽车和航天电子设备与迅速变化的消费和移动通信市场挂起勾来。我们相信,在Xilinx Virtex-5 FXT器件中,PowerPC处理器的APU是块宝。它为嵌入式系统设计人员提供的计算能力,在传统上只有自行定制ASSP器件的“大户”才有幸享用。既然赛灵思用户现在拥有这般可用资源,我们认为每个人都应该利用APU来优化自己的设计。

通过APU扩展指令集的基本原理设计人员想优化嵌入式系统时,通常是设法扩展处于设计核心位置的微处理器的指令集,以此来达到优化目的。从传统上讲这是最佳方案,因为嵌入式系统的复杂性在于设计的软件部分。您也可以增加专用的硬件模块,直截了当地为设计赋予新功能。

不过,您可能会发现,增加指令的方法在弥补硬件变化方面具有某些显著的优越性,并且在一定程度上易于为设计人员所实现。例如,通过扩展指令,您可以更精细地优化设计。另外,扩展指令集通常不会干扰存储器访问,因此具有优化系统整体性能的可能性。尽管有个人、公司和学术研究机构发表过有关论著,然而对于不熟悉这种技法的任何人来说,扩展指令集都可能看似一种“魔术”。但实际上,这并非那么复杂。请试想您如何通过APU接口向PowerPC处理器的指令集增加某些相当简单的指令,以此来优化Virtex-5 FXT设计。

一般而言,要扩展嵌入式微处理器的指令集,您需要明白您是要进行软硬件两方面修改。首先,您要为系统增加硬件模块,以完成专门的计算。这些计算是在 FPGA 结构中并行执行,而不是在软件中依次执行。用赛灵思公司的话来说,这些硬件模块称为“结构协处理模块”,即FCM。您可以用VHDL或Verilog语言编写这些FCM,它们将在Virtex-5 FXT器件的FPGA结构中终结。您可以将一个或多个FCM连接到PowerPC处理器的APU接口。

下一步是调整软件代码,以便启用增加的指令。您有两种可选方法(假定您在用C语言编程)。第一种方法是修改C编译器,令其自动利用附加指令可施展功效的情形。我们把这种方法留给学术界和致力于ASSP的某些人。

第二种方法较为简洁,不必触及编译器,而是使用所谓编译器认识的函数。也就是说,我们要在软件代码中手动调用一个能使用这些附加指令的C宏或C函数。

无论使用哪种方法,我们都必须调整汇编器,使其支持新指令。幸好,赛灵思公司在嵌入式开发套件 (EDK) 中包括了PowerPC的编译器和汇编器,它们已经支持这些附加指令。PowerPC遇到这些新指令时,迅速察觉它们不是其原指令集的组成部分,进而将它们交给APU予以处理。赛灵思公司已将APU配置成解译这些指令,为相应的FCM提供运算元数据,然后让FCM执行计算。

如果这一步妥善完成,则软件在运行时需要的指令就会较少。因此,我们无需提高CPU的时钟频率(这可能造成其他麻烦),就可以从设计中获得更多计算能力。

之所以使用APU,而不是通过PLB总线将硬件模块连接到微处理器,主要是因为PowerPC处理器与APU/FCM之间的较大带宽和较短延迟。另一优越性在于,系统需要通过PLB总线来快速访问外设,而APU不依赖CPU对外设的接口,因此不会增加PLB总线的负担。

APU为PowerPC与FCM之间提供多种接口方式。我们可以使用某种“加载存储指令”法,也可以使用“用户定义指令”(UDI) 法。赛灵思公司 的《用户指南》UG200 的第12章详细介绍了这些技法 ( )。

我们在示例中将使用UDI法,因为这种方法可以最大限度地控制系统,从而实现最高性能。可以从我们的网站下载示例设计,网址是 。

示例设计描述

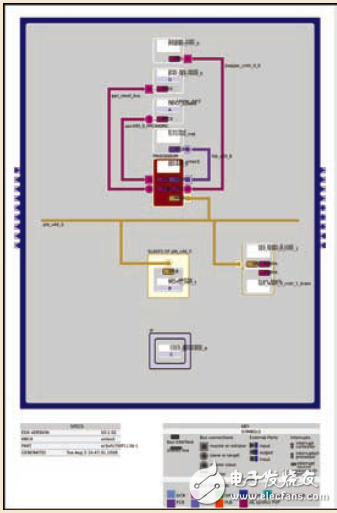

我们用增加一条UDI的方法扩展了PowerPC处理器的指令集,以执行复数乘法运算,这对于许多多媒体解码系统来说是一种简便易行的优化方法。EDK图显示了总体设计,包括如何通过APU将复数乘法器的FCM连接到PowerPC处理器,以及软件如何运用FCM。

图 1 – EDK 处理器系统框图

我们选择复数乘法作为示例,是因其在流式媒体数据解码方面具有广泛的适用性,也是因其能够明确说明如何通过增加专用指令来利用 APU。

复数乘法的定义是,两复数相乘,二者各有一个实值和一个虚值。

(a_R + j a_I, where j*j = -1):

(a_R + j a_I) * (b_R + j b_I) =

(a_R * b_R - a_I * b_I) + j (a_I * b_R + a_

R * b_I)

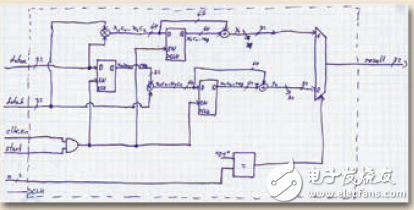

为提高效率,复数乘法硬件模块(cmplxmul) 分三级执行乘法运算。这样,便可在这种多周期的实现中仅使用两个乘法器和两个加法器,从而节省硬件资源。图2所示为复数乘法FCM的框图(草图形式)。

图 2 – 复数乘法协处理器设计如此容易,在坐标纸上即可完成

如cmplxmul.vhd中的VHDL代码所示,我们在三个时钟周期中完成复数乘法运算。我们在文件cmplxmul.vhd中实现了用来完成此复数乘法运算的FCM。文件fcmcmul.vhd提供了FCM/APU接口的封装,用来将FCM连接到APU。如我们将在分步指南(请见侧条)中所示,当使用UDI法时,您可以用此封装用作为模板,将自己的FCM连接到APU(“加载存储指令”法需要不同的互连方式)。

我们用Xilinx EDK/XPS 10.1.02通过使用Xilinx ISE® 10.1.02来综合了我们的设计。我们用ModelSim 6.3d SE对设计进行了仿真和测试。

通过增加专用于硬件加速和协处理的用户定义指令,Xilinx Virtex-5 FXT器件中所含PowerPC处理器的APU让嵌入式软件工程师能够以非常高效的方式加速其系统。以本文所述示例设计为起点,您就会发现掌控 APU 易如反掌,让您无需使用专用工具就能大大提高自家设计的性能。

-

汽车多媒体系统USB Type C端口ESD静电浪涌保护方案2023-05-29 2289

-

汽车多媒体系统端口ESD静电保护方案2023-05-08 1448

-

关于Virtex-5 FXT平台的知识点看完你就懂了2021-05-06 1174

-

如何使用外部FET的DC/DC控制器对 Virtex-5收发器的功率2018-05-18 1074

-

GB国家汽车标准-汽车音视频多媒体系统2016-04-26 1168

-

浅谈国内车载移动多媒体系统发展趋势2014-11-17 4115

-

实时协同设计中多媒体系统的设计与实现2011-09-21 1428

-

基于ARM Linux QT的掌上多媒体系统的设计和实现 (1)2011-08-04 4873

-

多媒体电教室设计方案2010-03-30 1958

-

车载多媒体系统发展态势2010-03-09 3000

-

Xilinx Virtex-5 FXT FPGA开发方案2009-11-24 512

-

车载移动多媒体系统的开发与实现2009-05-16 891

-

多媒体系统的硬件2009-03-10 4714

全部0条评论

快来发表一下你的评论吧 !