基于FPGA的数字集成时钟电路设计方案详解

可编程逻辑

描述

在当前的数字集成电路设计中,同步电路占了绝大部分。所谓同步电路,即电路中的所有寄存器由为数不多的几个全局时钟驱动,被相同时钟信号驱动的寄存器共同组成一个时钟域,并可认为同时时钟域内所有寄存器的时钟沿同时到达。

然而,在实际电路中,同时钟域内寄存器时钟沿的到达时间存在偏差,即时钟偏差。通过合理的时钟设计,可以减少这种时钟偏差,使其相对时钟周期可以忽略不计,从而达到同步的效果。

1 ASIC的时钟电路

在ASIC的电路设计中,自动布局布线工具使用动态搭建时钟缓冲器树的方法来解决时钟偏差问题。其基本思想就是控制时钟源与寄存器之间的门延时与线 路延时。如果同时钟域内所有寄存器的时钟端与时钟源之间的路径,包含大体相同的时钟缓冲器个数与连线长度,就可以近似地认为时钟信号从时钟源到各寄存器时 钟端的延时是相等的,因此寄存器间的时钟偏差可以忽略不计。

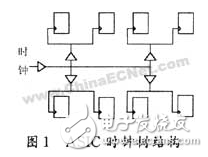

ASIC时钟树结构如图1所示。

2 FPGA的时钟电路

随着FPGA集成度的不断提升,单片FPGA已经可以完成百万门级的集成电路设计。因此,很多ASIC设计可以利用FPGA完成流片前的功能验证。 甚至直接使用FPGA进行商业生产。但是,FPGA的特殊结构决定了基于FPGA的设计不能直接照搬在ASIC设计当中的某些经验,时钟设计便是其中较突 出的一条。ASIC时钟树结构如图1所示。

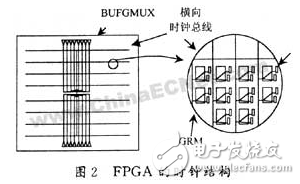

由于FPGA的生产工艺,在出厂之前,FPGA内部元件之间的连线已经完全固定。同时,FPGA具有连线延时相对门延时较大的特点,造成FPGA并 不能通过动态搭建时钟缓冲器树的方法解决时钟偏差问题。实际上,时钟树结构已经被预先固化在芯片当中。针对Xilinx公司的Virtex Ⅱ系列的FPGA。其时钟树结构如图2所示。

该系列FPGA直接利用单独一层铜布线层搭建时钟网络。所有的时钟信号,只能通过处于芯片纵向中轴线上下两端的16个BUFGMUX进入时钟网络。 所有BUFGMUX输出端一直延伸到芯片的中心,连接到铜布线层处于芯片中央纵向分布宽度为8的时钟总线。纵向时钟总线再连接到横向的8条宽度为8的时钟 总线,进而延伸到每一个CLB(Configurable Logic Block,可编程逻辑块)的GRM(General Route Matrix,通用布线矩阵阵列)上。

也就是说,在Virtex Ⅱ结构的FPGA当中,最多可以存在16个时钟域,然而同时只能存在最多8个全局时钟(上下两个对应的BUFGMUX共用一条时钟总线)。由于每个寄存器 的时钟端都通过横向和纵向的时钟总线连接到位于芯片中央的时钟源,而时钟源通过相同路径长度的连线和BUFGMUX连接,因此可以认为从同一 BUFGMUX出发的时钟信号到芯片内所有寄存器的延时相同,从而没有时钟偏差,经过实际工程验证,同BUFGMUX构成的时钟域内时钟偏差最多不超过 0.3ns。

3 设计实例

为了更好的说明FPGA 时钟电路的使用方法与其特殊的问题,下面将用一个在Virtex Ⅱ 6000 FPGA上实现的设计实例具体说明时钟电路建立的方法。

3.1 问题分析

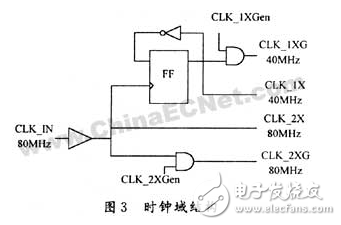

图3显示了在该设计当中的4个时钟域。

这样的时钟结构,在ASIC的时钟树设计中,并不会引发很大的问题。但是在FPGA的设计中,如果不加处理,会引起电路综合、布局布线的巨大压力。其主要的问题源于FPGA综合软件对BUFGMUX的自动指定,造成门控时钟和分频时钟与源时钟之间出现较大的时钟偏差。

一般,综合软件可以通过Verilog HDL的“posedge”和“negedge”关键字,或者VHDL当中的“event”关键字判断出时钟信号。然而,综合工具并没有判断门控时钟与分 频时钟的能力,即就是综合工具认定的时钟只能是一根网线,而不能穿越一般的逻辑门。为了让同时钟域的寄存器间没有时钟偏差。综合工具会自动在时钟的源头为 时钟信号指定BUFGMUX,使得时钟信号使用铜布线资源。

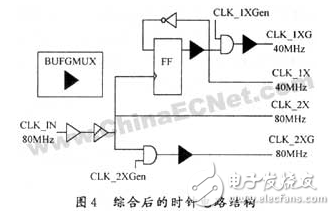

经过综合工具的自动指定,最终会将图3当中时钟结构转换为图4中的电路结构。

正如第2节所述,FPGA通过其特定的时钟网络,使得时钟信号从BUFGMUX到每个CLB的时钟端没有时钟偏差。但是,此结构的间接后果是为每个 CLB的时钟端添加了一个相同的时钟线延时,即从BUFGMUX通过时钟网络到达GRM的时间,在正常情况下,这个时间为6-7ns。

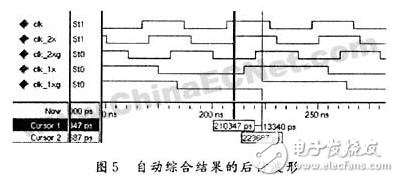

正是由于这一点,在综合工具自动指定BUFGMUX之后,为了实现CLK_2XG这个门控时钟,必须将CLK_2X时钟信号通过与门,再经过 BUFGMUX重新连接到时钟资源。显而易见,CLK_2XG时钟域的时钟信号相对时钟源CLK_IN来说经过了两次BUFGMUX和CLK_2X的时钟 域产生了至少6ns的时钟偏差。同理,CLK_1XG和CLK_1X相应与CLK_2X之间存在12ns和6ns的时钟偏差。相对CLK_2X 80MHz的时钟频率,一周期为12.5ns,显然最大12ns的跨时钟域的时钟偏差是不能忍受的。从图5的后仿波形当中,可以很明显地看到这个时钟偏差 达到了13.34ns。

3.2 解决方案

3.2.1 门控时钟

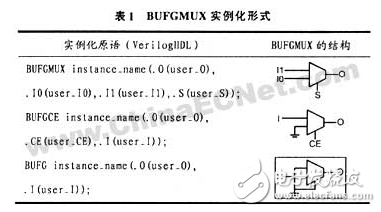

实际上,BUFGMUX并不是简单的时钟缓冲器,他是一个具有低时钟偏差、高驱动能力并带有选择端的双路选择器。使用不同的原语进行实例化,BUFGMUX可以构成时钟选择器、时钟门控器或者简单的时钟缓冲器[1]。

尽管BUFGMUX就3种使用方式,但如果让综合软件自动在合适的位置指定BUFGMUX,由于综合软件只能认出网线形式的时钟信号,因而只会使用BUFG的方式使用BUFGMUX,造成了上述的问题。

为了去除由于门控时钟造成的时钟偏差,只能通过手动更改代码,在合适的位置实例化BUFGMUX。在此例中可以为CLK_2X信号实例化BUFG原 语,而使用BUFGCE原语替代原来的与门,并直接使用CLK_IN为BUGCE的输入。这样CLK_2X和CLK_2XG都只经过了一个 BUFGMUX,因此可以近似地认为不存在时钟偏差。同理CLK_1X和CLK_1XG之间的时钟偏差也可以解决。

3.2.2 分频时钟

然而,BUFGMUX的3种使用方式并不能解决分频寄存器造成的CLK_1X和CLK_2X之间的时钟偏差问题。比较简单的一种方法是使用CLK_IN作为分频寄存器的输入,而不对CLK_2X进行分频。

尽管如此,由于分频寄存器的器件延时和相应的连接线路延时,CLK_2X和CLK_1X之间仍然存在大约2-3ns的时钟偏差,对于某些跨时钟域的 关键路径和时钟保持(Hold Time)约束来说,仍然过大。另外,由于CLK_IN被分频寄存器当作时钟使用,可能会造成综合软件自动给CLK_IN指定BUFG,导致所有时钟信号 都需要经过两个BUFGMUX,产生一个12ns左右的输入延时。

针对这种问题,可以使用FPGA当中的另一个特殊资源——DCM(Digital Clock Manager,数字时钟管理单元)。DCM当中包含一个DLL(Delay-Locked loop,延迟锁定电路),可以提供对时钟信号的二倍频和分频功能,并且能够维持各输出时钟之间的相位关系,即零时钟偏差(更详细的说明可查看参考文献 [1,2]。

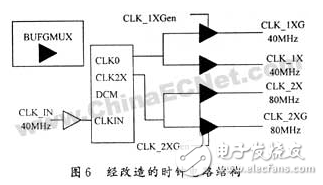

因此,针对分频时钟,可以直接利用DCM的分频功能,从而省去分频寄存器,彻底地解决了CLK_2X和CLK_1X之间的时钟偏差。不过更合适的选择是使用DCM的倍频功能,这样只需要为FPGA准备一个40MHz的低频时钟输入,相对80MHz要更容易实现。

3.2.3 最终实现

通过BUFGMUX和DCM的使用,可以将图4改造为图6所示的电路结构。

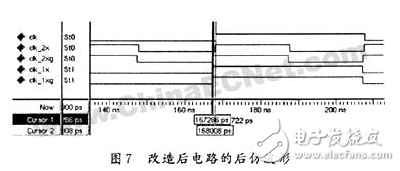

改造后,每个时钟域的时钟信号和信号源CLK_IN之间都只通过一个DCM和一个BUFGMUX,他们之间的时钟偏差仅为时钟网络本身的时钟偏差和 DCM的输出到各BUFGMUX输入端之间的线路延时偏差。如果进一步优化,通过在布局布线的步骤施加对BUFGMUX的位置约束,迫使图5中的4个 BUFGMUX都处于FPGA的上方或者下方的8个BUFGMUX上,跨时钟域的时钟偏差在VIRTEX Ⅱ 6000FPGA当中可以控制在0.5ns以内,基本满足80MHz的要求。改造后的时钟电路的后仿波形如图7所示,其最大的时钟偏差为0.722ns。

实际上,DCM和BUFGMUX从VIRTEX Ⅱ开始,已经成为FPGA的标准元件,可以在SPARTAN-3,VIRTEX Ⅱ,VIRTEX Ⅱ PRO,VIRTEX-4等器件上直接使用,因此该电路结构也可相应推广到这些FPGA的电路设计当中。

4 结语

本文通过比较ASIC时钟树结构和FPGA时钟网络的结构,说明了FPGA时钟网络的自身特点。通过一个设计实例,分析了直接使用综合工具实现多时 钟域的电路设计所存在的问题,并针对这些问题提出了利用BUFGMUX的三种使用方式代替门控时钟与利用DCM代替分频时钟的方法,较好地解决了FPGA 时钟电路的时钟偏差问题,并具有一定的适用性。

-

Verilog HDL数字集成电路设计原理与应用2023-05-26 626

-

数字集成电路设计透视资料下载2021-11-03 1198

-

CMOS数字集成电路是什么?CMOS数字集成电路有什么特点?2021-06-22 5155

-

基于FPGA的调焦电路设计方案资料下载2018-05-07 1320

-

Verilog超详细教程-数字集成电路设计入门2018-03-26 12012

-

数字电路设计方案中DSP与FPGA的比较与选择2017-01-18 1049

-

北大verilog课件从HDL到版图-数字集成电路设计入门2014-08-28 11134

-

数字集成电路设计入门2012-08-20 5343

-

数字集成电路设计流程.ppt——独家资料2011-11-22 13247

-

数字集成电路_什么是数字集成电路2011-10-28 5026

-

数字集成电路设计教学大纲2010-09-20 1228

-

用数字集成电路设计的里程表2009-11-03 2299

-

数字集成电路-电路、系统与设计 免费下载2009-02-12 16970

-

数字集成电路简介2006-04-16 2958

全部0条评论

快来发表一下你的评论吧 !