基于FPGA片上集成的高速FIFO实现缓存以及同步数据传输的应用

可编程逻辑

描述

随着测试环境越来越复杂,需要采集的参数种类越来越多,要求采集系统连续采集各种传感器输出的模拟信号,而目前常用的固态存储器件FLASH的写入速率比较低。本文提出一种基于FPGA(现场可编程门阵列)片上集成的高速FIFO实现采集数据的高速缓存并通过对高速FIFO的读写操作实现总线同步数据传输,提高数据的传输速率。

引言

高速数据采集系统目前已在雷达、声纳、遥测、动态测试等领域得到广泛应用。它的关键技术是高速ADC技术、数据存储与传输技术。目前各种测试环境越来越复杂,需要采集的环境参数及被测体各种动态参数的数目越来越多,多路信号的采集过程是实时的、连续的,因此,需要将待测参数实时、准确地存储下来[1]。此外,由于ADC芯片输出采样数据流的速率很高,需要大容量存储单元对采集数据进行存储。而目前常用的存储介质FLASH 的数据写入速度相对较低。因此,在数据的多通道采集及大容量存储模块之间加入高速缓冲存储器能够解决数据的缓存及速度匹配问题。

1 高速缓存的实现

通常,高速缓存的实现有四种方法[2-3]:

第一种是FIFO(先进先出)方式。FIFO具有两套数据线而无地址线,可在一端进行写操作,另一端进行读操作,数据进行顺序传输,因而能够达到很高的传输速度和效率,且由于省去了地址线而有利于PCB板的布线和硬件电路设计。缺点是只能顺序读写数据,且输入与输出数据总线宽度相等,不能满足采集或存储模块与控制模块数据总线带宽不等的应用场合,两套数据线会占用控制器件大量I/O端口。

第二种是双口RAM方式。双口RAM具有两套独立的数据、地址和控制总线,因而可从两个端口同时读写而互不干扰。双口RAM也能达到很高的传输速度,并且具有随机存取的优点。缺点是采用双口RAM需要占用大量的控制器件的I/O端口,并且高速双口RAM价格昂贵。

第三种是由高速SRAM或DRAM及相应的控制逻辑组成的缓存器。这种缓存器具有数据、地址和控制总线。优点是可随机存取,同时较大容量的SRAM和DRAM容易得到且价格适中,缺点是切换控制电路比较复杂。

第四种是采用VHDL硬件描述语言,充分利用Xilinx公司SpartanⅡ系列FPGA的系统资源,设计实现了一种片上集成的高速同步FIFO,它不仅提供了数据缓冲,而且通过对高速缓存的读写操作能够实现总线接口两端的数据同步传输,提高数据传输效率。

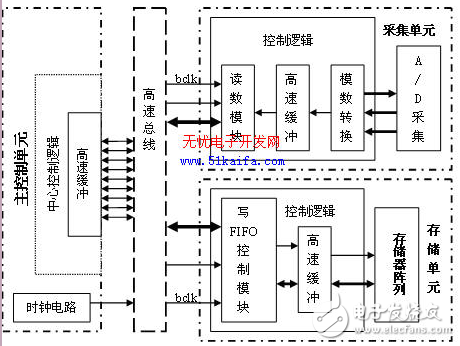

综合考虑以上四种高速缓存的实现方案的性能、成本和实现复杂度,笔者选用第四种方案。系统组成原理框图如图1所示。

图1 采集系统组成原理框图

笔者设计的采集系统能够采集64通道模拟信号,采集数据经过系统内部总线高速背板总线传输到存储器模块。采集单元将转换数据写入高速缓存中,由控制器件将数据以高速速率写入总线。其中ADC是一个8位精度、20MSPS采样速率模数转换器。由于A/D连续采样数据,若控制器件一直处于连续读数状态,这将占用其大部分的处理时间,增加功耗。因此最好的方法是采用高速缓存来存储采样数据,再集中传输一批数据,从而可以成倍提高系统内总线数据流通速率。

系统中采用容量比较大的FPGA,利用VHDL硬件描述语言完成数据的高速读写和对ADC采集模块的控制操作。为保证设计的硬件系统体积尽可能小,因此在不增加系统的硬件负担的前提下,利用FPGA实现片上集成高速同步缓冲存储器。这种实现方法可以使采集系统灵活、简单、方便,具有很强的可扩展性,可根据需要设计为不同数据宽度、不同容量的数字系统,接口电路简洁且不占用系统地址资源,系统移植或升级换代方便,而且控制简单,易于实现。

2 FPGA实现片上集成高速FIFO

2.1 FIFO结构设计

本设计中选用的控制器件FPGA为Xilinx公司Spartan-ⅡE系列XC2S100E,共有10个Block RAM,每个Block RAM的存储容量为4096-bit同步双口RAM[57]。每个端口都有独立的控制信号,并且每个端口的数据总线宽度可以独立配置。Block RAM可以用作FPGA片上和片外缓冲的FIFO,高速并行访问的缓冲存储器和总线宽度转换器等[4]。

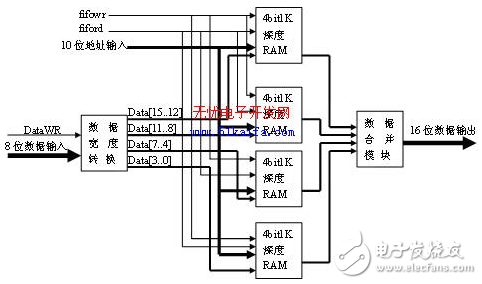

ADC采集单元进入的数据是8位,为了使记录器内数据传输速度加快,背板数据总线宽度为16位。因此设计中采用把4个双口RAM RAMB4_S4_S4并行连接构成16位数据宽度,1K深度的高速FIFO,如图2所示。ADC采集模块通过数据宽度转换模块将8位数据先经过FPGA内部数据宽度转换模块将输入的8位数据组合成16位数据。写入高速FIFO中。由于64路采集卡采样率为20Mbps,而集成FIFO读时钟的频率为30MHz。因此数据写入总线速率能达到60Mbyte/s。集成FIFO容量为16Kbit,每采集10us传感器信号,系统主控模块通过总线请求信号REQ授予该采集卡4us总线使用权,将缓存中的数据写入总线,然后存储到存储器阵列中。能够保证采集数据不会溢出。

图2 FPGA集成1K深度非对成同步FIFO

本设计中用读地址和写地址相减结果来判断FIFO 的存储状态。当读写地址的差值不相同时,说明FIFO内有数据,如果地址差为±1024说明FIFO已写满,如果差值小于±1024说明FIFO未满。当读写地址的差值相同时,说明FIFO内没有数据为空状态。程序如下所示:

offset <= "0000000000" when(f_addrd = f_addwr)

else (f_addwr - f_addrd) when(f_addwr > f_addrd)

else (1023 + f_addwr - f_addrd);

2.2 同步数据传输时序设计

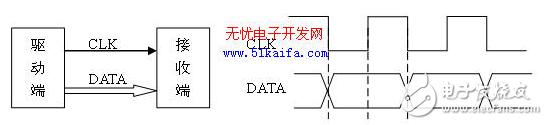

同步数据传输是指时钟选通信号CLK由驱动芯片伴随发送数据一起发送。在同步数据收发中,数据信号同时钟选通信号一起发向接收端。选通信号用于接收端锁存数据信号。如图3所示。

图3 源同步数据传输

与现有技术(常用并行总线传输技术)相比,本设计所采用源同步数据传输方法最大的优点是提高了总线数据传输速度的最大值,放弃了常用并行总线传输时序中由数据接收端发出的控制信号对总线数据传输操作进行同步的方法,而是使得数据同步信号和数据信号由数据源端总线接口同步发出,二者的传输路径、方向、走线长度都基本相同。二者之间的传输时间差异仅为板卡(或芯片)的传输抖动,按照目前器件水平,二者之间的延迟可以控制在1ns量级。基本可以满足这两个信号(数据同步信号和数据信号)同时到达数据接收端板卡接口的要求,实现总线上的高速数据传输。

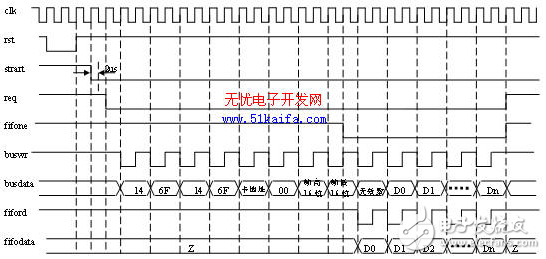

对片上集成高速FIFO的读写操作采取分时进行,当启动采集信号有效时,将采集数据写入高速缓存中,直至停止采集。当总线授予该采集单元使用权后,进行高速缓存的读数操作,将数据写入总线。控制器件对高速FIFO的读控制时序如图4所示。

图4 高速FIFO的读操作时序

当系统主控模块授予该采集单元总线使用权后,即REQ=’0’,由主控模块写入总线标识位146F、146F,写入当前采集单元的16位卡地址和32位帧计数。此时,判断高速缓存FIFO中是否有数据,如果有,进行读数操作;若没有,则等待。当高速缓存FIFO中有数据(fifone=’0’)时,为提高总线写入速度,在写入数据的同时,读出FIFO中的下一个数。因此写入总线第一个数据为无效数据。随后依次写入AD编码数据。当主控模块收回总线使用权,采集单元控制逻辑保证将当前数据正确写入存储器总线接口电路,总线写信号buswr置为弱上拉,数据总线置为高阻态。FIFO数据写入总线部分程序如下所示。

when st15=>

if f_rq='0' then

if offset<5 then

s_state<=st15;

else ----FIFO中数据不空

f_addrb<=f_addrb+1;

f_memwr<='0';

f_fiford<='0';

f_memd<=f_fifod; ----写入数据到总线

s_state<=st16;

end if;

else

s_state<=st17;

end if;

when st16=>

f_memwr<='1';

f_fiford<='1';

s_state<=st15;

3 结论

基于目前采集参数多样化,系统硬件体积小型化的发展趋势,本文针对自己设计的多通道数据采集系统的硬件设计中,提出了利用所选FPGA器件的特点,选择了资源占用最少、效率较高的片上集成高速缓存,解决了高速数据采集通道多、数据量大、实时性高的问题。并且通过对高速FIFO的读写操作实现总线同步数据传输的方法提高数据传输速率。该采集系统已通过项目验收,已实现社会经济效益达100万。并且通过使用泰克示波器TDS3054B测量系统内总线写同步信号频率为30MHz/s,即系统内总线数据传输速率能够达到60MByte/s。

-

基于FPGA的高效内存到串行数据传输模块设计2025-11-12 4116

-

基于 DSP-dMAX 的嵌入式 FIFO 数据传输系统设计2011-07-25 4389

-

基于FPGA的高速LVDS数据传输2014-03-01 6838

-

同步FIFO在大幅面高速彩色喷绘机喷头数据传输中的应用2015-01-28 3725

-

基于FPGA+USB3.0接口的高速数据传输系统设计2018-08-09 15063

-

ROHM高速数据传输方式控制器2018-11-19 1248

-

如何设计嵌入式FIFO数据传输系统?2019-08-08 2104

-

高速缓存/海量缓存的设计实现2020-12-04 1614

-

怎么实现基于FPGA的具有流量控制机制的高速串行数据传输系统设计?2021-05-25 1862

-

基于FPGA和USB的高速数据传输、记录及显示系统2006-04-16 748

-

基于FPDP的高速数据传输系统设计2009-12-01 2393

-

嵌入式 FIFO 数据传输系统设计2011-06-23 1436

-

USB2.0+FPGA实现多路数据传输系统2011-09-13 852

-

SOPC实现的PCI总线高速数据传输系统2012-02-10 1702

-

基于DSP+FPGA+ARM的架构实现高速多路数据传输系统的设计2021-04-24 7093

全部0条评论

快来发表一下你的评论吧 !