关于多电压轨FPGA和DSP应用的电源解决方案全解

可编程逻辑

描述

大多数电子产品都有一个或更多的数字处理系统,比如FPGA或DSP,而这些数字处理系统往往需要多个电压轨供电。对于数字系统的电源问题有多种解决办法。本文提出了多电压轨FPGA和DSP应用的电源解决方案,此处假设输入电源电压大于或等于系统的轨电压(如12、5或3.3V)。

特殊应用的要求

特殊应用要求使用全面DC/DC电源解决方案。大多数的系统设计者都倾向于简单的、低成本的电源解决方案,同时也要考虑被供电的电路类型以及输入电源和每个电压轨上的差异。FPGA和DSP内核以及I/O电压轨已经拥有了切换噪声,主要是由电压轨上数百万的晶体管的切换而产生的。所以,大体上,这些“数字”电压轨可以通过开关电源来供电而不用考虑开关噪声。

相反,音频电路、收发电路、时钟信号、锁相环电路和其他噪声敏感电路的电压轨——术语称“模拟”电压轨——应该经过线性调整器装置或低噪声、固定频率的PWM转换装置后供电。有时模拟电路的卖主特别要求这些电压轨还必须经过滤波环节。另外,噪声敏感电路可能会受到开关切换所产生的噪声的影响,所以,应该采用推荐的开关调整器电路并且保护所用的电感器不受干扰。限制开关频率的范围和/或使所有开关调整器的开关频率同步可能会使滤波环节变得更容易些。一旦某个电路被供电,就必须要考虑输入电源电压和每一能量电压轨上电压之间的差异——每一电压轨转换器的功耗必须在容许范围内。最简单的解决办法是功率分配。

电源分配

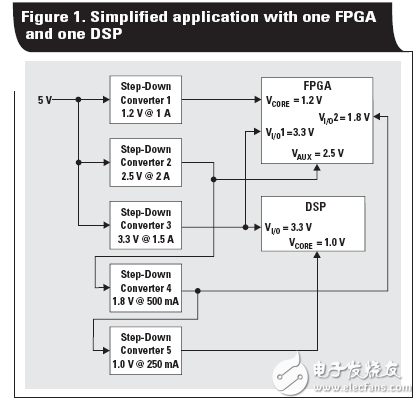

预缩工序节点导致了内核电压轨电压从2.5V降到了1.2V甚至低于1.0V。然而,作为负载点(POL)直流/直流转换器的输入电压(该电压提供内核电压),墙砖电压和许多总线的电压保持在12、5和3.3 V。直流/直流转换器所提供的电压必须要解决功率损耗问题。同时,当单个POL转换器的功率下降时,输入电源的输出能量将会增加。虽然数字IC电路的静态电流在数据表中已经给出,但是预测一个具体的FPGA结构或软件程序的最大电流(有时称为“动态电流”)常常是一件困难的事情。不过幸运的是,所有的FPGA和DSP生产商都提供了在线服务,包括:功率损耗的估计、关键软件的下载、具体应用的设计标准和至少一种最大电流的工作估计。一旦知道每一电压轨的最大电流和功率损耗,我们就可以构造出解决电源问题的方法了。图1所示的结构图就是许多种解决方案中的一种,可以用来解决一块FPGA和一块DSP的应用问题。

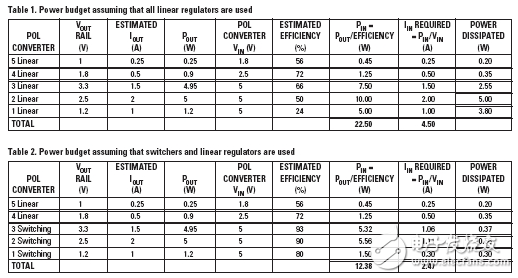

注意为了把5V的输入电源电压牵引到所有的电压轨电压上,设计者使用了FPGA所要求的2.5V电压轨电压作为一个平均总线电压,这样可以更有效提供1.8-V电压轨,然后再应用该1.8V去为1.0V电压轨供电。如果假设所有的POL转换器使用的都是价格便宜的线性调节器,功率分配如表1所示,其中输入电流至少为4.5A。同时,转换器1和2的功率损耗分别为3.8 和5 W,对于没有附加空气流动装置或者外部散热器的表面封装线性调节器是无法达到这样的功率损耗的。

假设转换器1、2和3所使用的是降压开关转换器,则功率分配如图2所示。可见开关调节器消除了相应的功率损耗,并且提高了效率,降低了输入电流,进而允许使用低能量的、较便宜的输入电源墙砖。

优秀的电源设计技术

在设计多电压轨系统时,如果没有考虑到每一个电压轨功率上升时间的话,将会对器件的稳定性造成瞬时或长期的威胁。不正确的电压轨时间可以放大潜在的故障,可能会损害处理器的I/O端口或支撑系统装置(如:存储器、逻辑处理器或数据变换器等)。ESD保护故障和绝缘结构故障将对器件造成长期的危害,而良好的绝缘结构可以使两个电压轨内在的分离。如果一个电压轨正在被使用,而另一个电压轨就会禁止使用一段较长周期——比如一个月——或者叠加更短的周期,这时就可能会对器件产生损害。

闭锁现象可以造成直接的显而易见的损害,或长时期的影响系统可靠性。当电流通过CMOS器件的衬底时,会在反向的寄生双极性晶体管(如SCR)上触发一种自激传导电压轨,这时就会产生闭锁现象。在这个过程中电流将持续的增大直到器件的损坏或电源电压下降。如果一个电源给一个器件供电,则在第二个器件没有被完全供电之前将会产生反向电流流入或流出第二个器件,这时将会产生触发电流。如果在所有器件都供电完毕后,输入端的电压大于或小于电压轨上的电压,系统同样会触发一个闭锁。有记载双向I/O端口也可能是系统产生故障的一个原因。

当处理器和支撑的外围设备(如存储器或数据变换器)不是由同一电源供电时,就可能存在的闭锁现象。而总线冲突一般发生在多个器件在供电过程中同时试图控制双向总线时,进而会影响I/O的可靠性。晶体管在某种未知的状态下将会产生一种从输入电压轨到接地之间的“隐蔽”路径,在类似这种不良条件下数字器件将会产生更大的瞬间起峰电流,进而造成瞬间的损害或长期影响系统的可靠性。最近,FPGA 和DSP制造商及已经改进了保护电路来减少这种闭锁现象、总线冲突和类似的晶体管不良状态。

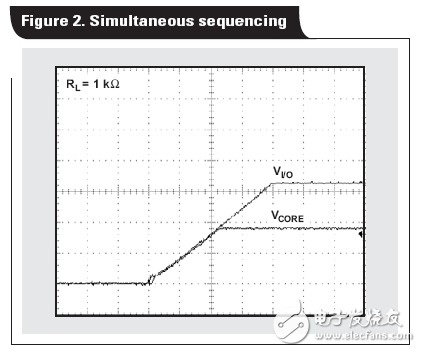

针对上文所述问题,下面列出了一些简而易行的电源设计方案对系统进行进一步的保护。第一,确保所有与处理器I/O总线相连接的逻辑外围设备由同样的电压轨供电,该电压轨同时为处理器的I/O供电。第二,确保每个电压轨的转换器控制在一个指定的误差范围内,该范围包括整体输入电压和瞬时过程中负载的变化范围。该系列文章的第二部分对此做了更详细的介绍。第三,确保所有电压轨的供电电压在相对较短的时间(一般小于等于100 ms)里是单调,或是同时供电,这样启动时电压轨间的意外时间误差将会减到最小。

-

两种能够帮助工程师简化FPGA的电源解决方案2018-03-26 8768

-

用于 Xilinx FPGA Zynq 7 的电源解决方案2015-04-14 3891

-

XilinxVirtex®UltrascaleFPGA多路千兆位收发器MGT电源解决方案2015-05-11 3687

-

用于Xilinx Ultrascale Kintex FPGA多路千兆位收发器(MGT)的电源解决方案2018-08-10 4102

-

如何选择合适的FPGA电源解决方案2018-08-13 3193

-

Xilinx Virtex Ultrascale FPGA MGT电源解决方案包括BOM及原理图2018-08-29 3758

-

Xilinx FPGA Zynq 7全套电源解决方案包括BOM及原理图2018-09-11 4196

-

基于FPGA应用设计优秀电源管理解决方案2019-05-05 2795

-

如何实施单片FPGA电源解决方案?2019-09-17 984

-

为FPGA供电的最佳解决方案2019-12-11 3647

-

关于电源排序的解决方案你了解吗2021-11-24 2955

-

Xilinx Virtex Ultrascale FPGA MGT电源解决方案2022-09-21 1732

-

简化FPGA的电源解决方案2022-11-23 657

-

具有多个电压轨的FPGA和DSP电源设计实例2009-09-25 891

-

双电源电压DSP的电源时序控制解决方案2024-10-11 351

全部0条评论

快来发表一下你的评论吧 !