基于FPGA和高速A/D转换芯片ADC08D1500的相关系统设计

FPGA/ASIC技术

描述

摘要:为同时完成4 个Stokes 矢量参数的相关测量,反演海面风场,提出了新型数字相关器的设计方法。结合高速数字相关器在数字极化辐射计中的应用,介绍了高速数据采样和相关处理系统。通过两片高速A/D 转换器(ADC08D1500)同步采样四路信号,采样结果通过Xilinx 公司新一代现场可编程门阵列(FPGA)-Virtex5 芯片作相关运算,相关结果通过串口上传到计算机,详细介绍了系统各个部分的接口电路和时序控制的设计。系统可以实现四路信号最高1.5GHz 采样率的相关计算。

0 引言

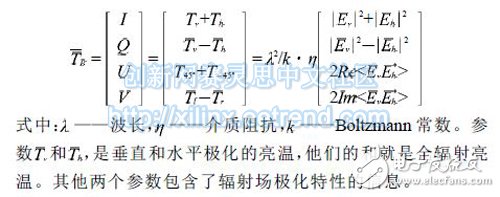

海洋表面风场的研究在气象学、海洋学、气候学中有着极其重要的意义。全极化辐射计的新技术特点是,同时使用多路相关技术,对水平和垂直极化信号进行相关处理,产生反演海面风场模型所需的参量。修正的Stokes 矢量可以用来描述空间中辐射场的二阶统计特性。修正的Stokes 矢量中的元素以亮温K 作为单位,如下式所示。

通过垂直和水平极化两路信号的相关运算可以得到4 个Stokes 参数。目前应用的极化辐射计,大多用模拟相关器。但是随着对风场测量精度的要求越来越高,模拟乘法器件已经满足不了要求。数字极化辐射计是指利用数字相关器来实现两个极化通道的自相关和互相关处理。数字相关器与模拟相关器相比,主要特点是能够用资源换速度,利用超大规模集成电路技术实现全并行宽带数字相关处理。数字相关器对模拟信号进行采样,然后量化的数据作相关运算。根据乃奎斯特采样定律,采样频率必须大于等于两倍被采样信号带宽,才能避免信息的损失。这就使得采样电路工作在很高的频率上,对电路的精度和可靠性提出了很高的要求。本文介绍了一种高频高可靠性的信号采样和相关处理系统。本系统中高速ADC 采用NS公司的ADC08D1500,它具有高精度和低功耗等优点,可以工作在最高采样率1.5GHz。FPGA 芯片具有体积小,集成度高,功耗低等特点。数据接收和相关计算以FPGA为核心完成。

1 数字相关器设计方案

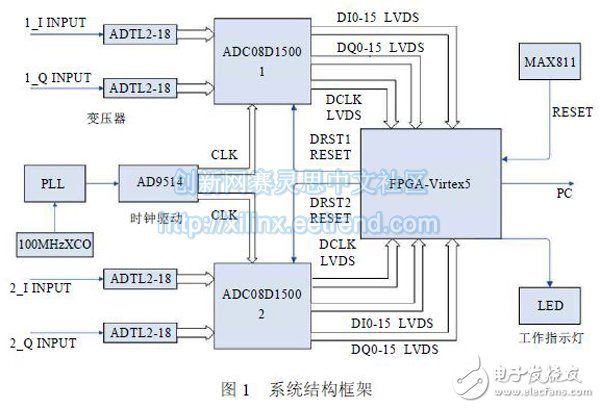

信号采集模块中,两片ADC08D1500 同时完成四路信号的采样。ADC 输出数据为LVDS 模式,单个ADC 位宽32bit,采用并行输出。采用Xilinx 公司FPGA-Virtex5 实现对2 个ADC输出数据的接收和相关运算处理。FPGA还要实现对两个ADC的复位控制,同步复位可以触发两个ADC 同步工作。本方案设计中采用高速时钟驱动器AD9514 对采样时钟进行驱动,确保到达两路ADC 的采样时钟信号的相位一致性。FPGA 计算的相关结果通过串口上传到PC 机。系统框图如图1 所示。

2 ADC 及外围电路

2.1 ADC

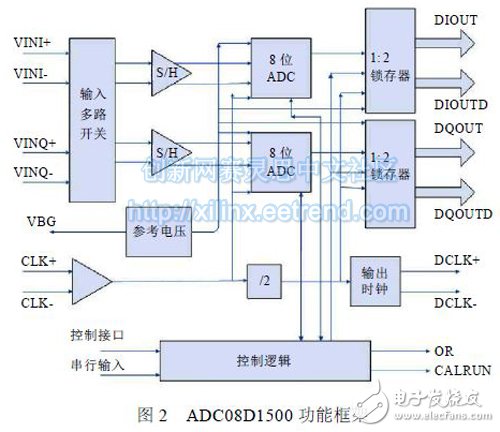

ADC 采用两片ADC08D1500 芯片。美国国家半导体公司的高速ADC-ADC08D1500 [3] 是一款高性能的模/数转换芯片,典型功耗1.9W。本数字相关器中,每个通道采样率1.5GHz,8bit 分辨率,全功率带宽1.7GHz。通过管脚配置设定输入峰峰值为870Mv。ADC上电231 个采样时钟周期以后自动校准。

DCLK 送给外部器件来锁存数据。DCLK 工作在DDR 传输模式。ADC 内部做1:2demux,输出时钟为采样时钟的二分频。这种方式降低进入FPGA 的时钟速率为采样频率的1/4,为高速相关计算提供方便。OR 管脚为高电平,指示输入超出量程。将OR 连接到FPGA 并驱动FPGA 的外接LED。图2 为ADC 功能框图。

2.2 时钟控制

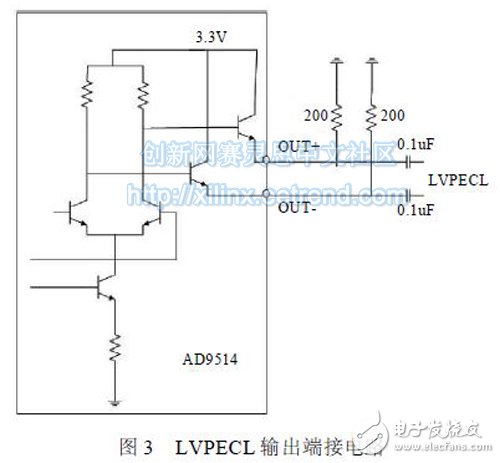

ADC08D1500 需要一个差分时钟输入。两个ADC 的采样时钟需要严格同步,以达到其幅相一致性的要求。设计中时钟通过时钟驱动AD9514 分出两路同相差分时钟。ADI 公司的高性能时钟驱动芯片AD9514 输入电平为LVPECL、LVDS,输出信号为LVPECL、LVDS、CMOS 电平。采用两路LVPECL电平输出交流耦合到两片ADC,最高输出1.6GHz 频率,如图3 所示为其LVPECL 输出端电路。

2.3 ADC 复位

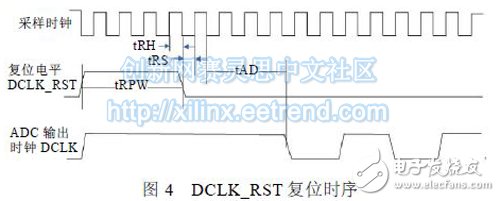

两个ADC的同步复位是保证ADC同步工作的主要方法。DCLK_RST 是ADC 的复位管脚。一个正脉冲可以复位和同步多片ADC 的DCLK 输出。复位信号必须持续4 个采样时钟周期以上复位才有效。如图4 所示,trpw 至少为4 个采样时钟周期。由FPGA 控制DCLK_RST 管脚实现对两片ADC 的同时复位。恢复时间Tad 为3.5ns。

2.4 ADC 与FPGA 接口电路PCB 设计

FPGA-Virtex5 是Xilinx 推出的第五代产品,IO 口可以接收高达1.25GHz 的LVDS 输入。每片ADC 输出的采样信号,同步时钟DCLK 和采样溢出信号OR 都是LVDS 电平传输。LVDS 的驱动器由电流源组成,电流通常为3.5mA。当驱动器翻转时,改变了流经端接电阻的电流方向,因此产生有效的逻辑1 和逻辑0 状态。LVDS 具有超高速、低噪声和超低功耗的优点。同时LVDS 在走线的布局的时候需要注意到以下几点。

(1)尽量保持LVDS 线的等长和平行,本设计采用4mils 宽和间距的走线,增强了接收器的共模抑制能力。

(2)高速信号线在满足条件的情况下,加入端接匹配以减少或消除反射,减小串扰。

(3) 对于微带线和带状线传输,走线高度在高于平面层10mil 以内。

(4)多层走线相邻两层线条尽量相互垂直,或走斜线,大面积的电源层和大面积的地层要相近,电源和地之间形成电容,起到滤波作用。

(5)确保每一个信号层相邻一个平面层。传输线将临近的参考平面层作为传输线的第二导体或者叫做信号的返回通道。确保传输线的特征阻抗一致。如果信号传输特征阻抗一致信号可以平稳的向前传播,如果阻抗发生变化,信号中的一部分就会往回反射,信号传输连续性受到破坏。

3 FPGA 设计

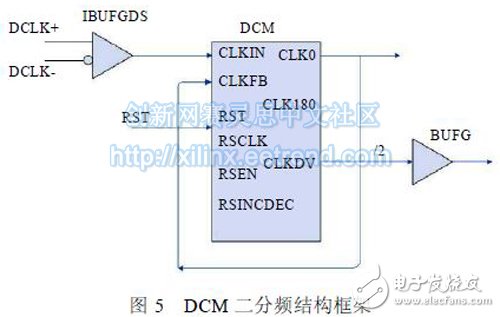

Virtex-5 采用65nm 工艺,与前一代90nmFPGA 相比,速度提高30%,逻辑容量增加65%。同时动态功耗降低了35%。数据以750MHz 的速率进入FPGA,时钟速率是375MHz。为降低数据运算的速度使得FPGA 工作更加稳定,输入的LVDS采样信号和差分时钟首先通过bufer 转化成单端信号,随后进入多路复用模块。将采样数据做1:2 的demux,即积累两个时间点的采样值再输出到下一个单元。同时需要将输入的控制时钟做二分频。分频的工作由Virtex5 中的DCM 时钟驱动模块完成。通过DCM 模块不仅能对时钟进行同步、移相、分频和倍频等变换,而且可以使全局时钟的输出达到无抖动延迟。FPGA 中高精度相位和频率调节主要是采用IBUFG+DCM+BUFG 来实现[7]。IBUFG 和BUFG 都是FPGA 里全局时钟BUFFER。图5 为DCM 产生二分频的结构简图,RST 是DCM 的复位信号,至少3 个输入时钟周期的高电平可以复位DCM。在程序配置以后,设计FPGA 自动触发一次RST 信号,随后将置于低电平。

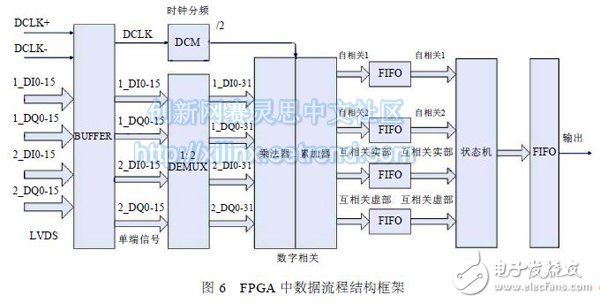

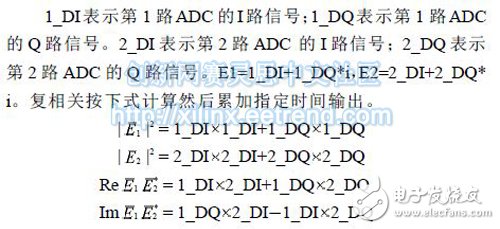

经过demux 后的采样值在分频后的时钟驱动下进入乘法器和累加器模块。用FPGA 里的IP 模块设计8bit 宽乘法器,当使用-3 级别的Virtex5 芯片时其计算速度最高达到550MHz。通过VHDL编程实现48bit宽累加器。通过IP核设计8bit 1024同步FIFO。如图6 为FPGA 中数据流程结构框图。

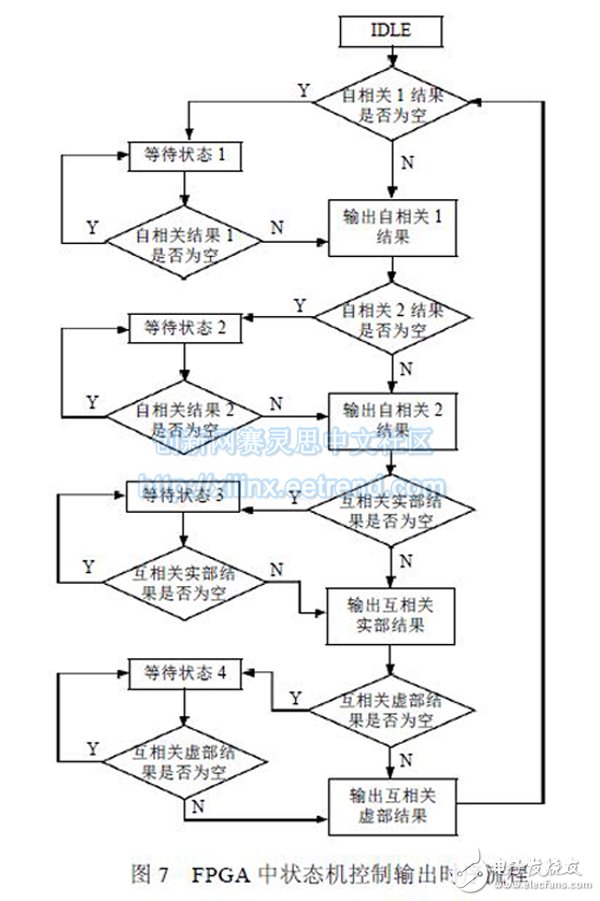

数据累加10ms (可控制) 通过串口输出到PC 机。相关结果按照自相关1,自相关2,互相关实部,互相关虚部顺序输出。通过状态机编程控制端口输出顺序。图7 为FPGA 中状态机控制输出时序流程图。

4 结束语

本文详细介绍了基于高端FPGA-Virtex5 和高速A/D转换芯片ADC08D1500 的相关系统设计。和模拟相关器相比,数字相关器没有通道互藕,一致性较好。提出的新型数字相关器可以同时完成4 个Stokes 参数高精度测量,采样量化精度8bits。同时此相关系统速度达到1.5GHz,可以满足1.5.GHz 宽带IQ 信号的相关处理。系统还具有体积小,使用灵活和功耗低等特点。整体功耗在15W 以内。基于高速ADC 和FPGAVirtex5的数字相关器设计方案还可以进一步拓展带宽。随着高速ADC 和FPGA 芯片的发展,带宽更高的数字相关器可以参考本设计方案,采用相同的结构和FPGA 数据处理方法。

- 相关推荐

- 热点推荐

- FPGA

- adc08d1500

-

高速低功耗利器:ADC08D1500 ADC深度解析2025-11-30 462

-

ADC08B200:高速8位A/D转换器的全方位解析2025-11-28 314

-

ADC08D1020:高性能8位A/D转换器的深度解析2025-11-27 397

-

ADC08D1500双通道、低功耗、高性能CMOS模数转换器数据表2024-07-17 403

-

ADC08D1500高性能CMOS模数转换器规格书2023-07-05 436

-

求一种基于高速转换芯片ADC08D1000的采集系统的设计和实现2021-04-23 1601

-

分享一款不错的基于ADC08D1500和FPGA Vertex-5的采集系统设计方案2021-04-08 1297

-

模数转换器ADC08D1500的性能特点及应用分析2020-12-28 3364

-

一种高频高可靠性的信号采样和相关处理系统2017-11-22 3237

-

A/D转换芯片ADC08D1000特性介绍2011-05-05 9123

-

高速信号采集与数据形成系统硬件设计2009-12-19 767

-

ADC08D1500,pdf datasheet (High2009-10-10 769

-

超高速转换器ADC08xxxx系列的校准2008-08-15 1731

全部0条评论

快来发表一下你的评论吧 !