基于FPGA的电子琴设计与实现

FPGA外设/外围电路

描述

电子琴设计原理

乐曲都是由一连串的音符组成,按照乐曲的乐谱依次输出这些音符所对应的频率,就可以在扬声器上连续地发出各个音符的音调。为了准确地演奏出一首乐曲,仅仅让扬声器能够发出声音是远远不够的,还必须准确地控制乐曲的节奏,即每个音符的持续时间。由此可见,乐曲中每个音符的发音频率以及音符持续的时间是乐曲能够连续演奏的两个关键因素。

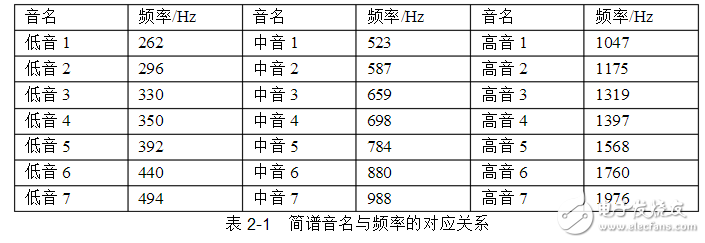

乐曲的12平均率规定:每2个八度音之间的频率要相差1倍,比如简谱中的中音2与高音2。在2个八度音之间,又可分为12个半音。另外,音符A(简谱中的低音5)的频率为392Hz,音符E到F之间、B到C之间为半音,其余为全音。由此可以计算出简谱中从低音

1至高音1之间每个音符的频率。简谱音名与频率对应关系如图2-1所示:

产生各音符所需的频率使用一分频器来实现,由于各音符对应的频率多为非整数,而分频系数又不能为小数,所以必须将计算得到的分频数四舍五入取整数。若分频器时钟频率过低,则由于分频系数过小,四舍五入取整数后的误差较大;若时钟频率过高,虽然误差变小,但分频数将会变大。在实际的设计中应综合考虑这两方面的因素,在尽量减小频率误差的前提下取合适的时钟频率。实际上,只要各个音符间的相对频率关系不变,演奏出的乐曲听起来都不会走调。

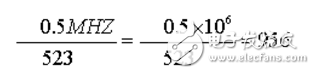

设计的音乐电子琴选取12MHZ的系统时钟频率。在数控分频器模块,首先对时钟频率进行12分频,得到1MHZ的输入频率,然后再次分频得到各音符的频率。由于数控分频器输出的波形是脉宽极窄的脉冲波,为了更好的驱动扬声器发声,在到达扬声器之前需要均衡占空比,从而生成各音符对应频率的对称方波输出。这个过程实际上进行了一次二分频,频率变为原来的二分之一即0.5MHZ。

因此,分频系数的计算可以按照下面的方法进行。以中音1为例,对应的频率值为523Hz,它的分频系数应该为:

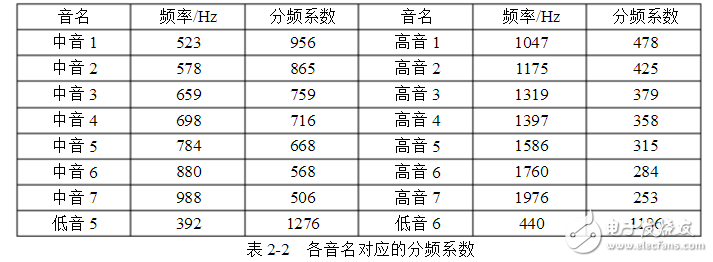

至于其他音符,可由上式求出对应的分频系数,这样利用程序可以很轻松地得到相应的乐声。

各音名对应的分频系数如图2-2所示:

音符的持续时间须根据乐曲的速度及每个音符的节拍数来确定。因此,要控制音符的音长,就必须知道乐曲的速度和每个音符所对应的节拍数。如果将全音符的持续时间设为1s的话,那么一拍所应该持续的时间为0.25秒,则只需要提供一个4HZ的时钟频率即可产生四分音符的时长。

至于音长的控制,在自动演奏模块,每个乐曲的音符是按地址存放的,播放乐曲时按4HZ的时钟频率依次读取简谱,每个音符持续时间为0.25秒。如果乐谱中某个音符为三拍音长,那又该如何控制呢?其实只要在3个连续地址存放该音符,这时就会发三个0.25秒的音长,即持续了三拍的时间,通过这样一个简单的操作就可以控制音长了。

2.2.1分频模块设计方法

方法一:使用加法计数器。在计数器值小于分频系数值时,保持分频的时钟信号不变,当计数器加到分频系数值时,令分频时钟信号发生跳变,同时将零设为此时的计数器值,这样分频时钟信号就会再次发生跳变。但是这种占空比不等于50%的信号是无法驱动实验板上的扬声器发声的。

方法二:使用减法计数器,计数器的数值由分频系数值向下递减,在减为零时跳变并重新赋值,原理与第一种类似。

方法三:先对时钟脉冲进行分频得到1MHZ的脉冲,然后按照输入的分频系数对1MHZ的再次分频,得到所需的音符频率,最后在音调输出时再进行二分频,将脉冲展开能够直接得到占空比为50%的分频信号,将脉冲展宽,使扬声器有足够发生功率。在思索一番后,最终确定了这一个方案,相比较与以上两种实现方法,这种方法的好处在于能够直接得到占空比为50%的分频信号。

按键模块设计方法

按键模块在这个系统中的作用是每按下实验板上的一个键,该模块要相应的输出一个分频系数,用程序将该分频系数送到分频模块后将会产生一个特定频率的信号,传送到实验板上的扬声器里,并发出不同频率的声音即音符。由于每输入一个信号,就产生一个特定的输出信号,且每种情况均能罗列,再加上情况总数(电子琴音调个数)不是很大,故我们使case语句来实现。

2.2.3 顶层模块设计方法 顶层模块的设计就是要设计一个顶层模块将各模块进行例化连接,再组成一个协同发挥功能的的整体。我们注意到,分频模块需要一个分频系数,而键入模块将会产生一个分频系数,因此分频系数在整个系统中将既不输入也不输出,在例化时,我们使用一个信号与之相连,这样它就能在模块间传递。

2.3系统设计的主要组成部分

本设计采用 VHDL语言编程设计实现,音频发生部分、键输入部分和数码显示部分以外,其余全部在一片FPGA芯片上实现。其系统结构如下图2.3所示:

硬件系统主要由FPGA模块,显示模块,按键模块以及扬声器电路组成。系统结构精简、可靠,而且灵活性高。

硬件设计

3.1 Cyclone II芯片简介 在Cyclone I器件系列非常成功的基础上,Altera公司的Cyclone II系列扩大了FPGA的密度,最多可以达到68416个逻辑单元,并且还提供了622个可用的输入/输出引脚和1.1M比特的嵌入式寄存器。Cyclone II器件的制造基于300mm晶圆,采用台积电90nm、低K值电介质工艺,这种工艺技术采用了低绝缘体过程,确保了快速性、有效性和低成本。Cyclone II器件通过使硅片的面积最小化,所以可以在单芯片上支持复杂的数字系统,而且在成本上还可以和ASIC进行竞争。Altera 最新一代低价位的FPGA——cyclone II FPGA系列,和同类90nmFPGA器件相比,它提高了百分之六十的性能和降低了一半的功耗。它的低成本和优化特征使Cyclone II 系列为各种各样的汽车、消费、通讯、视频处理、测试以及测量、和其他最终市场提供了理想的解决方案。 Cyclone II设备系列拥有以下的特点:

4608到68416 LEs 的高密度的结构;

嵌入式乘法器;

先进的I/O口支持;

灵活的时钟管理电路;

设备的配置;

3.2按键模块及其功能‘ 独立式键盘输入电路的VHDL程序设计主要包括:键盘去抖电路、输入信息译码电路和LED显示被按下等电路组成,其中重点为输入信息译码电路的设计。如图所示独立式键盘电路接口信息为独立的译码电路,译码时只对单键输入进行,该系统中用到了16个独立键。如图3-1所示是独立式键盘电路图:

3.3显示电路模块功能

显示模块主要是由1块74LS48译码芯片和1个共阴极七段LED显示器及1个发光二极管组成,由七段LED显示测量的频率值,发光二极管显示高音的音符。74LS48是输出高电平有效的中规模集成BCD七段显示译码驱动器,74LS48的输入端是四位二进制信号(8421BCD码),a、b、c、d、e、f、g是七段译码器的输出驱动信号,高电平有效。可直接驱动共阴极七段数码管,使能端全部悬空。74LS48简图3-2:

软件设计

4.1系统的流程

本设计采用Altera公司的EDA软件系统EP2C8Q208C8来完成。采用自顶向下的设计方法。图4-1为其软件流程图:

软件设计采用结构化程序设计方法,功能模块各自独立,实际上在设计中将键盘输入和乐曲存储放在了一个自动演奏模块中,软件设计的核心部分是数控分频器,键盘输入和乐曲储存都是提供给它相应的分频比。对输入的基准时钟进行多次分频,最终输出的就是想得到的音阶的频率。

4.2 设计模块

本系统主要由三个功能模块组成:music.vhd、tone.vhd和speaker.vhd。系统顶层设计原理图如图4-2所示,该系统有4个输入,3个输出端口。其原理图。

-

电子琴的设计与实现2022-05-31 1107

-

基于FPGA的电子琴设计 毕业论文分享2022-04-29 994

-

基于FPGA的简易电子琴的实现2021-04-28 1424

-

使用FPGA实现电子琴设计的程序与仿真资料免费下载2021-01-18 1178

-

使用FPGA实现电子琴设计的论文2020-07-24 1190

-

使用FPGA设计电子琴的资料合集免费下载2020-05-29 1182

-

FPGA DIY开发板控制电子琴2018-06-20 4280

-

简易电子琴设计及FPGA功能验证2016-02-16 763

-

基于FPGA的PS2键盘鼠标控制电子琴2015-10-29 1370

-

基于FPGA的电子琴设计2013-05-19 5205

-

基于FPGA和超声波的虚拟电子琴设计2012-10-26 876

-

电子琴设计2010-08-19 1475

全部0条评论

快来发表一下你的评论吧 !