基于FPGA的ADC0809控制电路

FPGA/ASIC技术

描述

摘要

本作品是基于FPGA的ADC0809采集控制电路。ADC0809是美国国家半导体公司生产的CMOS工艺8通道,8位逐次逼近式A/D模数转换器。其内部有一个8通道多路开关,它可以根据地址码锁存译码后的信号,只选通8路模拟输入信号中的一个进行A/D转换。

Abstract

This work is ADC0809 sampling control circuit based on FPGA. ADC0809 is produced national semiconductor CMOS 8 channel, eight successive approximation A/D analog-to-digital converter. Its internal have A 8 channel multiplex switch, it can according to the address latch signal after decoding, only gate 8 analog input signals of an A/D conversion.

1. 设计任务

基于FPGA的ADC0809控制电路设计,并阐明其控制原理。

2. ADC0809简介

2.1. ADC0809主要特性

①8路8位A/D转换器,即分辨率8位。

②具有转换起停控制端。

③转换时间为100μs

④单个+5V电源供电

⑤模拟输入电压范围0~+5V,不需零点和满刻度校准。

⑥工作温度范围为-40~+85摄氏度

⑦低功耗,约15mW

2.2. ADC0809外部特性(引脚功能)

①ADC0809芯片有28条引脚,下面说明各引脚功能。

②IN0~IN7:8路模拟量输入端。

③D0~D7:8位数字量输出端。

④ADDA、ADDB、ADDC:3位地址输入线,用于选通8路模拟输入中的一路

⑤ALE:地址锁存允许信号,输入,高电平有效。

⑥START: A/D转换启动信号,输入,高电平有效。

⑦EOC: A/D转换结束信号,输出,当A/D转换结束时,此端输出一个高电平(转换期间一直为低电平)。

⑧OE:数据输出允许信号,输入,高电平有效。当A/D转换结束时,此端输入一个高电平,才能打开输出三态门,输出数字量。

⑨CLK:时钟脉冲输入端。要求时钟频率不高于640KHZ。

⑩REF(+)、REF(-):基准电压。

①①Vcc:电源,单一+5V。

①②GND:地。

2.3. ADC0809工作原理

首先输入3位地址,并使ALE=1,将地址存入地址锁存器中。此地址经译码选通8路模拟输入之一到比较器。START上升沿将逐次逼近寄存器复位。下降沿启动 A/D转换,之后EOC输出信号变低,指示转换正在进行。直到A/D转换完成,EOC变为高电平,指示A/D转换结束,结果数据已存入锁存器,这个信号可用作中断申请。当OE输入高电平 时,输出三态门打开,转换结果的数字量输出到数据总线上。

3. 理论分析与计算

3.1. 系统设计原理

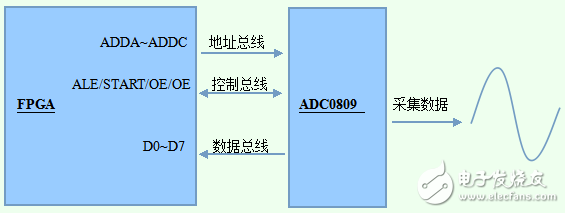

图3-1:系统设计原理图

工作原理:FPGA通过控制总线输入采集端口地址,此地址经ADC0809译码后选通8路模拟采集输入口之一。FPGA输出控制信号使AD的START脚信号出现高电平,上升沿将逐次逼近寄存器复位,下降沿启动 A/D转换。启动转换之后ADC0809的EOC脚输出信号变低,指示FPGA AD转换工作正在进行。直到A/D转换完成,EOC脚变为高电平,指示A/D转换结束,结果数据已存入锁存器。当FPGA检测到EOC脚变为高电平时,控制ADC0809的OE脚变为高电平,输出三态门打开,转换结果的数字量输出到数据总线上,再由FPGA存储起来。

3.2. AD计算分析

①转换量程:0~5V

②分辨率:参考电压为0-5V的话,ADC0809为8位AD,则每一位的电压值为(5-0)/255≈0.0196V

③转换时间: 取决于芯片时钟频率,本作品提供给AD的时钟频率为500KHZ,按官方资料知道AD转换时间为100μs(时钟为640KHz时),按此比例算出时钟为500KHz时的转换时间为130μs;

④采集最高频率:按130us转换时间来算,依据实际经验,在一个信号周期内采集6~7个点能使信号较好恢复原状,则能采集的最高频率大约为1Khz。

4. ADC0809硬件电路设计

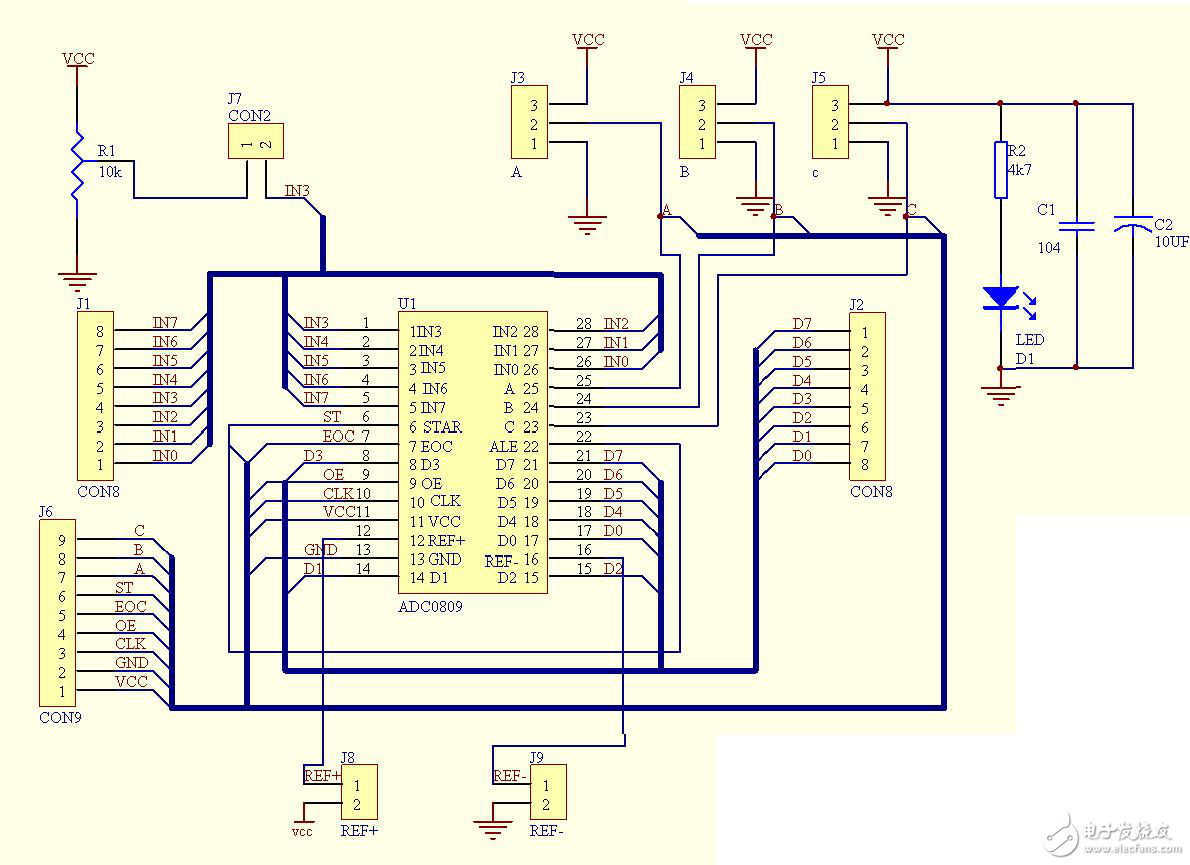

图4-1:ADC0809硬件电路图

注意事项:

①电阻R2用于限流,发光二级管D1用于指示电源是否接通

②电容C1、C2用于滤波

③滑动变阻器R1接AD采集输入口IN3主要用于测试精确AD是否正常工作

④排针用于连接FPGA和方便调试

⑤AD信号线与FPGA接口直接相连

⑥AD的工作频率由FPGA分频直接提供

5. 软件设计

5.1. 程序流程图

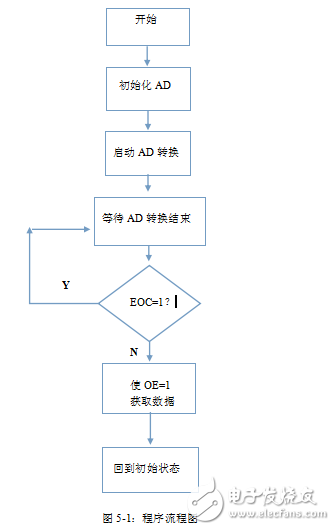

图5-1:程序流程图

确认AD转换完成有三种办法,分别是定时传送办法、查询方式、中断方式。本作品采用查询方式,即查询EOC的状态,即可确认转换是否完成,并接着进行数据传送。

附录:verilog程序

/*FPGA实现的程序:(verilog)

module AD0809(clk, //脉宽(至少100ns)

rst_n,

EOC, //约100us后EOC变为高电平转换结束

START, //启动信号,上升沿有效(至少100ns)

OE, //高电平打开三态缓冲器输出转换数据

ALE, //高电平有效,选择信道口

ADDA, //因为ADDB,ADDC都接地了,这里只有ADDA为变量

DATA, //转换数据

Clk500k,

DATA_R);

output START,OE,ALE,ADDA,clk500K;

input EOC,clk500K,rst_n;

input[7:0] DATA;

output[7:0] DATA_R;

reg START,OE,ALE,ADDA,clk500K;

reg[7:0] DATA_R;

reg[4:0] CS,NS;

Reg[5:0] counter;

/**********************产生AD时钟500Khz***********************************/

always @(posedge clk)

begin

if(counter==6‘b11_0010)

begin

Clk500K《=~clk500k;//1000HZ

counter《=6’b0;

end

else

counter《=counter+1‘b1;

End

/****************************编码*******************************************/

parameter IDLE=5’b00001,START_H=5‘b00010,START_L=5’b00100,CHECK_END=5‘b01000,GET_DATA=5’b10000;

/**********************利用有限状态机设计AD工作流程************************/

always @(posedge clk500K)

case(CS)

IDLE:

NS=START_H;

START_H:

NS=START_L;

START_L:

NS=CHECK_END;

CHECK_END:

if(EOC)

NS=GET_DATA;

else

NS=CHECK_END;

GET_DATA:

NS=IDLE;

default:

NS=IDLE;

endcase

always @(posedge clk500K)

if(!rst_n)

CS《=IDLE;

else

CS《=NS;

always @(posedge clk500K)

case(NS)

IDLE: //停止转换状态

begin

OE《=0;

START《=0;

ALE《=0;ADDA《=1;

end

START_H:

begin

OE《=0;

START《=1; //产生启动信号

ALE《=1;

ADDA《=1;//选择信道口IN0

end

START_L:

begin

OE《=0;

START《=0;

ALE《=1;//启动信号脉宽要足够长,在启动的时候ALE要一直有效

end

CHECK_END:

begin

OE《=0;

START《=0;

ALE《=0;

end

GET_DATA:

begin

OE《=1; //高电平打开三态缓冲器输出转换数据

DATA_R《=DATA;//提取转换数据

START《=0;

ALE《=0;

end

default:

begin

OE《=0;

START《=0;

ALE《=0;

ADDA《=0;

end

endcase

endmodule

-

adc0809是几位转换器 adc0809工作原理简述2024-10-21 3620

-

ADC0809资料2022-06-28 1093

-

ADC0809是什么?ADC0809是如何工作的2022-01-25 8398

-

怎样去使用ADC08092021-11-17 3083

-

ADC0809的使用2021-11-10 1980

-

利用FPGA控制ADC0809采样电压2021-09-28 1481

-

用状态机设计A_D转换器ADC0809的采样控制电路实验2021-09-16 1046

-

ADC0809驱动FPGA实现的verilog程序2021-08-31 1329

-

使用FPGA实现ADC0809的VHDL控制程序免费下载2021-01-18 940

-

adc0809中文资料下载 adc0809引脚图封装及应用电路2016-09-23 21348

-

ADC0809与MCS-51的连接电路2010-02-23 3888

-

ADC0809接口电路2009-01-14 5426

-

ADC0809 VHDL控制程序2008-06-27 3030

-

adc0809外围电路2007-12-25 4248

全部0条评论

快来发表一下你的评论吧 !