cdc路径方案帮您解决跨时钟域难题

描述

Hi,根据之前大家的反馈,这一章就来简单介绍一下CDC也就是跨时钟域可能存在的一些问题以及基本的跨时钟域处理方法。

跨时钟域的问题主要存在于异步时钟信号之间。首先同步时钟和异步时钟的主要区别在于同步时钟是同源的,有一个确定的相位关系,在综合约束的保证下同步时钟路径可以尽可能的去满足setup/hold的要求。同步时钟在CDC中属于同一个时钟域。

而异步时钟来自不同的晶振源,他们之间没有一个确定的相位关系,也就是说如果一个条路径的起点和终点寄存器由异步时钟驱动,没有任何办法来保证信号在何时会到达终点寄存器,这样可能引发一系列的问题,比如亚稳态。我们知道对于同步时钟信号,在综合工具以及后端工具中有时钟约束,可以解决同步时钟路径的setup/hold,而对于异步信号,在综合以及后端中都设为false path,也就是说没有办法从工具的角度进行解决。在这种情况下,就需要从设计层面来解决这个问题,避免这些路径的违例对电路功能造成影响。

Synopsys提供的Spyglass工具可以用于检测系统中存在的CDC路径,并且分析其可能产生的问题,在综合之前进行CDC的检测以及相关设计的修改,可以最大程度地避免这些问题。下面我们来看下几种CDC可能造成的问题以及相应的检测和简单的解决方案。

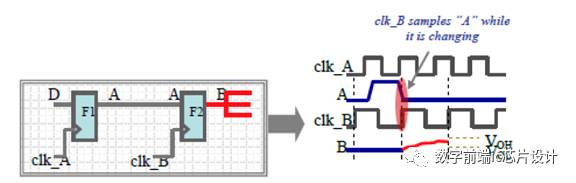

1.metastability

亚稳态是跨时钟域中最主要的一个问题,因为在一条时钟路径中我们无法预知信号会在何时到达终点寄存器,那么有可能信号就会造成setup/hold的违例

上图所示的例子是一个很典型的metastability 问题。由于A信号在F2寄存器的setup违例,造成的亚稳态会在F2的下接负载中进行传播。

对于亚稳态问题,针对具体信号的功能,一般有不同的处理。

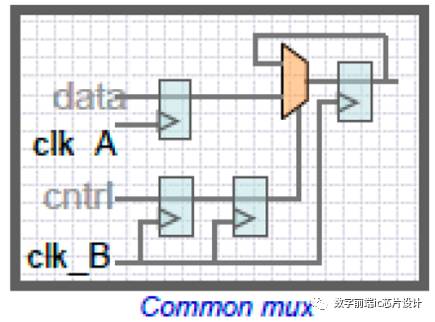

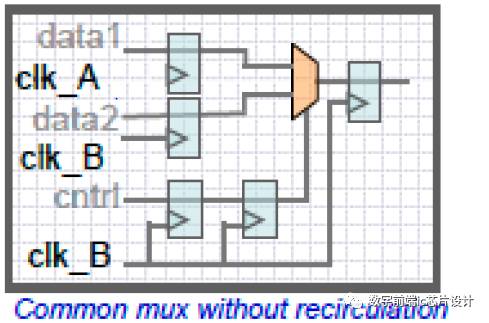

对于多bit的data信号,我们可以使用使能技术,也就是通过一个使能信号来判断data信号是否已经稳定,当使能信号有效的时候说明data处于稳定状态,在这种情况下终点寄存器才对信号进行采样,可以保证没有setup/hold违例。而使能信号一般使用double FF的方法来进行同步。下面是一些简单的data同步电路的例子:

在该电路中Cntrl信号通过两级寄存器同步,通过mux来控制data的采样,注意到这里使用的是recirculate的mux

当然也可以不适用recirculate的mux,mux的另一个输入同样来自终点时钟域。

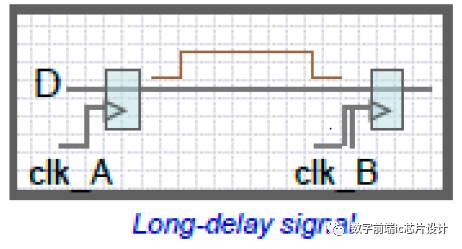

此外还可以通过long-delay,也就是给信号长的延时来保证信号能在指定的时间到达。

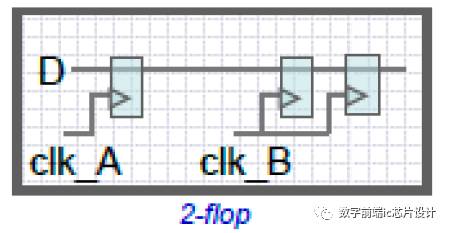

如果是控制信号,我们可以直接使用double FF的方法,也就是多级寄存器同步的方法来进行同步。这是因为控制信号位数较少,不需要额外使用使能信号资源。

上图是个最基本的两级flop的同步器,原理很简单,我们默认亚稳态会在一个时钟周期之内解决,因此从第一级flop输入的亚稳态到第二级flop就稳定了。因为这是一个1-bit的信号,所以如果第一个时钟亚稳态稳定的值不是我们预估的值,比如1->0的跳变,亚稳态最后结果是1,那么0的稳定值也会在下一个周期到达第二级flop。

以上是一些最基本的信号同步器,根据具体design的不同,可以设置不同的同步逻辑,但同步逻辑的基本思路都类似,通过控制信号来保证来自时钟源A的信号在稳定的情况下才被来自时钟源B的终点寄存器采样,而控制信号因为多为单bit,一般都使用两级寄存器来采样。

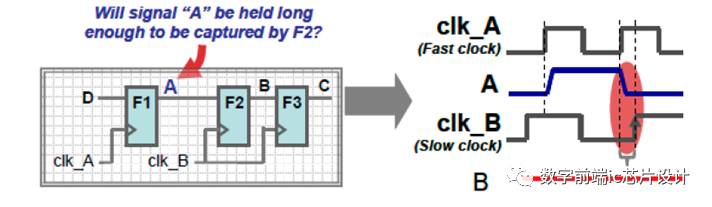

2. fast-slow CDC

除了亚稳态之外,如果信号起始时钟源频率比终点时钟源高很多,那么可能就会导致信号的丢失。

在上图的例子中,虽然A信号到B信号之间使用了同步器,但是如果时钟域A的频率过高,很容易造成信号的丢失。对此,我们需要使用额外的结构来保证A信号不丢失。

常用的方法有两种,一是使用定制化的电路,使A->B之间有至少一个B周期的延时。

另一个是使用控制信号,控制信号的信息来自B时钟域的反馈信号,当B成功完成一次有效采样之后,才让A读取下一个信号。针对不同的具体电路有不同的设计方案,这里就不一一列出。

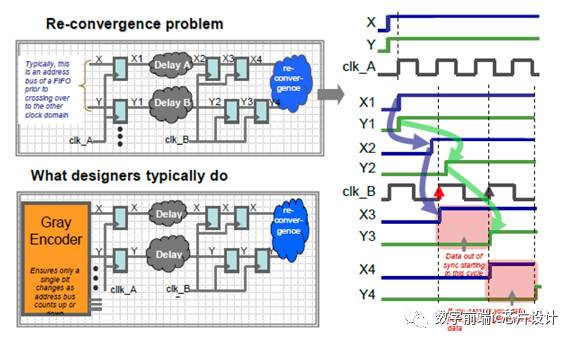

3. multi-bit data correlation

对于多bit的data信号,如果采用每个bit分别同步的方法,由于每个bit到达同步器的延时不同,可能造成采样时刻多bit的信号corelation有问题。

在上图所示例子中,由于每个bit到达2-FFs同步器的时间不同,如果这几位bit同时跳变,可能在第一拍采样的时候采到的不是我们想要的结果。

对此,我们可以使用格雷码,来确保对于多bit信号每次只有一位bit发生了跳变。另外可以使用使能信号,在所有bit的信号都稳定之后,才进行同步采样。

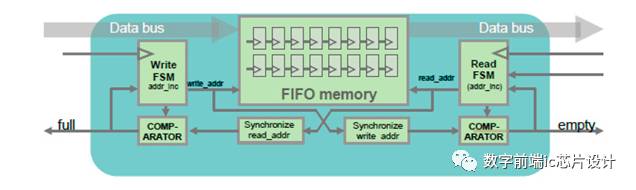

4. FIFO

我们可以使用FIFO来完成跨时钟域的信号转换,下图是一个简单的FIFO例子

FIFO会占用比较多的资源,但对于跨时钟域问题能够有很好的保证。对于FIFO,我们可以使用DesignWare中已经搭建好的标准单元,这是经过验证的可综合的FIFO。在Spyglass中,我们也可以对FIFO的正确性进行验证。

5.reset synchronization

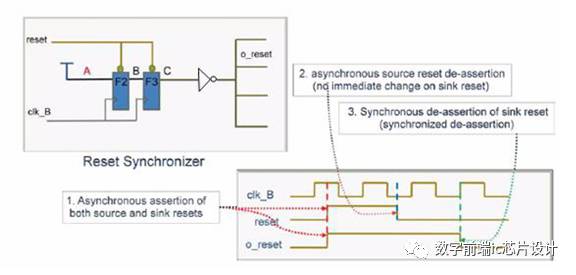

复位信号是一个系统中最重要的几种信号。复位信号的同步也是系统中很关键的一个环节。对于复位信号的同步,我们有一个经典的标准设计方案

从上图中我们可以看到,我们采用了异步复位同步释放地方法。这里并不是直接将复位信号进行两级同步。

以上就是CDC的一些基本问题和经典的解决方案,针对不同设计我们可以有不同的解决方法,而通过Spyglass,我们可以在综合之前对CDC的问题进行一个完整的检测。希望以上对大家的设计有所帮助。

- 相关推荐

- 热点推荐

- CDC

-

如何处理跨时钟域这些基础问题2024-01-08 1517

-

处理跨时钟域(CDC)信号同步的最常见方法2023-09-20 6734

-

跨时钟域电路设计—单比特信号传输2023-06-27 2247

-

CDC跨时钟域处理及相应的时序约束2023-06-21 3395

-

跨时钟域电路设计总结2023-05-18 1574

-

多位宽数据通过握手方式跨时钟域2023-05-06 2374

-

单位宽信号如何跨时钟域2023-04-13 2315

-

各种类型CDC路径中的毛刺问题2023-03-30 1915

-

CDC跨时钟域的基础概念介绍2022-12-26 2937

-

CDC跨时钟域的基础概念2022-08-29 3632

-

关于cdc跨时钟域处理的知识点,不看肯定后悔2021-06-21 2216

-

CDC单bit脉冲跨时钟域的处理介绍2021-03-22 4478

-

vivado约束案例:跨时钟域路径分析报告2020-11-27 7011

-

关于FPGA中跨时钟域的问题分析2019-08-19 4059

全部0条评论

快来发表一下你的评论吧 !