基于ARM+FPGA的开发平台实现了基于CSMA/CA的MAC协议

控制/MCU

描述

0 引言

基于CSMA/CA的MAC协议的优势在于其简单和健壮性,适用于分布式网络,每个节点无需维持和动态更新周围相邻节点的状态信息,可以独自决定何时接入信道,只要上层有数据需要传输,MAC层就会对信道进行竞争,因此该协议的应用也相当广泛。嵌入式技术的发展对MAC协议的实现也提供了很好的技术支撑。本文搭建了一种基于ARM和FPGA相结合的嵌入式开发平台,并在此基础上设计与实现了基于CSMA/CA的MAC协议。由于ARM和FPGA本身就是可重构器件,同时将FPGA中的一些协议参数由ARM来设置,通过修改ARM的代码就可以实现对FPGA中协议功能的调整,方便快捷,不再需要重新生成比特文件下载,有利于MAC协议可重构的实现。

1 协议功能描述

1.1 报文结构

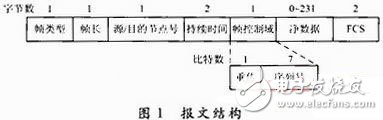

本设计实现的是基于CSMA/CA的MAC协议的基本访问模式,节点之间的通信只有数据帧(DATA)和应答确认帧(ACK)。图1给出了报文结构,其中ACK没有净数据部分。由于考虑的是一跳范围的无线通信,没有中继节点等,因此只有源节点号和目的节点号。

1.2 组网设计

本文设计的MAC协议除了满足基本的的物理载波侦听和虚拟载波侦听相结合检测信道忙闲的机制外,还包括帧间间隔、随机退避、应答确认和重传机制。

有数据要发送的节点会首先监听媒介,若为忙则继续等待,若空闲的时间超过或者等于DIFS或者EIFS则会进入退避进程。在执行退避进程过程中,节点将随机产生一个退避时间来设置退避定时器,同时继续监听媒介,若空闲时间达到了一个时隙时间,则退避定时器减去一个时隙时间,如果在期间媒介变为了忙,退避进程将挂起,直到媒介空闲时间再次达到DIFS或者EIFS后才会接着继续进行退避进程。当退避定时器变为0时,节点才允许开始发送数据,同时也会启动超时重传机制,如果在规定的时间内没有收到所希望的ACK,则会重传数据帧,当节点重传的次数超过了重传门限将会丢弃该数据帧,或者超过了数据帧最长允许的发送时间,也会丢弃该数据帧;当节点收到ACK时,就会开始准备下一次数据的发送。

接收节点收到正确且是发送给本节点的数据帧将会立刻回复源节点ACK。如果节点没有收到正确的数据帧,则将使用EIFS;如果收到正确的数据帧,但是不是给本节点的,节点将解析出持续时间,更新NAV,将信道视为已被占用。

1.3 功能划分

本设计充分利用ARM灵活便捷的优势,用来实现随机退避算法和协议参数的管理,如重传次数,帧间间隔的设置等。随机退避算法采用的是第i次退避就在2i个时隙中随机地选出一个值作为节点需要退避的值。协议参数的设置由ARM来完成,主要是考虑到FPGA不利于参数的修改,这样也可以增强协议的可重构性。而FPGA以其卓越的实时信号处理优点,用于管理MAC帧的收发控制等。

2 协议设计

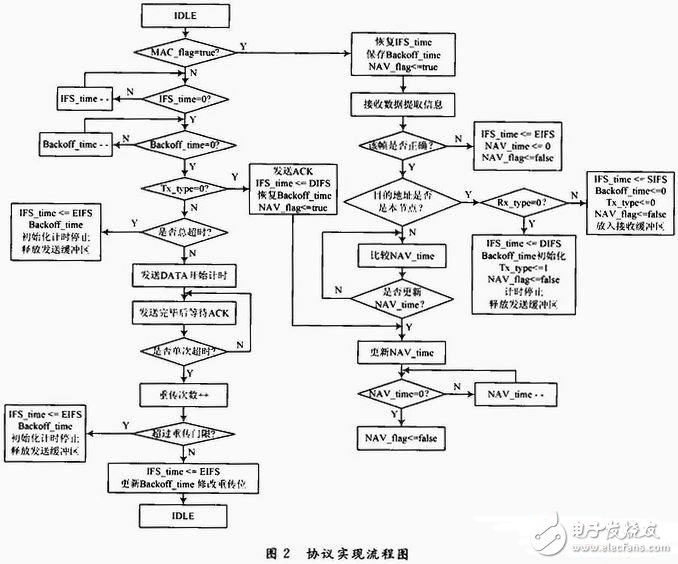

MAC层的工作状态主要是由物理载波侦听和虚拟载波侦听共同决定的(即:MAC_flag=CS_flag or NAV_flag),当两者都显示为空闲时,MAC层才会进入发送数据帧状态。同时该协议也需要时钟计数参与其中,IFS_time是每个节点在进入退避进程前需要等待的时间,实现帧间间隔的功能;Backoff_time是每个节点在退避进程中退避的时间;NAV_time是没有在通信的节点预留信道的时间。这三个时间也关系着整个协议所处的状态。图2给出了具体的实现流程图,具体实现过程步骤如下:

(1)若MAC_flag为false时,表明信道空闲,此时进入(2);若MAC_flag为true,则说明现在信道已被占用,此时不管节点已经处于什么状态都会进入第七步,除了正在发送数据的节点,由于正在发送的节点是不可能监听信道的,而且也无法接收其他节点的数据,载波侦听机制在这种状态下是失效的,因此不会出现正在发送数据的节点从发送状态突然变为接收状态。

(2)执行帧间间隔进程,递减IFS_time大小,直到为0就进入(3)。IFS_time的初始值为DIFS。

(3)退避进程。退避时间的大小主要是由ARM提供,当节点经历了一个时隙时间,退避时隙数减1,但当节点没有完全经历一个时隙时间,退避时隙数就不会变化。退避进程结束后就会进入(4)。

(4)判断发送类型,设计中发送类型Tx_tpye的初始值为1。若Tx_tpye为0,则为节点发送ACK,根据接收到的数据帧中的源/目的节点号以及序列号等组装回复发送节点ACK,并初始化IFS_time和Backoff_time以备节点发送数据帧使用,同时设置NAV_flag为true,更新NAV_time的值,继续虚拟载波侦听,避免出现发送ACK的节点会优先占用信道的情况;若Tx_tpye不为0,则表明节点可以开始发送数据帧,转入(5)。

(5)发送数据帧前首先判断是否超过最大允许发送的时间,若超过了就丢弃该数据帧,将IFS_time设置为EIFS,Backof_time初始化,超时计时器停止;若没有超过最大允许发送时间,则节点正式发送数据帧,并启动单次超时计时,发送完毕后就等待ACK,此时进入(6)。

(6)在等待ACK到来的同时判断是否超时单次允许发送的时间,若超过了,则重传次数递加;然后判断是否超过重传门限,如果超过了门限,则丢弃该数据帧;如果没有超过,则将IFS_time设置为EIFS,而且还需要ARM的随机退避算法根据重传次数重新给一个退避时隙数,同时修改数据帧中的重传位以便接收节点识别。

(7)保存当前退避进程中的Backoff_time和刚刚结束的帧间间隔的大小IFS_time,接收MAC帧并解析其中相关的数据,为后续的组装ACK做准备,然后进入(8),同时将NAV_flag设置为true,保证MAC层能处理完数据。

(8)校验接收到的MAC帧是否正确,若不正确,则将IFS_time设置为EIFS,NAV_flag设置为false,NAV_time设置为0,这样节点就进入执行帧间间隔进程。若校验正确,则进入(9)。

(9)将FPGA解析出来的目的节点号与本节点的比较,判断是否是发送给本节点的。如果不是发送给本节点的,那么就再比较本节点现在的NAV_time值是否大于接收到的MAC帧内的NAV,若大于则本节点继续按照现有的NAV_time值执行下去;若小于接收到的MAC帧内的NAV,则使用MAC帧内的NAV来更新本节点的NAV_time值,然后以最新的NAV_time值递减下去直到为0,虚拟载波侦听显示空闲。但是在执行NAV_time递减过程中随时都有可能收到新MAC帧,而且也不是发送给本节点的,照样要执行本步骤,并不是等到NAV_time变为0后再更新。如果是发送给本节点的,则会进入(10)。

(10)若节点接收到的是数据帧。即Rx_type为1,FPGA将接收到的数据帧上传ARM;同时将IFS_time更新为SIFS,Backoff_time设置为0,这样使得接收到数据帧到发送ACK之间的时间间隔为SIFS,并将Tx_tpye设置为0,NAV_flag变为false,进入(2),开始准备发送ACK。如果Rx_type为0,则节点接收到的是ACK,说明一次数据收发过程结束,节点将初始化相关参数,计时停止等,FPGA释放空间,表明该数据帧已发送成功。

3 仿真验证

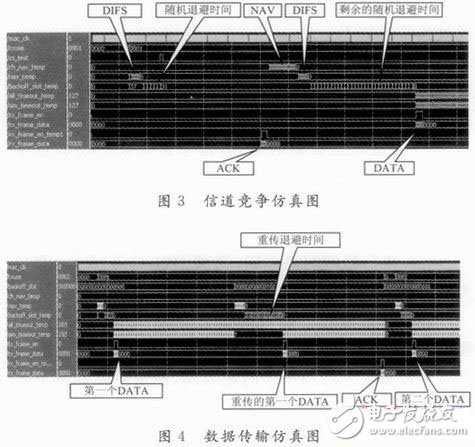

基于CSMA/CA的MAC协议的实现关键在于各个节点对各种情况的处理,因此对一个节点协议功能的仿真验证也能说明设计的正确性。本设计中FPGA部分的设计是重点,所以使用ModelSim进行仿真观察节点FPGA的处理过程。

3.1 信道竞争过程

基于CSMA/CA的MAC协议中各个节点也不知道自身周围的节点情况,因此节点竞争信道时随时都可能检测到信道已被占用。图3给出了节点在退避过程中检测到物理载波侦听变为忙,立刻停止退避进程,将此时的退避时隙数挂起,即退避时隙数保留为31。待到信道重新空闲超过帧间间隔DIFS后,将以保留的退避时隙数继续进行退避进程,变为0后开始发送数据帧。在图中还可以看到节点收到正确的ACK后,更新NAV的过程。从仿真图的执行流程可以说明所设计的MAC协议满足载波侦听机制、帧间间隔、随机退避的功能要求。

3.2 数据传输过程

从图4中可以观察到节点发送第一个数据帧后,超时计数器开始计时,但在规定时间内没有收到ACK,则重传数据帧,重传退避的时间是重新赋值的,并且帧间间隔不再是DIFS,而是EIFS;当节点接收到正确的ACK后,开始发送新的数据帧。说明了所设计的MAC协议能够实现确认重传机制。

4 结语

在以ARM和FPGA为主的硬件结构上,设计与实现了基于CSMA/CA的MAC协议,该协议具有载波侦听机制、随机退避、确认重传等功能。经过仿真测试,验证了所设计MAC协议的可行性。

-

米尔ARM+FPGA架构开发板PCIE2SCREEN示例分析与测试2023-07-07 1457

-

Demo演示:ARM+FPGA主流嵌入式架构板卡-HDMI显示摄像画面2023-01-13 2029

-

CSMA/CA工作流程 CSMA/CA与CSMA/CD的区别2021-08-24 16855

-

求一种短距离无线传输的CSMA/CA协议实现方法2021-05-28 1771

-

怎么实现一种无线传感器网络CSMA协议的设计?2021-05-25 858

-

【Combat FPGA开发板】基于FPGA的网口设计——MAC协议的开发2021-05-06 3756

-

FPGA实现路由、MAC层协议的困难在哪里?2018-07-25 2927

-

基于CSMA/CA的MAC协议设计实现2018-03-28 7784

-

工程师深谈ARM+FPGA的设计架构2015-05-25 22926

-

基于CSMA/CA的无线局域网协议的实现方法2011-12-22 1102

-

ARM+FPGA的高速同步数据采集2010-07-22 1697

-

基于ARM+FPGA的重构控制器设计2010-03-02 1233

-

基于ARM 平台的MAC 协议IP 核设计2009-05-16 1004

全部0条评论

快来发表一下你的评论吧 !