基于65nm工艺的五分频器设计方案

描述

USB 3. 0 是通用串行总线( Universal Serial Bus)的最新规范, 该规范由英特尔等大公司发起, 其最高传输速度可达5 Gb/ s,并且兼容USB 2. 0 及以下接口标准。物理层的并串/ 串并转换电路是U SB 3. 0 的重要组成部分, 在发送端将经过8 b/ 10 b 编码的10 位并行数据转换成串行数据并传输到驱动电路, 在接收端将经过CDR( Clock and Data Recovery) 恢复出来的串行数据转换成10 位并行数据。在并串/ 串并转换过程中,同时存在着时钟频率的转换, 若串行数据采用时钟上下沿双沿输出,则串行数据传输频率降低一半, 并行传输时钟为串行传输时钟的1/ 5, 即五分频。

本文设计了基于65 nm 工艺的五分频器, 产生一个占空比为50%的五分频信号。对该电路的设计不以追求高速度为惟一目标,而是在满足U SB 3. 0 协议所要求的频率范围基础上, 尽可能的降低功耗。

1 电路原理与结构

采用基于D 触发器结构的五分频器逻辑框图如图1所示。图1 由3 个D 触发器和少量逻辑门构成, 采用了同步工作模式, 其原理是由吞脉冲计数原理产生2 个占空比不同的五分频信号A 和B, 然后对时钟信号CLK, A 和B 进行逻辑运算得到占空比为50% 的五分频信号CLK/ 5, 其计数过程如表1 所示, 从表1 的计数过程可知, 分频后的时钟CLK/ 5 的周期是输入时钟CLK 的5 倍, 由此实现了五分频并且其占空比为50% 。

图1 5 分频电路逻辑结构

表1 5 分频器计数过程

2 分频器基本电路的设计

触发器是整个分频器中最基本的结构, 只有设计好一个快速的触发器, 才能实现一个高频率的分频器,目前用于分频电路的触发器电路主要有3 种。第1 种是CML( Current Mo de lo gic) 电路, 是由ECL( EmitterCo uple Logic) 电路演变来的, 相比传统的静态分频器,由于电路的摆幅较小, 因而电路的工作速度快; 第2 种是TSPC( True Single Phase Clock) 电路, 采用单相时钟, 大大减少了电路的元件数目, 从而提高电路工作速度, 同时这种电路功耗极低; 第3 种是注锁式( Injected-Locked) 电路, 由于要使用电感, 因而它的体积过大且工艺难度高, 成本较高, 很少被广泛采用。本文分别采用CML 电路和TSPC 电路构成分频电路, 并对两者的速度和功耗等进行比较。

CML 电路构成的触发器如图2 所示, 由图中可以看出, 该触发器由2 个CML 结构锁存器组成, 它们构成主从型结构, 每个锁存器都要经过2 个阶段: 跟踪阶段和保持阶段。当主锁存器跟踪输入信号时, 从锁存器处于锁存保持阶段, 然后交替。其中N13 , N14 为尾电流管, 偏置电压V_bias 使N13 , N14管工作在饱和状态, 充当恒流源的作用。dp 和dn 是由输入信号d 经传输门和反相器产生的一对互补差分信号, ck_m 和ck_p 是由输入时钟信号clk 经传输门和反相器产生的一对互补时钟差分信号。主锁存器工作状态为: 当ck_m 为高电平时, N5 管导通, N6 管关闭, 此时N1 , N2 管工作在差分状态, 将输入信号dp, dn 采入。当ck_p 为高电平时,N6 管导通, N5 管关闭, 此时N3 , N4 使电路维持在锁存状态, 从锁存器工作状态恰好与主锁存器工作状态相反。设计中在触发器输出端q, qn 之间加了2 个反相器从而在q, qn 之间形成正反馈, 增强了电路的输出驱动能力。工作时, 电路的尾电流应当足够大, 有利于提高电路工作频率和输出信号的摆幅。

TSPC 电路构成的触发器如图3 所示, 由图中可以看出, 该电路由四级反相器构成, 上升沿触发, 当CK 为低电平, 输入反相器在节点X 上采样反向d 输入,第2 级反相器处于保持状态, 节点Y 预充电至V dd,第三级反相器处于保持状态, 时钟上升沿来时, 第二级反相器求值, Y 的电平值发生变化, 时钟ck 为高电平时,节点Y 的值传送到输出q, 该触发器的延时为4 个反相器的传播延时, 由于电路中元件数目很少, 而且采用动态逻辑, 因此功耗极低。

图2 CML 锁存器构成的主从式触发器电路

图3 TSPC 电路构成的触发器

3 仿真结果与分析

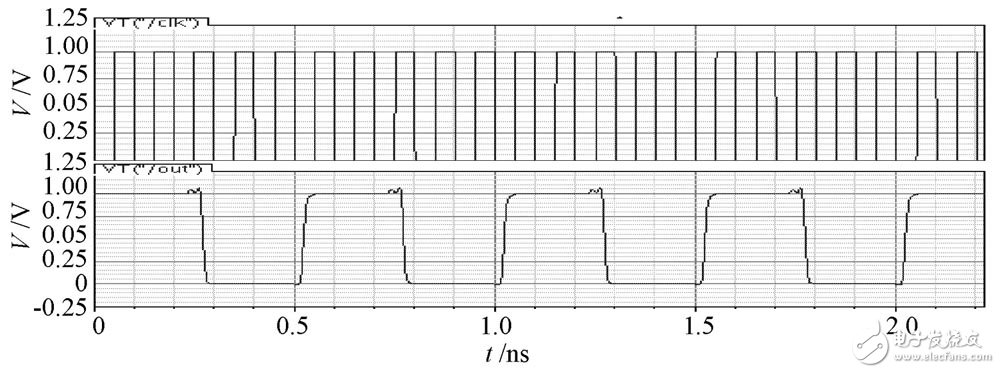

采用Cadence 公司的spect re 仿真器对设计的分频器分别仿真, 仿真电源电压为1 V, 结果表明: 在典型工艺参数条件下,基于CML 电路结构的五分频器最大工作频率是8 GHz, 最小工作频率是1 kHz, 当工作在8 GHz 时, 功耗为1. 7 mW, 输出信号占空比为49. 76% ; 基于T SPC 电路结构的五分频器最大工作频率是10 GHz, 最小工作频率是10 MHz, 当工作在10 GH z时, 功耗采用10 ns 内的平均功耗, 功耗为0. 2 mW, 输出信号占空比为49. 92%.由于是单端输入输出, 基于T SPC 电路结构的分频器抗噪声能力较弱。最高工作频率下的仿真结果如图4, 图5 所示。

图4 基于CML 电路结构的五分频器工作在8 GH z 仿真图

图5 基于T SPC 电路结构的五分频器工作在10 GHz 仿真图

对于不同频率的分频器。通常采用FOM 值来比较其性能, 分频器的FOM 值定义为:

式中: fmax 是分频器的最高工作频率; P 是分频器在最高工作频率下的功耗, 表2 为本文设计的分频器和其他文献中介绍的分频器作对比,所有的分频器均采用CMOS工艺, 对比表明本文设计的5 分频器性能较优,在65 nm 工艺下具有明显的功耗低优势, 尤其是采用TSPC 电路结构的分频器, 功耗极低。

表2 几种分频器性能的总结对比

4 结语

本文基于65 nm 工艺分别采用CML 电路结构和TSPC 电路结构设计了1 个五分频器, 采用spectre仿真表明, 采用CML 结构的分频器最高工作频率8 GHz,功耗1. 7 mW, 输出信号占空比49. 76% ; 采用T SPC 电路结构分频器最高工作频率10 GHz, 功耗为0. 2 mW,输出信号占空比49. 91%, 由于采用单端输入输出, 所以采用T SPC 结构的分频器抗噪声能力较弱。输出信号占空比为50% 是本文一大特点, 2 种结构的分频器工作频率完全覆盖了USB 3. 0 协议所要求的频率范围,满足协议要求。

-

七分频分频器与饮料售货机控制器verilog代码2022-09-01 773

-

基于CPLD/FPGA的半整数分频器设计方案2021-06-17 1159

-

请问D触发器结构的五分频器逻辑电路怎么实现?2019-09-11 4148

-

65nm芯片设计出现的问题该怎么解决?2019-08-07 2428

-

32分频器电路2017-05-01 6031

-

USB3.0中五分频电路设计2011-11-25 11684

-

10-37GHz CMOS四分频器的设计2010-12-29 956

-

基于FPGA的65nm芯片的设计方案2010-08-27 1194

-

二阶分频器低通单元电路2009-12-21 3876

-

高保真三分频扬声器系统分频器电感的精确设计2009-12-15 4143

-

定阻型功率分频器的设计与制作(二)--一分频点的选择2009-12-02 1499

-

四分频器2009-04-11 3894

-

十分频器电路图2009-03-29 8355

-

供数字时钟使用的+5000分频器电路2009-01-13 2396

全部0条评论

快来发表一下你的评论吧 !