一种快速有效的宽带功率放大器匹配电路设计与实现

电源设计应用

描述

摘要: 针对LDMOS宽带功率放大器匹配电路设计, 提出了一种快速、有效的方法。采用多节并联导纳匹配法得出宽带匹配电路的初始值后, 利用ADS软件对匹配网络的S参数进行优化。仿真结果为: 在频率范围为1. 3 GH z~ 2. 3 GH z内, 两端口的反射系数均小于- 25 dB, 匹配网路的传输系数接近0 dB。为实现更好的阻抗匹配, 再用ADS优化匹配网络, 使其阻抗值更接近功率晶体管的实际输出阻抗值。此方法对快速有效地设计宽带功率放大器匹配电路有着很好的借鉴作用。

宽带功率放大器除在军用领域外, 在无线通信、移动电话、卫星通信网、全球定位系统、直播卫星接收、毫米波自动防撞系统、光传输系统等领域都有着广阔的应用前景。

LDMOS功率晶体管较其它微波晶体管有着很好的热稳定性, 频率稳定性, 更好的线性度, 较大的线性增益, 更高的效率和较低的交叉调制失真。同时, LDMOS 是基于成熟的硅工艺器件, 成本较其它GaAs等器件低很多。因此, LDMOS 特别适用于新一代移动通信系统基站中的功率放大器。

阻抗匹配是微波功率晶体管放大器的设计关键, 合适的阻抗匹配网络可以实现通频带内最佳的功率传递效率。即将晶体管放大器的输入阻抗与信号源的内阻实现共轭匹配; 晶体管放大器的输出阻抗与负载阻抗达到共轭匹配。前级晶体管的输出阻抗与后级晶体管的输入阻抗实现共轭匹配。

在阻抗匹配的并联导纳法中, 其所达到的阻抗匹配仅限于在工作频率附近能达到的较好匹配。若工作频率改变, 微波晶体管输入、输出阻抗(或导纳)都会产生相应变化。因此要保持在较宽的工作频带内具有良好的共轭匹配, 就要采用多节并联导纳匹配法。其过程是将晶体管在不同工作频率上测得的导纳值描在导纳圆图上, 按频率顺序由低至高, 将导纳值连成一条曲线。设计时, 据此曲线选用多个并联导纳, 从不同位置接入, 以实现在较宽频带内的共轭匹配。

假设并联电纳多接入点离晶体管的距离为l, 那么在不同工作频率时, 晶体管导纳值沿各自等驻波系数圆转到并联电纳接入点所旋转的波长数l / λ g是不同的l / 长< l / λ短。即在整个工作频带内, 高于中心频率的各点导纳值比低于中心频率的各点导纳值沿各自的等驻波系数圆移动距离所走过的波长数大。这样, 从微带线上的一点转换到另一点, 其导纳值随波长的变化轨迹与原来的不同。这表明, 在整个工作频带内晶体管导纳值变化的轨迹曲线, 在接入一段微带线之后, 在频段高端和低端得到不同的伸缩, 由此可使导纳曲线变换到靠近圆图的中心, 接近于匹配点, 从而达到宽带匹配的目的。

1 设计思路

因输入输出匹配电路设计方法相似, 故在此仅以LDMOS晶体管放大器MRF281Z输出匹配电路设计为例, 采用多节并联导纳匹配法得出宽带阻抗匹配网络的初始值, 再结合基于矩量法的ADS 软件对目标进行优化, 从而快速有效地实现晶体管放大器的宽带阻抗匹配。

2 负载牵引法获得输出阻抗

负载牵引法的原理就是放大器在大信号电平激励下, 通过连续变换负载测试输出功率, 然后在Sm ith阻抗圆图上画出等功率和等增益曲线。这样就可以选择适当的输出阻抗, 准确设计功率放大器,达到所需的增益和输出功率。

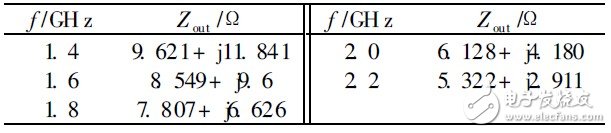

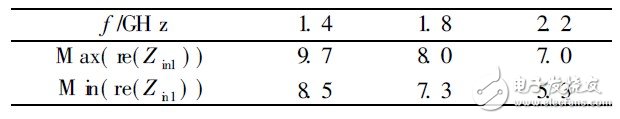

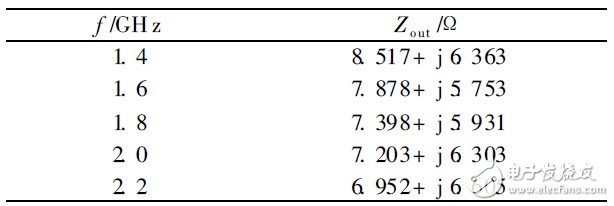

晶体管MRF281Z在1. 4 GH z到2. 2 GHz的各频点的输出阻抗经用ADS 负载牵引后的得到的最佳负载阻抗为表1。

表1 晶体管MRF281Z的输出阻抗

3 多节阻抗匹配网络设计

为了向负载传送最大功率或者使微波电路系统、传输系统处于或接近行波状态, 需要用共轭匹配网络。匹配网络对于放大器的驻波比、功率增益、输出功率等性能指标都有着决定性的制约。

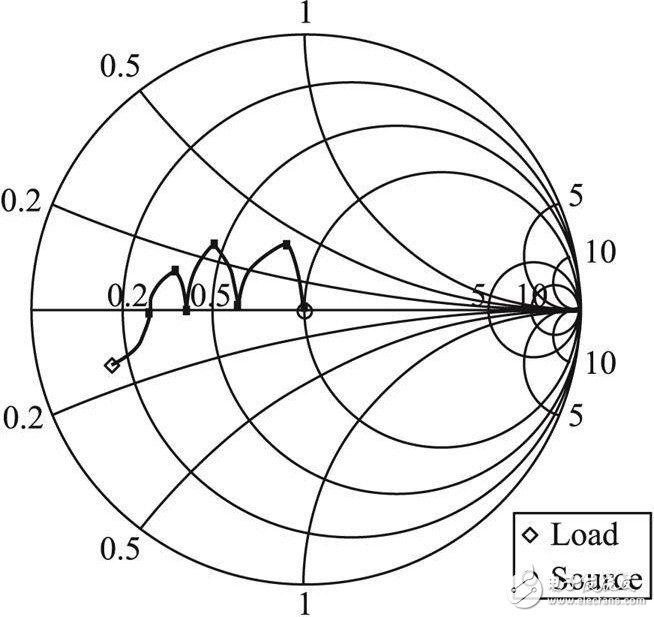

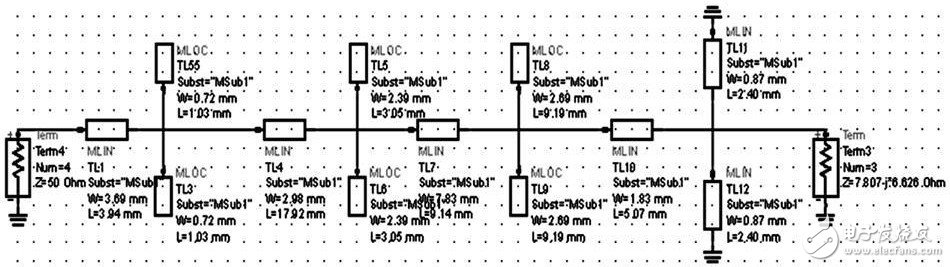

在共轭匹配的条件下, 得到最大传输功率, 在这里我们取频率f = 1. 8 GHz的输出阻抗Z out= 7. 807+ j 6. 626的共轭阻抗Z*out = 7. 807- j 6. 626作为我们匹配端口的阻抗, 在Sm ith 圆图中采用共轭匹配法进行四节微带线匹配(如图1、图2所示)。

图1 多节微带线实现阻抗匹配的Smith圆图

4 用ADS仿真与优化设计

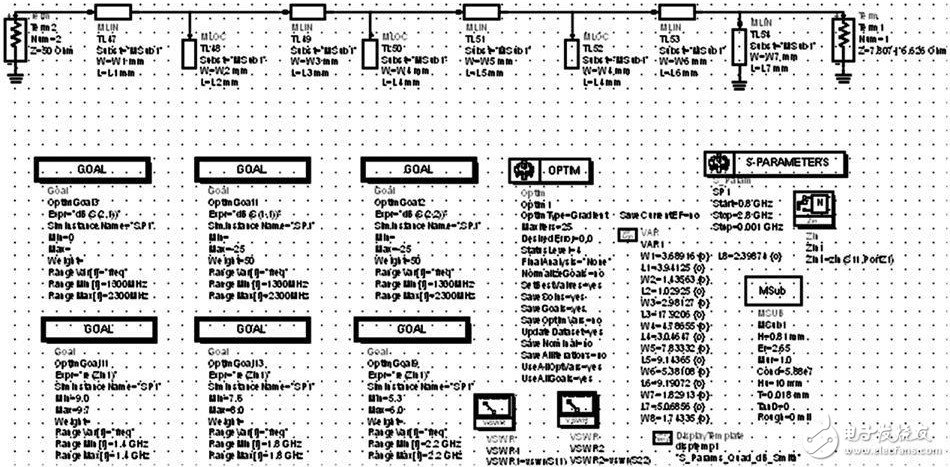

将上面得到的匹配电路用ADS进行仿真, 把各节微带线的长度和宽度设为变量, 并对其进行优化(如图3所示) , 步骤如下:

图3 用ADS对输出匹配电路进行仿真及优化

( 1)在原理图中加入OPTIM 控件:

先用Random 进行初步优化, 再利用Gradient进行局部优化。

( 2)加入优化目标GOAL控件:

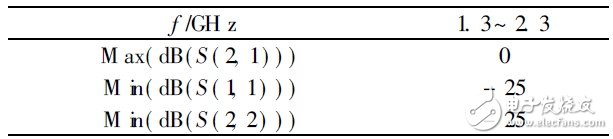

在此, 我们先对匹配网络的S参数进行优化, 具体的S参数优化目标控件配置表如表2所示。

表2 优化S参数目标控件配置表

在完成优化匹配网络的S 参数之后, 为使得匹配网络端口1的阻抗Z in1与晶体管负载牵引得出的输出阻抗基本一致, 我们再对Z in1的实部进行优化,具体优化目标控件配置表如表3所示。

表3 优化阻抗Z in1控件参数配置表

5 各指标ADS仿真结果

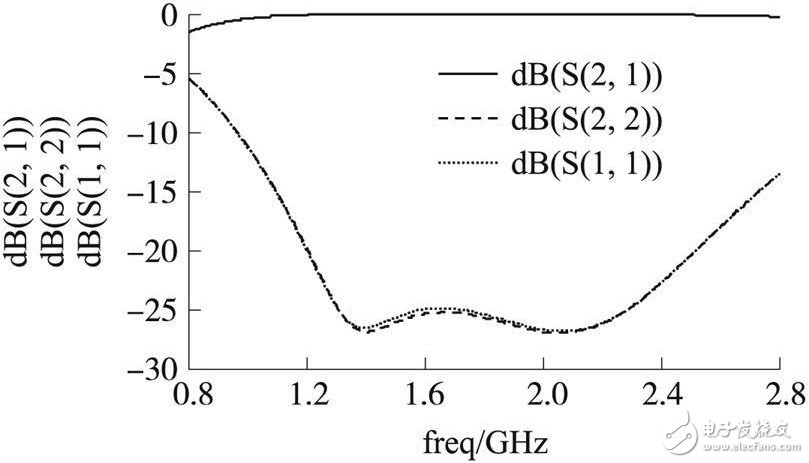

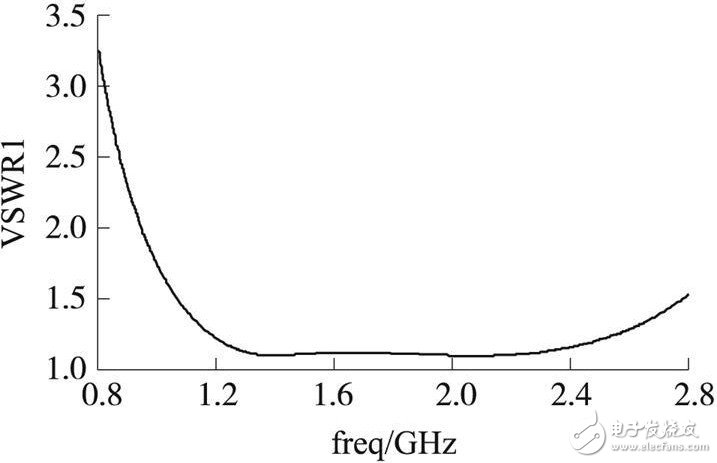

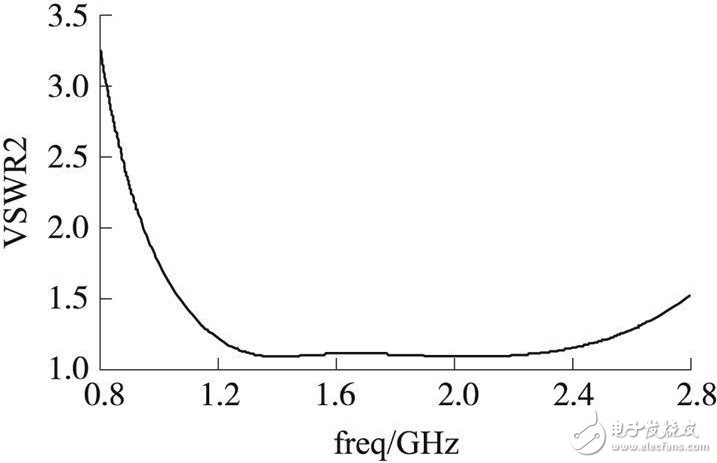

对优化后的晶体管匹配电路在ADS中对S 参数、输出驻波比等性能参数进行仿真, 仿真结果如图4、图5、图6所示。

图4匹配网路的S 参数曲线图

图5 匹配网络的端口1驻波比曲线图

图6匹配网络的端口2驻波比曲线图

将匹配网路端口1的阻抗Z in1用ADS测试出阻抗值结果如表4所示。

表4 输出匹配网路的阻抗值

6 匹配网络的实现

在实际应用中, 单端非平衡的短截线(开路线、短路线)常被平衡型设计方案取代, 上面电路转化为的电路形式为图7所示。

图7 微波晶体管输出匹配网络平衡性设计

输出匹配电路转化成电路版图如图8所示。

图8 微波晶体管输出匹配网络电路版图设计

7 仿真结果分析

从以上仿真结果分析得知, 宽带功率晶体管放大器输出电路阻抗匹配较好, 在频率范围为: 1. 3 GH z~2. 3 GH z范围内, S21正向传输系数接近0 dB, S11、S22即两端口反射系数均小于- 25 dB, 匹配网路两端口驻波比均小于1. 2, 说明正向传输很大, 反射很小。

同时匹配网路端口1阻抗Zin1与晶体管负载牵引的输出阻抗值很接近, 能更好的完成阻抗匹配。因此, 用多节微带线匹配法结合ADS 对目标进行优化, 减少了调试成本、缩短了周期, 对晶体管的宽带匹配网络的实现取得了很好的效果。

-

功率放大器的输入、输出阻抗匹配的实现步骤2023-06-30 14027

-

宽带功率放大器匹配电路设计2021-06-11 1084

-

怎么实现同轴变换器原理及射频功率放大器宽带匹配的设计?2021-05-21 1391

-

短波宽带功率放大器2020-02-07 2119

-

一种利用射频功率放大器电路的GSM/DCS双频段RF射频前端设计2019-07-08 2942

-

快速有效的宽带功率放大器匹配电路的设计与实现2018-10-18 2145

-

GaAs和GaN宽带功率放大器电路设计考虑因素2018-10-17 4395

-

输出匹配电路的功率放大器耗散损失研究2017-12-11 3266

-

一种新颖的射频功率放大器电路结构2017-11-22 1295

-

宽带功率放大器是什么?宽带功率放大器简介、型号参数2017-09-08 2736

-

波形功率放大器的原理与应用2017-06-21 4860

-

射频功率放大器推动电路设计2017-03-10 5076

-

高频宽带功率放大器的设计2012-11-22 4932

-

LDMOS宽带功率放大器匹配电路设计2011-08-18 1983

全部0条评论

快来发表一下你的评论吧 !