ARM Cortex-M3的SRAM单元故障软件的自检测研究

控制/MCU

描述

引言

目前,对于存储单元SRAM的研究都是基于硬件电路来完成,而且这些方法都是运用在生产过程中,但是生产过程并不能完全杜绝SRAM的硬件故障。在其使用过程中,如果SRAM硬件出错,将导致程序出错而且很难被发现。因此在运用的阶段,为防止存储单元损坏而导致系统出错,通过软件的方式对SRAM进行检测是必要的。

1 SRAM运行状态分析

SRAM是存储非CONSTANT变量(如RW),它具有掉电即失的特点。由Cortex—M3的启动步骤可知,系统上电后,首先执行复位的5个步骤:

①NVIC复位,控制内核;

②NVIC从复位中释放内核;

③内核配置堆栈;

④内核设置PC和LR;

⑤运行复位程序。

可以看出,不能在调入C环境之后检测SRAM,必须在Cortex—M3复位之前和启动之后进行检测。

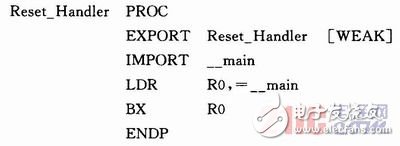

在执行系统复位的最后一个步骤之前,系统都没有对SRAM执行任何相关的数据传送动作。第⑤步运行复位程序,在ST公司Cortex-M3处理器内核的STM32系列微控制器的启动代码中有一段复位子程序:

在这个子程序里导入了__main,__main是C库文件的入口地址。它执行下面3个步骤:

①复制非root(RW、RO)从Flash到SRAM;

②分配ZI区,并且初始化为0;

③跳转到堆栈初始化子程序接口__rt_entry。

由__main的第一步可以得出,在跳入__main之后,系统对SRAM进行了相关数据转移的操作。因此,检测SRAM必须在此步骤之前,否则将会覆盖SRAM从Flash中转移过来的数据。

2 SRAM检测方案设计

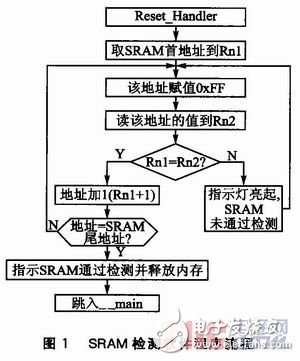

在复位子程序跳入__main之前,设计另一个程序入口SRAM_Check,使PC指针指向该SRAM进行硬件单元检测程序(SRAM_Check)的入口。在SRAM_check里,首先将PC指针指向SRAM的首地址并写入0xFF,读回该地址的值到通用寄存器Rn1,并对Rn1里的值进行加1操作,然后将Rn1和256做比较,得出SRAM硬件是否损坏。这种操作可以避免因SRAM硬件一直为1或0而出现算法本身错误。由于Cortex—M3复位后默认的时钟为HSI,是一个内部RC振荡器,因此精度不高。如果需要更准和快速的时钟,就必须在跳入SRAM_Check之前对相关的寄存器进行操作。

3 SRAM检测软件设计

图1为本文设计的SRAM检测软件程序流程。

4 在线调试结果及分析

上电复位后,在线调试PC指针指向Reset_Handler入口地址时的SRAM初始数值如图2所示。可以看到,当系统复位时每个SRAM单元的数值均为0x00。

在线调试下,图3为对所有的SRAM地址进行检测后SRAM的数值,完全符合程序设计要求。

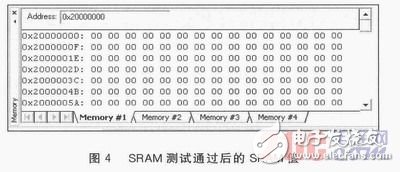

SRAM测试通过后,释放所有的SRAM,还原为0x00,如图4所示。

5 结论

本文提出了一种基于软件的SRAM单元故障自检测方法,通过在线调试得到的结果,可知该方法是完全可行的。在实际运用中,该方法能够确保系统正常地运行在可靠的环境之上。如果SRAM单元有生产或运输等损坏,也可以通过该方法方便地检测出来,大大减少了系统排除故障的时间。

- 相关推荐

-

ARM Cortex-M3的SRAM单元故障软件的自检测研究2011-08-02 0

-

【图书分享】《ARM Cortex-M3权威指南》2014-03-13 0

-

基于CMSIS标准的Cortex-M3应用软件开发2010-02-21 2272

-

ARM7和Cortex-M3比较2010-06-07 2789

-

Cortex M3的SRAM单元故障软件的自检测研究2011-07-29 1585

-

ARM Cortex-M3权威指南2015-12-14 888

-

深入学习ARM Cortex-M3的权威级2017-10-15 934

-

基于CMSIS 标准的Cortex-M3应用软件开发2017-10-26 714

-

基于ARM Cortex-M3的过采样技术2017-10-30 993

-

米尔科技ARM Cortex-M3教程指南2019-11-25 2783

-

ARM Cortex-M3 处理器的主要特性分析2021-06-17 13148

-

Cortex-M3处理器内核与基于Cortex-M3的MCU关系2021-11-05 1598

-

ARM Cortex-M3系统设计与实现2021-11-05 1059

-

MAX32561: DeepCover Secure Arm Cortex-M3 Flash Microcontroller Data Sheet MAX32561: DeepCover Secure Arm Cortex-M3 Flash Microcontroller Dat2023-10-13 16

-

MAX32552: DeepCover Secure Arm Cortex-M3 Flash Microcontroller Data Sheet MAX32552: DeepCover Secure Arm Cortex-M3 Flash Microcontroller Dat2023-10-17 20

全部0条评论

快来发表一下你的评论吧 !