能满足多道脉冲幅度分析器A/D转换要求的高速脉冲峰值保持电路设计

模拟技术

描述

在能谱测量中,多道脉冲幅度分析器所测量的是脉冲的峰值幅度,但探测器输出信号经过线性放大后的脉冲信号峰顶很窄,即使经过理想最佳滤波器将窄脉冲调理成信噪比很高的高斯脉冲,仍不能满足多道脉冲幅度分析特别是A/D转换的要求。这时必须由脉冲峰值保持电路将脉冲峰值甄别并展宽,使脉冲的峰值保持一段时间再送入后续电路。因此,峰值保持电路又叫做模拟展宽器。笔者采用集成芯片设计了一种适用于高速脉冲信号的峰值保持电路,对于100 kHz的模拟信号,峰值保持电路可以准确地采集到峰值并保持,同时向单片机发出请求中断信号,启动A/D转换器。A/D转换完成后,保持电容迅速放电,等待下一个脉冲的到来。

1 峰值保持理论

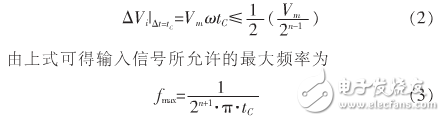

峰值保持电路具有保持和采样2个状态。处于采样状态时,电路的输出始终跟随输入信号;处于保持状态时,电路的输出保持着前一次采样结束前瞬间的输入模拟量。在高速脉冲峰值采集过程中,为保证A/D转换精度,在转换过程中其输入信号变化量不能大于1/2 LSB。假设输入信号Vi=Vmsinωt,则Vi的最大变化率为

当A/D转换器的分辨率为n位,转换时间为tc时,为保证A/D转换器的正常工作,则

设8位A/D转换器的转换时间tc=100μs,代入上式计算可得,A/D转换器的所允许的最大输入信号频率fmax=6 Hz。为获取高频的脉冲信号峰值,必须存信号输入A/D转换器之前对其峰值进行保持。

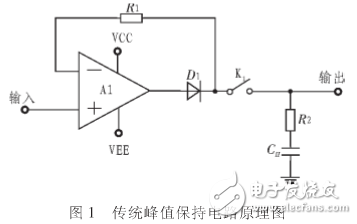

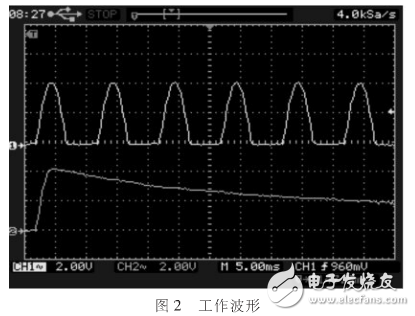

传统的峰值保持电路原理图如图1所示,由集成运算放大器,二极管和电容构成。图2为其工作波形,其中波形1为输入信号波形,波形2为开关K1打开后峰值保持的波形。

在传统的峰值保持电路中,输入信号通过由运算放大器组成的电压跟随器后向保持电容充电,直到充到输入电压的最大值。在理想情况下,保持电容可以保持输入信号的峰值电压,但是实际中二极管的反向电阻不是无穷大,电路下一级也存在电阻并且保持电容存在漏电。从频域来看,二极管和保持电容组成的网络积分非线性大、动态范围小且存在极点,由于二极管内部电阻不是恒定值,极点的位置不固定。通过这样的电路采集到的峰值信号,不能够满足高速脉冲信号处理的要求。为了克服以上缺点,前人做了大量工作,其中文献设计了由肖特基二极管和跨导放大器组成的峰值保持电路,取得了较好效果,但是仍存在对于高速窄脉冲信号响应不灵敏、精度低等不足。本文旨在提出并设计一种适用于高速脉冲信号的峰值保持电路。

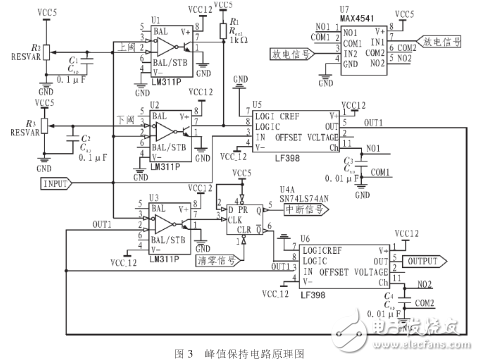

2 电路原理

图3是峰值保持电路原理图,该电路主要由幅度判别、波形采样、峰值保持、电荷泄放等部分组成,幅度判别采用高速低功耗电压比较器LM311实现,电压上阈、下阈由可调精密电位器分压获得。由于LM311输出端集电极开路,将U1,U2输出端接上拉电阻可实现“线与”功能;采用NationalSemiconductor公司的采样保持芯片IF398实现采样/保持功能,其控制端可直接接于TTL、CMOS逻辑电平,LOGIC引脚电平决定电路处于采样/保持状态。模拟开关MAX4541接收单片机控制信号,控制保持电容C3、C4充放电。若输入信号Vi幅度处于上下阈之间,U1、U2同时输出高电平,“线与”后得到高电平送到U5的LOGIC管脚,U5处于采样状态,输出OUT1跟随输入信号Vi变化。峰值没有到来时,OUT1Vi,U3输出高电平,产生上升沿,D触发器U4被触发,/Q输出低电平,U6处于保持状态,将OUT1输出的峰值保持住,并送至A/D转换器;同时Q输出高电平,向单片机发送中断信号,通知单片机峰值到来,单片机收到中断信号后启动A/D转换。A/D转换完成后,单片机向D触发器发出清零信号,同时控制模拟开关U7闭合,保持电容C3,C4放电,等待下一个脉冲的到来。

3 电路调试

3.1 保持电容的选取

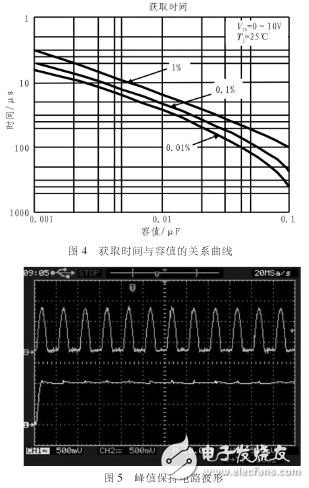

保持电容对于电路精度具有很大影响。电容及其容值的选择应综合考虑下降误差、采样保持偏差、采样频率、精度等指标。保持电容产生误差的主要原因是感应吸收,即电容两端在电压急剧变化时,产生电容值下降的现象。经测试发现:电容两端电压在1μs内由10 V降至100 mV时,聚脂薄膜电容约变化0.8%,陶瓷电容变化在1%以上,本电路中保持电容C3、C4选用感应吸收与漏电流均较小的聚苯乙烯电容。容值的选取参照如图4所示曲线。容值选的过小,则峰值保持时间会缩短;选的过大,则电容充放电时间过长。综合以上因素,C3、C4电容值取0.01μF。

3.2 尖峰电压的消除

在凋试过程中笔者发现,当电路由采样状态切换到保持状态的瞬间,输出端产生了尖峰电压。起初,笔者降低输入逻辑输入信号的幅度(由12 V降低到1 V),但尖峰电压并没有很好的消除。经过对于LF398各管脚间耦合情况的分析测试得出:尖峰电压是由于LF398进入保持状态的同时,逻辑输入信号通过电路板布线间寄生电容耦合和漏电耦合到模拟信号输入端引起的。假设逻辑输入端(也就是LOGIC引脚)与保持电容存在着1 pF的寄生电容,保持电容是0.01μF,那么当逻辑输入端由0 V跳变到5 V,LF398从采样状态切换到保持状态时,相当于在模拟输入端增加了约1 mV的输入信号,因而会在输出端产生尖峰。可以采取以下措施消除尖峰:一是在布线时逻辑输入端走线与模拟输入端走线尽可能远些;二是将模拟输入端用地线包围起来,降低线间寄生电容耦合和漏电耦合干扰。

4 实验结果

为验证文中电路的可行性,用盛谱科技公司的F05型任意波信号发生器产生幅度为1V、频率为100 kHz的脉冲信号作为输入,用同惠电子公司的TD01000型双通道示波器观察输入输出电压波形,如图5所示,波形1为峰值保持电路输入信号波形,波形2为峰值保持稳定后的信号波形。从图中可以看出,文中设计的峰值保持电路较好地保持了输入信号的峰值,起伏较小。电路保持住的峰值与输入信号峰值误差《1%,满足A/D转换的要求。

5 结束语

文中介绍了采用电压比较器LM311,采样/保持芯片LF398集成芯片等构成的峰值保持电路,结构简单、成本低廉、易于调试。实验表明,该电路性能可靠、稳定性好、可以有效地克服温漂,灵敏度好,误差小于《1%,可用于高速脉冲信号的峰值甄别保持,下一步将致力于提高电路在复杂环境下的峰值保持的有效性,提高电路的抗干扰能力。

-

jf_38395046

05-19

0 回复 举报大佬可以帮我看看我这个峰值保持电路的问题吗 收起回复

jf_38395046

05-19

0 回复 举报大佬可以帮我看看我这个峰值保持电路的问题吗 收起回复

-

jf_38395046

05-19

0 回复 举报up主你好,我想请问一下我的峰值保持电路不能正常保持峰值,呈现平滑下降是什么原因呢 收起回复

jf_38395046

05-19

0 回复 举报up主你好,我想请问一下我的峰值保持电路不能正常保持峰值,呈现平滑下降是什么原因呢 收起回复

-

请问怎样去设计一个多道脉冲幅度分析器设?2021-04-14 1608

-

怎么利用LPC2134实现多道脉冲幅度分析器的设计?2021-04-09 1134

-

多道脉冲幅度分析器死时间修正方法探讨2018-04-09 911

-

基于LPC1764的多道脉冲幅度分析器的电路设计2017-09-25 846

-

FPGA数字核脉冲分析器硬件电路2015-02-03 2371

-

高速脉冲峰值保持电路的设计2012-06-28 7465

-

多道脉冲幅度分析器改进研究实现过程分析2012-06-11 1029

-

一种多道脉冲幅度分析器的实现方案2011-10-13 5562

-

基于DSP的多道脉冲幅度分析系统硬件设计2011-02-27 527

-

基于ARM微控制器LPC2134的多道脉冲幅度分析器设计2010-09-25 2657

-

一种实用的脉冲幅度分析器2010-05-25 787

-

可携式多道脉冲幅度分析器研制2010-05-19 556

全部0条评论

快来发表一下你的评论吧 !