数据存储技术之nand_flash结构和原理剖析

描述

1. 引言

NAND FLASH被广泛应用于电子系统中作为数据存储。在各种高端电子系统中现场可编程门阵列(FPGA)已被广泛应用。FPGA灵活的硬件逻辑能实现对NAND FLASH的读写操作。本文中阐述了一种基于NIOS II 软核的NAND FLASH的驱动方法。

2. VDNF2T16VP193EE4V25简介

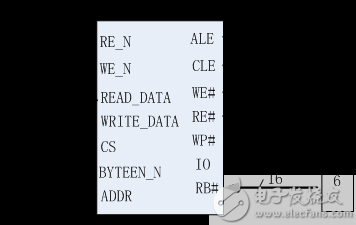

欧比特公司的VDNF2T16VP193EE4V25是一款容量为2Tb、位宽为16位的NAND FLASH,其内部由8片基片拓扑而成,其拓扑结构如下:

图1 VD1D8G08VS66EE8T7B拓扑结构

其主要特性如下:

Ø 总容量2Tb;

Ø 位宽:16位;

Ø SLC;

Ø 兼容ONFI2.2;

Ø 封装:PGA193;

Ø 电源:+3.3V(VCC)、+1.8V(VCCQ)。

3. VDNF2T16VP193EE4V25的控制器设计

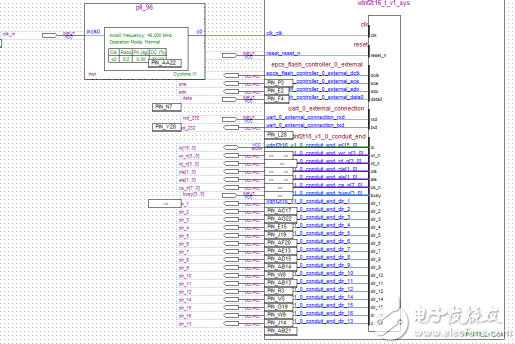

大容量NAND FLASH控制器设计包括一个IP核设计。其基于NIOS II 的AVALON总线。AVALON总线能兼容大部分存储器接口,IP核将AVALON总线时序转接至NAND FLASH,从而对NAND FLASH进行读写操作。

IP逻辑主要有片选信号产生、ALE、CLE、RE、WE等控制信号的转接。其中RE、WE信号可采用AVALON总线的RE、WE信号;CLE、ALE采用总线地址的低2位进行控制;片选数量较多可依据AVALON总线的byteen信号进行译码产生。

图2 控制器功能框图

//写信号

assign nand_wr_n = {avalon_wr_n,avalon_wr_n,avalon_wr_n,avalon_wr_n};

//读信号

assign nand_rd_n = {avalon_rd_n,avalon_rd_n,avalon_rd_n,avalon_rd_n};

//ALE信号,采用地址0

assign nand_ale = {avalon_add[0],avalon_add[0]};

//CLE信号,采用地址1

assign nand_cle = {avalon_add[1],avalon_add[1]};

//片选信号

assign nand_cs_n[0] = temcs[0]|avalon_byteen_n[0];

assign nand_cs_n[1] = temcs[0]|avalon_byteen_n[1];

……

IP核设计完成后采用QSYS进行硬件平台搭建,QSYS系统软核对外引出信号有EPCS、UART、NAND FLASH接口,在Quartus II建立原理图块进行编译产生硬件信息。

采用Nios II Software Build Tools for Eclipse 对QSYS进行软件编程可实现对NAND FLASH的驱动。

//NAND FLASH数据寄存器地址定义

#define NandFlashDataReg0 (VDNF2T16_V1_0_BASE)

//NAND FLASH ALE寄存器地址定义

#define NandFlashAddReg0 (VDNF2T16_V1_0_BASE+4)

//NAND FLASH CLE寄存器地址定义

#define NandFlashCmdReg0 (VDNF2T16_V1_0_BASE+8)

……

以下为读取ID及坏块的信息:

******************************************************************

The cs=0 NAND_FLASH's ID is Right ,The ID is=0x2c881a7a9000

***********************************************************************

This cs=0 FLASH's Bank=0 have 5 BadBlocks:

The num=0 Bank LUN1's num=90 is BadBlock.

The num=0 Bank LUN1's num=91 is BadBlock.

The num=0 Bank LUN1's num=1738 is BadBlock.

The num=0 Bank LUN2's num=90 is BadBlock.

The num=0 Bank LUN2's num=91 is BadBlock.

The Number of Bank's Valid Block is Right.

……

4. 结论

本文阐述了一种通过FPGA实现对欧比特公司的大容量NAND FLASH芯片VDNF2T16VP193EE4V25的操作方法。设计中采用ALTERA公司FPGA芯片,利用自建IP搭建硬件平台实现NAND FLASH的驱动。该设计也可移植到其他FPGA上,可以很好地应用在各嵌入式电子系统中。

- 相关推荐

- 热点推荐

- Nand flash

- 数据存储技术

-

NAND Flash的基本原理和结构2025-09-08 7758

-

【半导体存储】关于NAND Flash的一些小知识2024-12-17 1634

-

从NOR Flash到NAND Flash和SD NAND,从底层结构到应用差异2025-12-08 536

-

从NOR Flash 到 NAND Flash 和SD NAND,从底层结构到应用差异2026-03-05 1169

-

NAND_Flash中文版资料2013-07-16 12657

-

Nand Flash的物理存储单元的阵列组织结构2018-06-12 3484

-

NAND Flash的储存结构与接口设计2020-11-05 3870

-

如何读取nand_flash上的数据2022-02-17 640

-

NAND_Flash长时间读写后会导致读写失败吗?2023-10-16 737

-

NAND_Flash结构与驱动分析2016-03-17 942

-

NAND Flash 的存储结构以及NAND Flash的接口控制设计2020-11-03 5647

-

nand_flash的初始化,如何从nand_flash中读取数据2021-12-22 1146

-

NAND Flash存储器的基础知识2023-09-27 5828

-

MLC NAND Flash:存储技术中的均衡之选2024-06-06 1878

-

NAND Flash与其他类型存储器的区别2024-08-20 2247

全部0条评论

快来发表一下你的评论吧 !