瀚海微SD NAND之SD 协议(32)1.8V信令的驱动强度和总线时序

电子说

描述

输出驱动强度

4级驱动强度为了保持主机系统的灵活设计,输出驱动可以看到大范围的主机负载。

4 种可选驱动强度使主机系统能够调整驱动强度,以优化特定的主机负载。

这使SD卡能够灵活地支持不同的系统负载和系统目标,同时提供非常好的信号完整性性能。

为UHS-I卡1.8V信号电平定义了4种可选择的驱动强度类型。

同时也为主机输出驱动的设计提供参考。

主机应该选择最合适的卡的驱动强度来驱动其特定的PCB。

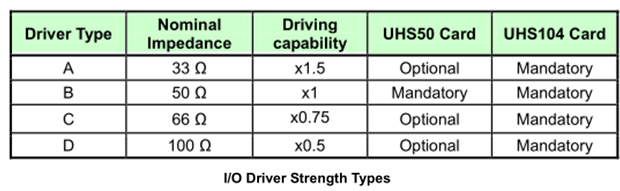

I/O驱动强度类型

卡输出驱动的负载取决于主机的PCB设计。

从驱动器看到的等效电容负载由传输线阻抗、传输线上的信号传播延迟和信号的上升/下降时间决定。

当上升/下降时间大于传输线上若干波反射时间时,认为负载是“集中的”,否则认为负载是“分布的”。

对集总系统的插卡输入、传输线输入和主机输入的总电容负荷进行了估计。

相反,对于分布式系统,估计距离源一定距离的路径上的集总元素的和。

其余的路径电容对驱动器是不可见的。

因此,在这种情况下,通常主控制器输入电容不会被驱动程序看到。

出于测试的目的,将传输线负载转换为等效集总负载,其上升/下降时间与传输线情况相同。

为每种驱动类型定义两个估计电容负载,以定义UHS50和UHS104卡的驱动特性。

驱动类型B

类型B是默认的驱动强度,适用于固定阻抗的分布式系统,传输线为50欧姆,在所有可用频率下。因此,它被定义为50欧姆标称驱动器。该驱动程序可以支持UHS104卡的总CL约15pF, UHS50卡的总CL约30pF。驱动强度B是参考驱动程序定义的所有其余的驱动力量。

驱动程序类型A

类型 A 是x1.5驱动,定义为33欧姆名义驱动,并支持高达208 MHz的操作。

驱动程序类型С

类型C是x0.75驱动程序,它是最弱的驱动,它支持208 MHz的操作,和被定义为66欧姆名义司机。

驱动程序类型D

类型 D驱动程序是一个x0.5驱动,最好是系统速度并不是关键,但更重要的是低噪音/低电磁干扰。D型产生最慢的上升/下降时间。使用一个非常缓慢的上升时间,系统通常将被认为是一个集中负载系统。

D型定义为100欧姆标称驱动器,最大工作频率取决于主机设计。

注:标称阻抗由输出驱动器在0.9V时的I-V特性定义。

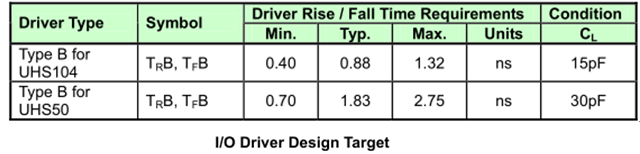

I/O驱动器AC特性介绍

I/O设计器的设计目标。输出驱动器在所有最大到最小延迟条件下的特性最下方的输出测试电路。

升/降时间表

要求下图为UHS104和UHS50卡默认驱动强度(B型)的要求。

A、C、D型驱动器的I-V曲线(电流-电压特性)约为x1.5。

x0.75和x0.5从默认驱动程序类型B

注:1. 典型的上升/下降时间值是设计目标。

2. 任何在最小值和最大值之间的实际上升/下降时间都符合本规范。

输出上升时间在VoL(0.45V)到voH (1.4V)之间测量,输出下降时间在VoH(1.4V)到VoL(0.45V)之间测量。

应用说明:上图也可用于确定主机输出驱动的驱动强度。

其中一种驱动能力应根据主机系统的电容负载进行测量。

当选择D型驱动器时,最大频率由主机系统决定。

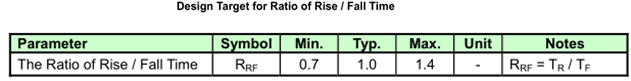

上升/下降时间比的设计目标

6.7.1.3.1中进行的所有测量都满足下图所述上升时间与下降时间之间的允许差值。

最坏的Rrf通常发生在不平衡工艺条件下的快N通道和慢P通道或慢N通道和快P通道。

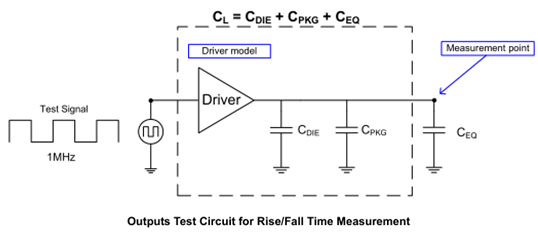

输出驱动测试电路

注:

1. 对于相同的温度和电压,在整个温度和电压范围内指定上升时间与下降时间的比值。

2. 对于给定的温度和电压组合,它表示由于工艺变化而引起的上升和下降时间的最大差异。

术语定义如下:

CL:每条线路的系统总有效电容。 (传输线转换为等效集总负载)

CDIE:卡芯capacitance

CPKG:卡封装电容

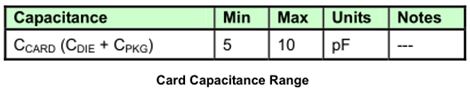

Ccard = CDIE + CPKG

CL= CCARD + CEQ

卡电容范围定义如下:

审核编辑 黄宇

-

ESP32 驱动瀚海微SD NAND 完整方案 + FAT/FAT32 驱动核心区别2026-02-02 739

-

解决SD NAND CRC校验失败的综合指南:瀚海微存储产品的可靠性保障2025-11-21 638

-

瀚海微SD NAND/TF卡:赋能全场景数据存储,定义高效安全新基准2025-10-14 433

-

瀚海微SD NAND/TF卡——数据世界的全能搭档2025-10-13 569

-

瀚海微SD NAND之SD 协议(42)SPI总线时序2024-10-21 1357

-

瀚海微SD NAND之SD 协议(37)SPI总线保护和读写2024-10-09 1443

-

瀚海微SD NAND之SD 协议(36)SPI模式2024-10-08 1467

-

瀚海微SD NAND之SD 协议(33)1.8V供电的驱动强度2024-09-27 1362

-

瀚海微SD NAND之SD 协议(31)总线的信号和时序2024-09-25 908

-

瀚海微SD NAND之SD 协议(29)硬件接口2024-09-24 1491

-

瀚海微SD NAND应用之SD协议系统功能和概念 1 基础知识2024-07-19 1802

-

SD NAND关于3.3V和1.8V之间的转换2023-09-21 5666

-

SD nand 与 SD卡的SPI模式驱动2023-05-10 3003

-

MK SD NAND 1.8v IO电压应用分享2022-11-18 2282

全部0条评论

快来发表一下你的评论吧 !