探讨基于sopc技术的fpga集成嵌入式系统设计

描述

可编程片上系统( SoPC)是在可编程逻辑器件的基础上发展起来的一种灵活、高效的嵌入式系统设计解决方案,系统设计者可以从传统的板级系统设计转换到芯片级系统设计,将系统设计中所需要的各个功能单元以IP ( Intellectual Property)的形式集成到FPGA中,实现集成度更高的嵌入式系统。

Virtex-4系列FPGA是由Xilinx公司推出的包含多个面向特定领域平台的FPGA产品,各个系列的FPGA通过对嵌入式处理器、高性能DSP功能单元、增强时钟管理、存储器、并行和串行I/O、混合信号以及其它功能模块等的优化组合使其可以满足特定领域的应用需求。Virtex-4系列的三个平台分别是:针对逻辑应用的Virtex-4 LX,针对超高性能信号处理的Virtex-4SX,针对嵌入式处理和高速串行连接的Virtex-4 FX。其中Virtex-4 FX系列FPGA主要是为复杂系统应用提供优化,特别是网络、存储、电信和嵌入式应用中的高速串行连接和嵌入式处理,在其配套的EDK环境中还为系统设计者提供丰富的总线、时钟、外设、JTAG口等IP资源,使设计者能够方便的搭建自己的嵌入式系统。

1 Virtex-4 FX系列FPGA介绍

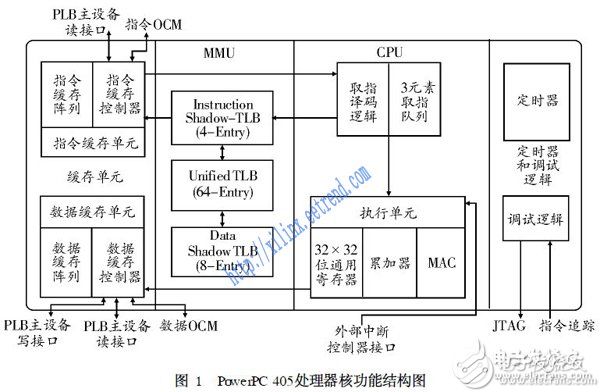

Virtex-4 FX系列FPGA芯片内至少包含一个PowerPC405处理器核,其功能结构如图1所示,该处理器核为32位哈佛结构的R ISC硬核,最高工作频率为400MHz。PowerPC405处理器包括以下功能单元: ( 1)5级数据通道流水线,包括取指、译码、执行、写回、装入写回5 级流水段; ( 2 ) 一个虚拟内存管理单元(MMU) ,支持可变页面大小和写保护、控制访问选项;(3)独立的指令Cache和数据Cache; ( 4)支持调试和跟踪,包含一个JTAG接口; ( 5)三个可编程计时器。另外, PowerPC 405硬核还具有如下特点: ( 1)支持硬件乘法和除法; ( 2) 32个32位通用寄存器; ( 3) 16KB两路组相联方式指令缓存( set-associave) ; (4) 16KB两路组相联方式数据缓存、写回/写直达; ( 5 ) 实现PowerPC用户指令集架构(U ISA) ; ( 6)专用的片上存储器接口(OCM) ; ( 7 )支持IBM CoreConnect总线架构。

CoreConnect总线架构是由IBM开发的一种片上总线通信连接技术。CoreConnect总线包括处理器局部总线( PLB) 、片上外设总线(OPB)和设备控制寄存器总线(DCR) 。PLB总线为主设备和从设备之间提供高带宽、低延迟的连接,OPB总线为连接具有不同总线宽度和时序要求的外设提供了一条途径,减少了对PLB性能的影响,DCR总线用来控制PowerPC405处理器中的通用寄存器和设备寄存器之间的数据传输。

2 基于SoPC的嵌入式系统设计技术

2. 1 平台技术

在平台的基础上来构建嵌入式系统为设计者提供了极大的便利, Xilinx 推出的嵌入式开发工具包( EDK)集成了诸如硬件平台产生器(platgen) 、硬件仿真模型产生器( SimGen) 、软件平台产生器( libgen) 、应用软件编译工具(GNU Compiler) 、软件调试工具(GNU Debugger) 等一系列工具。设计者可以通过集成在EDK环境下的Xilinx平台工作室(XPS)方便的调用各种工具进行基于SoPC的嵌入式系统设计。EDK环境下为系统设计者提供了丰富的IP资源,可利用现有的资源迅速搭建自己的嵌入式系统,完成整个PowerPC系统硬件的开发。如果开发工具包提供的IP库不能满足系统设计者的需求,设计者也可定制自己的IP。图2所示为EDK开发环境图形界面。

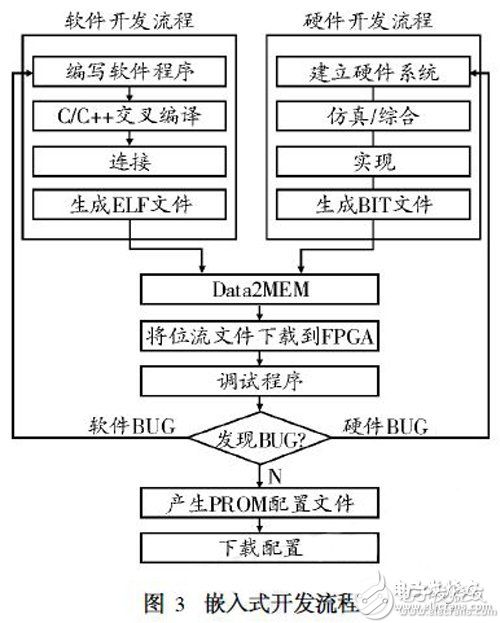

EDK环境为其自带的IP提供了相应的驱动程序及相关的函数,设计者可以通过调用这些函数加快应用程序的开发。对于设计者自行研制的IP,则需要编写相应的驱动程序。应用程序编写完成后,调用EDK下的GNU工具,编译连接生成可执行文件,再将硬件、软件文件结合在一起,产生可下载的位流文件下载到FPGA,使用Xilinx 微处理器调试工具(XMD ) 连接GNU调试工具进行应用程序调试,在确认应用程序正确无误,能实现系统功能之后,即可将位流文件转换成PROM的配置文件(MCS文件) 下载到目标板上的PROM,从而完成整个设计开发。图3为利用EDK工具进行嵌入式系统开发的流程。

2. 2 系统架构及硬件设计

基于SoPC的嵌入式系统设计过程中,系统设计者首先要明确设计需求,这对于整个设计具有指导性作用,也是将来设计完成后检验设计是否可用的标准之一。系统设计者根据设计需求来确定其系统架构,定义系统主要模块组成,决定其接口类型、总线结构、硬件功能及软件功能,完备的系统架构定义要能满足基本的设计需求,并能最大限度的提高系统整体性能。

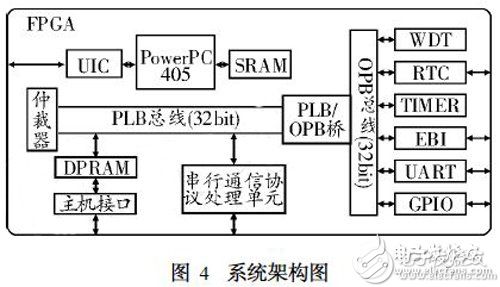

基于SoPC的多路传输数据总线接口的设计需求是在板级多路传输数据总线接口模块的基础上提出的,通过对板级器件的IP化,将原有板上芯片以IP的形式集成到FPGA中,用单片集成电路实现原板级电路的设计。根据板级多路传输数据总线接口模块的系统结构,提出了如图4所示的基于SoPC的嵌入式系统架构图,该嵌入式系统集成了PowerPC405处理器、串行通信总线协议处理器,具有实时时钟(RTC) 、看门狗(WDT) 、计时器( TIMER)功能,可实现GJB289A-97(数字式时分制指令/响应型多路传输数据总线)中规定的RT/BC功能,支持实现ISBC协议(改进的静态总线控制协议) ,通过方式选择分别支持LBE总线访问、VME总线访问、PC I总线访问(通过PLX9054 桥接器) 、PCI-Express总线访问(通过PEX8311桥接器)四

种主机接口访问方式。

硬件设计过程中,系统设计者在XPS图形界面下调用现成的IP库,搭建SoPC的硬件环境,通过硬件平台产生器(p latgen)生成硬件文件,其中PowerPC405处理器、双口存储器、SRAM、串行通信总线协议处理单元挂接在PLB总线上;实时时钟(RTC) 、看门狗(WDT) 、计时器(TIMER) 、外部总线接口( EB I) 、通用输入输出接口( GPIO) 、串口控制器(UART)挂接在OPB 总线上;通用中断控制器(UIC) 、仲裁器和PLB /OPB 桥的寄存器通过DCR总线访问。硬件架构搭建起后通过硬件仿真模型产生器( SimGen)对硬件的功能进行仿真。

2. 3 软件设计

基于SoPC的嵌入式系统软件设计过程中,软件设计者要明确嵌入式系统的相关硬件配置,诸如内存地址映射关系,硬件寄存器配置等,这将决定开发出的嵌入式软件是否具备实用性。嵌入式软件的设计通常包括CPU启动代码,系统初始化代码,硬件自测试程序,设备驱动程序,实时操作系统及应用软件等,根据不同的系统需求,软件包含的内容稍有差异。软件设计阶段,设计者将选择出编译和调试工具并完成编程。

基于SoPC的多路传输数据总线接口的软件由初始化程序、自测试程序、BC /RT控制程序组成。基于SoPC的嵌入式软件开发是在EDK环境下采用C语言编程实现的,通过软件平台产生器( libgen) 、应用软件编译工具(GNU Compiler)编译连接得到可执行文件,该文件可与生成的硬件位流文件通过JTAG接口一起下载到FPGA 运行,也可先将位流文件固化到外部PROM中,应用软件的可执行文件转换成二进制文件固化到外部FLASH中,系统上电后自动加载硬件逻辑并将应用软件搬家到SRAM运行。各部分软件完成如下的功能:初始化程序完成CPU初始化及相关功能单元的初始化;自测试程序完成系统的上电自测试和内部自检; BC /RT控制程序完成该嵌入式系统作为BC或RT时的数据传输控制。基于SoPC的嵌入式系统硬件设计和软件设计可以并行开展,利用软硬件协同设计的思想,可加快整个嵌入式设计的速度。

2. 4 测试验证

基于SoPC的嵌入式系统设计的测试验证用来保证系统不存在软件和硬件上的缺陷。软件测试验证旨在通过执行软件并观察其行为是否满足设计要求,而硬件测试验证则包括了确保硬件能够对外在的激励作出正确的响应并能正确的执行软件。

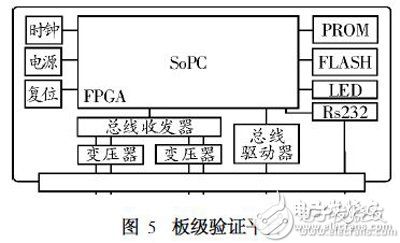

基于SoPC的多路传输数据总线接口中复杂的软硬件结构及其种类繁多的IP资源,使得该系统的测试验证工作也变得复杂。在测试验证过程中,采用多级测试验证技术,首先对各单一模块进行仿真测试,进行软硬件协同验证,再通过集成各个功能模块进行系统集成验证,最后进行板级验证。在进行系统各模块功能验证时,软件可以作为硬件测试的信号源,针对各个模块都编写相应的C语言测试向量,进行功能覆盖率测试。在单一功能模块验证测试的基础上,将各模块集成为一个完整的系统,对整个系统进行集成测试。进行板级验证时,可以运行更为完整、更接近实际应用的C程序测试向量,使得测试更全面、更可靠。图5所示为板级验证平台示意图。

3 结束语

本文通过对Xilinx公司Virtex-4 FX系列FPGA的介绍,分析了其内嵌的PowerPC405处理器的体系结构及CoreConnect总线的特点,通过基于SoPC的多路传输数据总线接口的硬、软件设计技术和验证技术的介绍,更好地阐述了基于SoPC的嵌入式系统设计方法。在基于SoPC的嵌入式系统设计中,通过单片FPGA实现多片专用芯片的功能,减少器件数目,缩小系统面积,增加系统可靠性,达到了对板级多路传输数据总线接口模块小型化、集成化的目的。基于SoPC的嵌入式系统设计以其数据处理速度快、集成度高、开发周期短、应用灵活方便等特点,相信在航空航天领域将会得到广泛的应用。

-

Altera SOPC 嵌入式系统设计(一)2024-06-25 6367

-

嵌入式fpga是什么意思2024-03-15 3721

-

FPGA实现嵌入式系统2021-07-30 1344

-

嵌入式系统的硬件平台组成2020-06-20 3632

-

基于SoPC的嵌入式系统设计方法阐述2020-01-25 2432

-

使用SoPC进行嵌入式系统设计的技术详细说明2019-08-20 1188

-

Altera SOPC嵌入式系统设计教程2019-02-21 3582

-

基于sopc嵌入式文字识别系统设计2018-12-19 1998

-

基于SoPC的嵌入式硬件平台系统设计详解2018-09-25 2534

-

基于SoPC的FPGA集成嵌入式系统设计2017-11-23 2127

-

SOPC嵌入式高频电磁场水处理器设计与实现2013-06-26 995

-

SOPC嵌入式系统实验教程2012-10-25 3246

-

基于SOPC的嵌入式文字识别系统设计2011-09-01 998

-

SoPC培训班(北京未名芯锐FPGA培训学院)2009-09-07 3472

全部0条评论

快来发表一下你的评论吧 !