怎样设计一个基于EDA技术的无线抢答系统?

EDA/IC设计

描述

随着电子技术的发展,应用系统向小型化,快速化,大容量,重量轻的方向发展,电子设计自动化(Electronics Dcsign Automation)技术应运而生,他是电子产品及系统开发领域中一场革命性变革,也是高科技化发展的必然产物。主要应用于数字电路的设计,目前他在中国的应用多数是用在FPGA/CPLD/EPLD的设计中。系统为电子产品的开发,电子系统的设计,电子系统工程提供了高度集成的软件环境,具有完整而自动的实现流程,直观的没计环境,庞大的模拟库,简单而优良的仿真功能等优势。

1 引言

抢答器在各种知识、智力竞赛中有很大的用处,他能准确、公正、直观地判断出第一抢答者,并通过抢答器的指示灯显示和警示蜂鸣等手段指示出第一抢答者。如今在很多的综艺节目中,更多的采用大屏幕显示抢答者,渲染出更加激烈的比赛气氛,而且配合演播厅的整体效果,就要求抢答器也能提供多种接口,并抛弃传统的长长的蜘蛛网似的开关引线。本文所介绍的是一种基于EDA技术的实用器系统的设计方案,他采用超大规模逻辑器件CPLD来处理抢答器的逻辑,通过上位微机来完成声音和动画等效果。该方案的优点在于:反应快、安装简单、覆盖范围广、可扩展性强、使用效果更美观等。

2系统构成

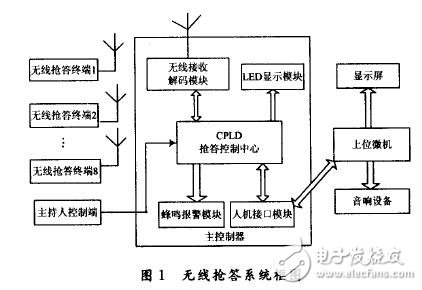

基于CPLD和无线编解码发射接收技术的器系统的原理框图如图1所示,由8路终端、主控制器以及上位微机系统组成。

2.1无线抢答终端

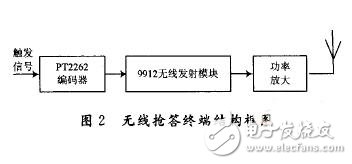

在本设计中,无线抢答终端主要包括编码模块、无线发射模块和功率放大模块,其内部结构框图如图2所示。

其中编码模块采用的是专用红外遥控编码芯片PT2262-IR,在主控制器端的无线解码模块采用的与其配对使用的解码芯片PT2272,他们都是***普城公司生产的一种CMOS工艺制造的低功耗低价位通用编解码电路,最多可有12位三态地址端管脚,任意组合可提供531441地址码。PT2262最多可有6位(DO ~D5)数据端管脚,设定的地址码和数据码从17脚串行输出,非常适合用于无线遥控发射电路,其有效发射接收距离为80 m,发射电路电源范围为2-12 V,接收电路电源范围为4. 8~5. 0 V,发射电路有效发射反应时间≤0. 2 ms.

无线发射接受模块采用通用系列产品9912,在主控制器端的无线接收模块采用的是9921,这样不仅可以加快制作过程,而且还可以增加电路的稳定与可靠性。

2. 2 CPLD主控芯片

系统核心控制芯片采用的是Altera公司MAX7000S系列新一代CPLD器件EPM7128SLC84-15。该芯片采用CMOS E2PROM工艺,传输延迟仅为5 ns;内部具有丰富的资源-128个触发器、2500个用户可编程门;而且具有68个用户可编程的I/O接口,为系统定义输人、输出和双向口提供了极大的方便;为了比较适合混合电压系统,通过配置,输人引脚可以兼容3.3V/5V逻辑电平,输出可以配置为3. 3 V/5 V逻辑电平输出。EPM7128同时还提供了JTAG接口,可进行ISP编程,极大地方便了用户。

新的CPLD芯片技术除了大大减少集成芯片的数目,便于对系统进行扩展,还可以缩短开发周期。降低开发成本,同时提高了技术保密性。与FPGA技术相比,CPLD有掉电不易失的优点,使用更加方便。

2. 3人机接口电路

本系统中,主控制器与上位微机的通信采用RS 232串行异步通信方式。由于CPLD主控芯片的输出电平与RS 232的电平不匹配,所以主控制器与上位微机的人机接口电路,主要选用采用Max232芯片的进行电平转换。Max232是MAXIM公司生产的,包含两路驱动器和接收器的RS 232转换芯片。芯片内部有一个电压转换器,可以把输入的+5V电压转换为RS232接口所需的±10V电压。

3软件设计

本设计中的软件由CPLD控制程序和土位机PC端的动态效果演示程序2部分组成。CPLD控制程序实现与无线接收解码模块的连接及完成与外围模块之间的数据转换和通讯。上位机PC端的动态效果演示程序重点是完成基于VB的交互界面的设计。

3. 1基于CPLD的核心控制程序

CPLD控制程序是本系统软件设计的核心,他采用的是在美国Altera公司的Max+Plus II 10.0平台上用VHDI高级语言输人设计方法。他有专用的工具来实现将语言描述过的电路功能转换为实际的电路,具有很好的通用性和灵活性。他的主要功能:接收并保存无线接收解码模块传送的抢答成功的终端的编码并封锁接收模块,直至控制端复位;同时蜂鸣器奏响并在LED显示抢答成功的终端编号;并完成CPLD与串行接口芯片的数据交换。

该控制程序主要包括4个功能子模块:分频模块、抢答终端编码接收模块、串行发送模块、串行接收模块。在Max-f-Plus II 10. 0中设计输人各个模块的VHDL的程序后,生成库器件并合成系统原理图如图3所示。以下简要介绍抢答终端编码接收模块和串行发送模块的程序设计。

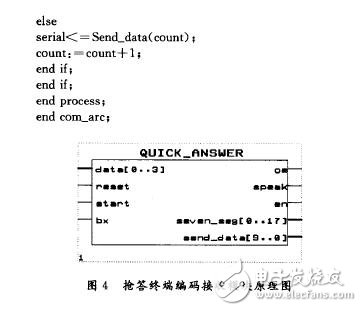

图4为生成的该模块原理图,其VHDL源程序如下:

3.1.2串行发送模块

如图4所示,该模块将抢答终端编码接收模块输出的抢答终端的编码按照串行异步通讯规则发送给人机接口电路。在串口通讯中,我们约定的帧格式为1位开始位+8位数据位+1位停止位,没有校验位,通讯波特率为9600。根据约定,该模块输出数据为10位,在发送完10位后,就停止发送,并使发送端电平处于逻辑1,然后等候下次的发送。其VHDL源程序如下:

3. 2上位机PC端的演示程序

本软件是在VB 6.0环境下开发的,并利用其数据管理功能,建立比赛题库并提供管理界面。其与主控制器之间的串行口通信设计部分充分利用了Mscomm串行口通信控件。由于该控件提供通过串口发送和接收数据的串行通信能力,包括了全部Windows API中关于串行通信的16个函数所完成的功能,而且开拓了更多使用户设计方便的对象属性来满足不同用户不同业务的需求,因此给编程带来极大的方便。

本软件在PC环境下运行,包括以下几个功能:根据设定自动抽出比赛题目、控制主控制器的工作、声光效果显示抢答终端编号并倒数计时、现场效果渲染等。详细程序在此不再赘述。

4结语

经过反复试验,该系统运行稳定,操作方便,达到了预期的设计效果,具有可操作性强、现场效果好的特点,已经在知识竟赛等相关活动中实际使用。

-

EDA程序设计之抢答器2023-08-22 511

-

怎样去编写一个PLC抢答系统2022-02-16 989

-

怎样去设计一个基于单片机智能抢答器控制系统2022-01-13 902

-

怎样去设计一个基于STM32的四人抢答器2021-09-24 3429

-

使用STM32单片机设计一个无线抢答器的资料合集详细说明2020-08-11 2264

-

使用NRF24L01设计多路无线智能抢答器的详细资料说明2020-01-03 1498

-

基于STM32的无线抢答器2018-08-29 17980

-

同立创商城一起学习制作无线抢答器2017-05-23 4248

-

实时互锁式无线抢答手柄的设计与应用2012-07-30 1153

-

基于AT89S52单片机的无线抢答记分系统的设计与制作2012-07-12 1207

-

电子抢答器的EDA设计与实现2011-10-25 4544

-

基于OuartusⅡ和GW48EDA开发工具的电子抢答器设计2010-11-22 1113

-

EDA求助2010-06-05 3122

-

EDA高手看看~~~~2008-12-28 4532

全部0条评论

快来发表一下你的评论吧 !