cadence是什么软件_有什么用途

电子常识

描述

铿腾电子科技有限公司(Cadence Design Systems, Inc; NASDAQ:CDNS)是一个专门从事电子设计自动化(EDA)的软件公司,由SDA Systems和ECAD两家公司于1988年兼并而成。是全球最大的电子设计技术(Electronic Design Technologies)、程序方案服务和设计服务供应商。其解决方案旨在提升和监控半导体、计算机系统、网络工程和电信设备、消费电子产品以及其它各类型电子产品的设计。产品涵盖了电子设计的整个流程,包括系统级设计,功能验证,IC综合及布局布线,模拟、混合信号及射频IC设计,全定制集成电路设计,IC物理验证,PCB设计和硬件仿真建模等。 其总部位于美国加州圣何塞(San Jose),在全球各地设有销售办事处、设计及研发中心。2016年,Cadence被《财富》杂志评为“全球年度最适宜工作的100家公司”。

Cadence 是一个大型的EDA 软件,它几乎可以完成电子设计的方方面面。包括ASIC 设计,FPGA 设计和PCB 板设计。与众所周知的EDA 软件Synopsys相比,Cadence 的综合工具略为逊色。然而Cadence 在仿真电路图设计,自动布局布线,版图设计及验证等方面却有着绝对的优势.Cadence 与Synopsys的结合可以说是EDA 设计领域的黄金搭档。此外Cadence 公司还开发了自己的编程语言skill,并为其编写了编译器。由于skill 语言提供编程接口甚至与C 语言的接口,所以可以以Cadence 为平台进行扩展用户,还可以开发自己的基于Cadence 的工具。实际上整个Cadence 软件可以理解为一个搭建在skill语言平台上的可执行文件集。所有的Cadence 工具都是用Skill 语言编写的。

Cadence 是一个大型的EDA 软件,它几乎可以完成电子设计的方方面面,包括ASIC 设计、FPGA 设计和PCB 板设计。Cadence 在仿真、电路图设计、自动布局布线、版图设计及验证等方面有着绝对的优势。Cadence 包含的工具较多几乎包括了EDA 设计的方方面面。下面主要介绍其产品线的范围。

1、板级电路设计系统

包括原理图输入、生成、模拟数字/混合电路仿真,fpga设计,pcb编辑和自动布局布线mcm电路设计、高速pcb版图的设计仿真等等。包括:

A、Concept HDL原理图设计输入工具, 有for NT和for Unix的产品。

B、Check Plus HDL原理图设计规则检查工具。(NT & Unix)

D、Allegro Expert专家级PCB版图编辑工具 (NT & Unix)

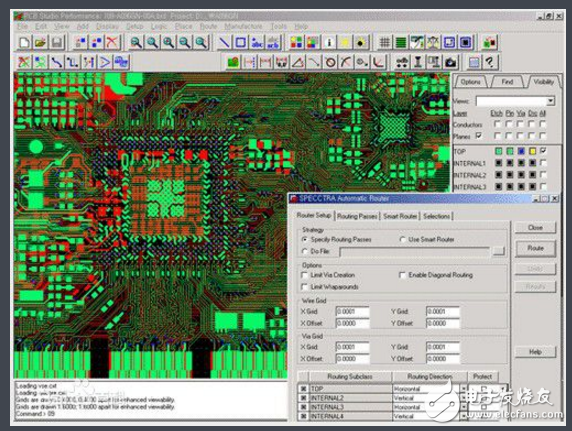

E、SPECTRA Expert AutoRouter 专家级pcb自动布线工具

F、SigNoise信噪分析工具

G、EMControl 电磁兼容性检查工具

H、Synplify FPGA / CPLD综合工具

I、HDL Analyst HDL分析器

J、Advanced Package Designer先进的MCM封装设计工具

2、Alta系统级无线设计 这部分包括:

A、SPW (Cierto Signal Processing Work System)信号处理系统。 可以说,spw包括了matlab的很多功能,连demo都有点象。它是面向电子系统的模块化设计、仿真和实现的环境。它的通常的应用领域包括无线和有线载波通信、多媒体和网络设备。在进行算法设计、滤波器设计、c Code生成、软/硬件结构联合设计和硬件综合的理想环境。

它里面非常有意思的就是信号计算器。

B、HDS (Hardware Design System)硬件系统设计系统

它现在是SPW的集成组件之一。包括仿真、库和分析扩展部分。可以进行spw的定点分析行为级和rtl级的代码生成。

C、Mutimedia多媒体 (Multimedia Design Kit)

它可以进行多媒体应用的设计,包括电视会议系统、数字电视等等以及任何种类的图象处理系统的设计。

D、无线技术Wireless(IS-136 Verification Environment)

无线电技术标准系统级验证工具,可以在系统级的抽象层上生成、开发和改进遵守IS-54/136 标准的信号处理算法。在完成硬件结构设计后,就可以使用hds直接生成可综合的hdl描述和相应的标准检测程序(testbench)。 E、IS-95无线标准系统级验证 同上。

F、BONeS网络协议分析和验证的设计工具。

它是一套软件系统,专门用来做多媒体网络结构和协议的设计的。可以用来快速的生成和分析结构单元之间的信息流的抽象模型,并建立一个完整的无线网络的运作模型。例如,用户可以改进atm转换器的算法,并建立其基于微处理器包括高速缓存和内存和总线、通信处理方法的应用模型。 G、VCC 虚拟协同设计工具包

它是用来进行基于可重用的ip核的系统级设计环境。

3、逻辑设计与验证(LDV)

LDV包括的模块有:

A、verilog-xl仿真器

B、Leapfrog VHDL仿真器

支持混合语言的仿真,其vhdl语言的仿真是通过编译后仿真,加快了速度。

C、Affirma NC Verilog仿真器

其主要的特点是适合于大系统的仿真。

D、Affirma NC VHDL仿真器

适用于VHDL语言的仿真。

E、Affirema 形式验证工具--等价检验器

F、Verifault-XL 故障仿真器

用来测试芯片的可测性设计的。

G、VeriSure代码覆盖率检查工具

H、Envisia Build Gates 综合工具

4、时序驱动的深亚微米设计

Cadence 的底层软件有:

A、逻辑设计规划器。

这是用于设计早期的规划工具。其主要用途是延时预测、生成供综合工具使用的线路负载模型。这个工具是用来在物理设计的早期象逻辑设计者提供设计的物理信息。

B、物理设计规划器。

物理设计的前期规划。对于大型设计而言,物理设计的前期规划非常重要。很多流程中,在前期的物理规划(floorplan)结束后,就需要一次反标验证设计的时序。

C、SE (Silicon Ensemble)布局布线器

se是一个布局布线的平台,它可以提供多个布局布线及后期处理软件的接口。

D、PBO Optimization基于布局的优化工具

E、CT-GEN 时钟树生成工具

F、RC参数提取 HyperRules规生成,HyperExtract RC提取,RC简化,和delay计算

G、Pearl静态时序分析

Pearl 除了界面友好的特点外,还有就是可以和spice仿真器交换数据来进行关键路径的仿真。 H、Vampire验证工具

5、全定制ic设计工具

这部分的工具包括:

A、Virtuos Schematic Composer : IC Design Entry

它是可以进行混合输入的原理图输入方式。支持 vhdl/hdl语言的文本输入。

B、Affirma Analog DEsign Environment

这是一个很好的混合信号设计环境

C、Virtuos Layout Editor版图编辑

它支持参数化单元,应该是一个很好的特性。

D、Affirma Spectra

高级电路仿真器和hspice一类的仿真器。

E、Virtuoso Layout Synthesizer

直接的layout生成工具,小规模设计环境

F、Assura验证环境,包括diva

G、dracula验证和参数提取包

H、ICCragtsman 布局设计的环境。

在面向ip的设计中比较合适。

- 相关推荐

- 热点推荐

- Cadence

-

请问各位要积分有什么用途呢?2014-09-26 4353

-

哪里有Cadence软件2015-08-21 4137

-

请问cadence拓扑是做什么用的?2019-03-05 3336

-

请问这些是什么类型的寄存器?有什么用途?2019-06-05 1846

-

请问这个C1有什么用途,是什么反馈2020-05-04 2305

-

static有什么用途?2021-12-24 978

-

usb外置声卡有什么用途?和一般声卡有什么区别?2023-11-10 1043

-

电池中的钴有什么用途?2009-10-26 11642

-

玻璃水,玻璃水是什么?有什么用途?2010-03-10 29824

-

空气质量传感器有什么用途?2011-01-28 929

-

cadence鼠标增强软件2016-08-03 934

-

镍氢电池具体有什么用途2017-12-12 16590

-

PLC通讯接口有什么用途2022-06-06 5303

-

光纤是什么?有什么用途?2023-05-16 11523

-

氧化硅薄膜具体有什么用途呢?2024-04-22 2568

全部0条评论

快来发表一下你的评论吧 !