74ls138工作原理详解(引脚图及功能_参数_逻辑功能及应用电路)

IC应用电路图

描述

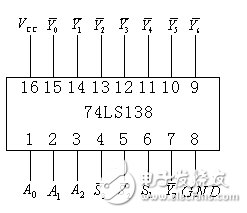

一、74ls138引脚图及功能

1、引脚图:

2、引脚功能:

A0~A2:地址输入端

STA(E1):选通端

/STB(/E2)、/STC(/E3):选通端(低电平有效)

/Y0~/Y7:输出端(低电平有效)

VCC:电源正

GND:地

A0~A2对应Y0——Y7;A0,A1,A2以二进制形式输入,然后转换成十进制,对应相应Y的序号输出低电平,其他均为高电平;

编辑推荐:74ls138管脚图及功能真值表

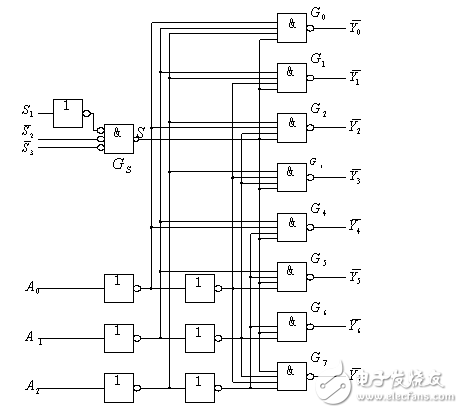

二、74ls138工作原理

74LS138 为3 线-8 线译码器,共有 54/74S138和 54/74LS138两种线路结构型式,其工作原理如下:

①当一个选通端(E1)为高电平,另两个选通端((/E2))和(/E3))为低电平时,可将地址端(A0、A1、A2)的二进制编码在Y0至Y7对应的输出端以低电平译出。(即输出为Y0至Y7的非)比如:A2A1A0=110时,则Y6输出端输出低电平信号。

②利用 E1、E2和E3可级联扩展成 24 线译码器;若外接一个反相器还可级联扩展成 32 线译码器。

③若将选通端中的一个作为数据输入端时,74LS138还可作数据分配器。

④可用在8086的译码电路中,扩展内存。

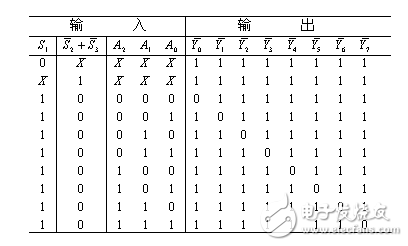

三、74ls138逻辑功能真值表

1、用与非门组成的3线-8线译码器74LS138

2、3线-8线译码器74LS138的功能表

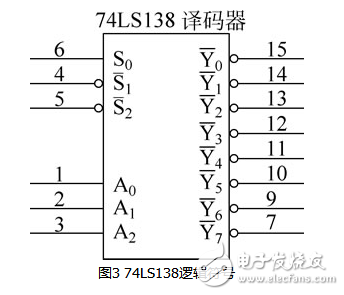

3、74ls138逻辑符号

无论从逻辑图还是功能表我们都可以看到74LS138的八个输出引脚,任何时刻要么全为高电平1—芯片处于不工作状态,要么只有一个为低电平0,其余7个输出引脚全为高电平1。如果出现两个输出引脚同时为0的情况,说明该芯片已经损坏。

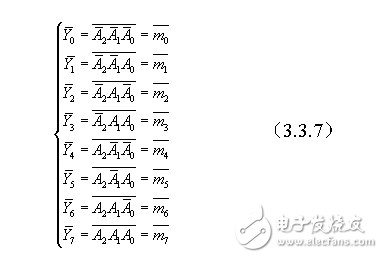

当附加控制门的输出为高电平(S=1)时,可由逻辑图写出

由上式可以看出,同时又是这三个变量的全部最小项的译码输出,所以也把这种译码器叫做最小项译码器。

71LS138有三个附加的控制端、和。当、时,输出为高电平(S=1),译码器处于工作状态。否则,译码器被禁止,所有的输出端被封锁在高电平,如表3.3.5所示。这三个控制端也叫做“片选”输入端,利用片选的作用可以将多篇连接起来以扩展译码器的功能。

带控制输入端的译码器又是一个完整的数据分配器。在图3.3.8电路中如果把作为“数据”输入端(同时),而将作为“地址”输入端,那么从送来的数据只能通过所指定的一根输出线送出去。这就不难理解为什么把叫做地址输入了。例如当=101时,门的输入端除了接至输出端的一个以外全是高电平,因此的数据以反码的形式从输出,而不会被送到其他任何一个输出端上。

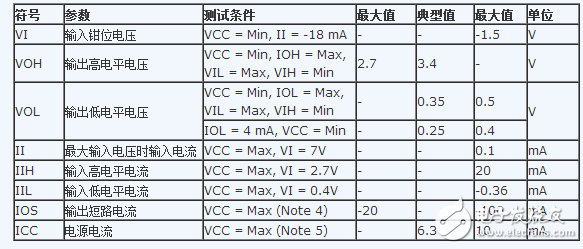

四、电气参数:

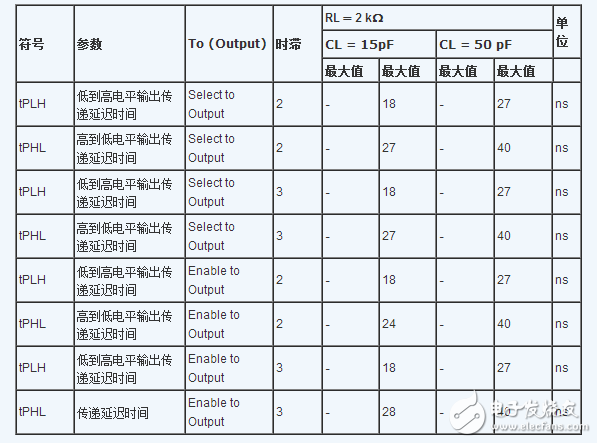

五、动态特性表

六、74ls138应用电路(实例)

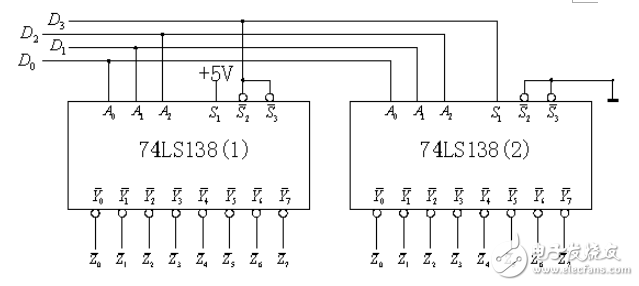

例1:试用两片3线-8线译码器74LS138组成4线-16线译码器,将输入的4位二进制代码译成16个独立的低电平信号。

解:由下图可见,74LS138仅有3个地址输入端。如果想对4位二进制代码,只能利用一个附加控制端(当中的一个)作为第四个地址输入端。

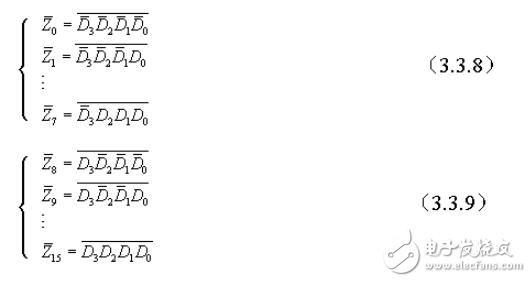

取第(1)片74LS138的和作为它的第四个地址输入端(同时令),取第(2)片的作为它的第四个地址输入端(同时令),取两片的、、,并将第(1)片的和接至,将第(2)片的接至,如图3.3.9所示,于是得到两片74LS138的输出分别为

下图用两片74LS138接成的4线-16线译码器

式(3.3.8)表明时第(1)片74LS138工作而第(2)片74LS138禁止,将的0000~0111这8个代码译成8个低电平信号。而式(3.3.9)表明时,第(2)片74LS138工作,第(1)片74LS138禁止,将的1000~1111这8个代码译成8个低电平信号。这样就用两个3线-8线译码器扩展成一个4线-16线的译码器了。

同理,也可一用两个带控制端的4线-16线译码器接成一个5线-32线译码器。

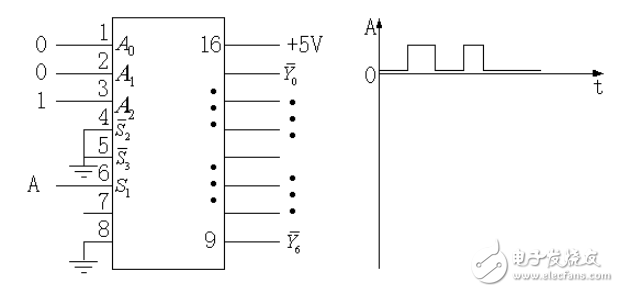

例2: 74LS138 3-8译码器的各输入端的连接情况及第六脚()输入信号A的波形如下图所示。试画出八个输出引脚的波形。

解:由74LS138的功能表知,当(A为低电平段)译码器不工作,8个输出引脚全为高电平,当(A为高电平段)译码器处于工作状态。因所以其余7个引脚输出全为高电平,因此可知,在输入信号A的作用下,8个输出引脚的波形如下:

即与A反相;

其余各引脚的输出恒等于1(高电平)与A的波形无关。

74ls138相关文章:74ls138应用电路图大全(五款74ls138全加器电路/抢答器电路/三人表决器电路)

-

利用74LS138实现逻辑函数式Y的逻辑功能2023-03-23 28385

-

如何对74LS138译码进行实验2021-07-14 6954

-

74ls595和74hc595区别(引脚图及功能、应用电路图)2018-05-29 47642

-

74ls190中文资料汇总(74ls190引脚图及功能_工作原理及应用电路)2018-05-28 357351

-

74ls162中文资料汇总(74ls162引脚图及功能_逻辑图_特性参数及应用电路)2018-05-08 109742

-

74ls138应用电路图大全(五款74ls138全加器电路/抢答器电路/三人表决器电路)2018-05-04 122454

-

74ls273中文资料汇总(74ls273引脚图及功能_工作原理及应用电路)2018-04-26 190481

-

74ls07引脚图及功能_74ls07工作原理2018-04-04 85460

-

74ls138中文资料详解2017-11-03 70886

-

74hc138和74ls138的区别2017-10-31 50649

-

74LS1382016-04-29 4211

-

74ls138真值表_74ls138功能表2011-03-20 10668

-

74ls138译码器内部电路逻辑图功能表简单应用2009-07-13 68023

-

74ls138引脚图-74ls138管脚图及功能真值表2007-12-17 194494

全部0条评论

快来发表一下你的评论吧 !