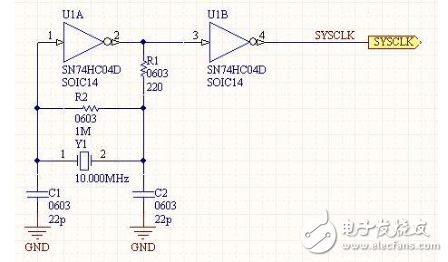

74HC04和晶振做晶体振荡电路产生时钟信号

IC应用电路图

描述

时钟信号为CMOS电平输出,频率等于晶振的并联谐振频率。74HC04在这里相当于一个有很大增益的放大器;R2是反馈电阻,取值一般≥1MΩ,它可以使反相器在振荡初始时处于线性工作区,不可以省略,否则有时会不能起振。R1作为驱动电位调整之用,可以防止晶振被过分驱动而工作在高次谐波频率上。C1、C2为负载电容,实际上是电容三点式电路的分压电容,接地点就是分压点。以接地点即分压点为参考点,输入和输出是反相的,但从并联谐振回路即石英晶体两端来看,形成一个正反馈以保证电路持续振荡。C1、C2会稍微影响振荡频率。

74HC04可以用74AHC04或其它CMOS电平输入的反相器代替,不过不能用TTL电平输入的反相器,因为它的输入阻抗不够大,远小于电路的反馈阻抗。

实际使用时要处理好R1和R2的值,经试验,太小的R1或太大的R2会有可能导致电路工作在晶振的高次谐振频率上(常见的是3次谐波,10MHz的晶振会产生30MHz的频率输出)。对于10MHz的晶振,采用R1=220Ω、R2=1MΩ可以使电路稳定输出10MHz的方波时钟信号。

最后,不要忘记,74HC04中未使用的输入引脚要接地或VCC。

晶振电路

用反向器(74LS00)与晶振、两个小电容、一个大电阻。用的是典型电路,可在示波器上就是不振?

HC的或HCT的才行,如果电容小的话,应该用MOS输入的门。LS芯片的最高截止频率没问题,原因是LS芯片需一个百欧级偏置电阻才能达到线性状态,此时增益又不够。

HC和LS速度上并无区别(最大40兆),问题出在振荡电路是将非门当成线性反向放大器来使用。HC只要加个10兆电阻即可,此时仍有足够的放大倍数(约100)。LS加个1兆电阻仍是非线性状态,不可能振荡,需要5千才能线性,但此时负反馈太深,放大倍数过小(小于10),仍不可能振荡。

原先CMOS比TTL的速度低,高速CMOS与TTL的速度低错不多,由于CMOS的优点工耗低,故得以发展,HC就是高速CMOS,但TTL的可靠性要好(短路不会烧掉,CMOS就不同啦)。

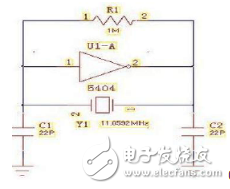

我想很多的单片机爱好者对晶振两边要接22或者30pF的电容不理解,因为电容有些时候是可以不要的。 其实单片机和其他一些IC的振荡电路的真名叫“三点式电容振荡电路”,如下图

Y1是晶体,相当于三点式里面的电感,C1和C2就是电容,5404非门和R1实现一个NPN的三极管,接下来分析一下这个电路。5404必需要一个电阻,不然它处于饱和截止区,而不是放大区,R1相当于三极管的偏置作用,让5404处于放大区域,那么5404就是一个反相器,这个就实现了NPN三极管的作用,NPN三极管在共发射极接法时也是一个反相器。大家知道一个正弦振荡电路要振荡的条件是,系统放大倍数大于1,这个容易实现,相位满足360度,与晶振振荡频率相同的很小的振荡就被放大了。

接下来主要讲解这个相位问题: 5404因为是反相器,也就是说实现了180°移相,那么就需要C1,C2和Y1实现180°移相就可以,恰好,当C1,C2,Y1形成谐振时,能够实现180移相,这个大家可以解方程等,把Y1当作一个电感来做。也可以用电容电感的特性,比如电容电压落后电流90°,电感电压超前电流90°来分析,都是可以的。当C1增大时,C2端的振幅增强,当C2降低时,振幅也增强。有些时候C1,C2不焊也能起振,这个不是说没有C1,C2,而是因为芯片引脚的分布电容引起的,因为本来这个C1,C2就不需要很大,所以这一点很重要。

接下来分析这两个电容对振荡稳定性的影响。因为5404的电压反馈是靠C2的,假设C2过大,反馈电压过低,这个也是不稳定,假设C2过小,反馈电压过高,储存能量过少,容易受外界干扰,也会辐射影响外界。C1的作用对C2恰好相反。因为我们布板的时候,假设双面板,比较厚的,那么分布电容的影响不是很大,假设在高密度多层板时,就需要考虑分布电容。

有些用于工控的项目,建议不要用无源晶振的方法来起振,而是直接接有源晶振。也是主要由于无源晶振需要起振的原因,而工控项目要求稳定性要好,所以会直接用有源晶振。在有频率越高的频率的晶振,稳定度不高,所以在速度要求不高的情况下会使用频率较低的晶振。

-

74hc14与74hc04的区别2023-08-18 9124

-

晶体振荡器是什么2021-08-09 5687

-

【转帖】晶体起振的影响条件有哪些,又是如何保持震荡?2018-06-06 3258

-

74ls04和74hc04有什么区别_74ls04/74hc04简介2018-04-08 30022

-

石英晶体振荡电路,仿真输出的频率怎么是固定的,不应该与晶振的频率一致吗?2018-03-23 4603

-

由74HC04组成的并联谐振振荡电路2017-12-04 8130

-

74HC04英文手册2016-11-02 1998

-

晶体振荡电路设计_CN2015-12-25 1094

-

晶体振荡电路 求助!!2015-03-16 3347

-

振荡IC有效实现时钟晶振高精度和高稳定度2013-11-08 2355

-

有人懂晶体振荡电路吗?2011-12-13 4730

-

晶体振荡电路的设计方法2010-04-28 11107

-

晶体振荡电路的设计2009-06-28 12554

-

555晶体振荡电路2008-05-19 2189

全部0条评论

快来发表一下你的评论吧 !