ADC采样控制电路的设计与实现

电源设计应用

描述

什么是ADC

ADC,Analog-to-Digital Converter的缩写,指模/数转换器或者模数转换器。是指将连续变化的模拟信号转换为离散的数字信号的器件。真实世界的模拟信号,例如温度、压力、声音或者图像等,需要转换成更容易储存、处理和发射的数字形式。模/数转换器可以实现这个功能,在各种不同的产品中都可以找到它的身影。

与之相对应的DAC,Digital-to-Analog Converter,它是ADC模数转换的逆向过程。

ADC最早用于对无线信号向数字信号转换。如电视信号,长短播电台发接收等。

数字输出选择

1.高端仪表促进了更快的ADC速度和更多的通道数与密度,设计者必须评估转换器的输出格式,以及基本的转换性能。

2.主要的输出选项是CMOS(互补金属氧化物半导体)、LVDS(低压差分信令),以及CML(电流模式逻辑)。

3.要考虑的问题包括:功耗、瞬变、数据与时钟的变形,以及对噪声的抑制能力。

4.对于布局的考虑也是转换输出选择中的一个方面,尤其当采用LVDS技术时。

当设计者有多种ADC选择时,他们必须考虑采用哪种类型的数字数据输出:CMOS(互补金属氧化物半导体)、LVDS(低压差分信令),还是CML(电流模式逻辑)。ADC中所采用的每种数字输出类型都各有优缺点,设计者应结合自己的应用来考虑。这些因素取决于ADC的采样速率与分辨率、输出数据速率,以及系统设计的功率要求,等等。

ADC0809采样控制电路设计

一、实验目的

学习用状态机实现A/D转换器ADC0809的采样控制电路。

二、实验内容

利用QuartusⅡ实现A/D转换器ADC0809的采样控制电路状态机设计;给出仿真波形。最后进行引脚锁定并进行测试,硬件验证设计电路对ADC0809的控制功能。

三、实验仪器与器材

计算机1台,GW48-PK2S实验箱1台,QuartusⅡ6.0 1套。

四、实验

用VHDL 设计的状态机的一般结构有以下几部分组成:

1. 说明部分

说明部分中有新数据类型TYPE 的定义及其状态类型(状态名)和在此新数据类型下定义的状态变量。状态类型一般用枚举类型,其中每一个状态名可任意选取。但为了便于辨认和含义明确,状态名最好有明显的解释性意义。状态变量应定义为信号,便于信息传递。说明部分一般放在ARCHITECTURE 和BEGIN之间。

2. 主控时序进程:

状态机是随外部时钟信号以同步时序方式工作的,因此状态机中必须包含一个对工作时钟信号敏感的进程作为状态机的“驱动泵”。当时钟发生有效跳变时,状态机的状态才发生变化。状态机的下一状态(包括再次进入本状态)仅仅取决于时钟信号的到来。一般地,主控时序进程不负责进入的下一状态的具体状态取值。当时钟的有效跳变到来时,时序进程只是机械地将代表下一状态的信号next_state 中的内容送入代表本状态的信current_state 中,而信号next_state 中的内容完全由其它的进程根据实际情况来决定。当然此进程中也可以放置一些同步或异步清零、置位方面的控制信号。总体来说,主控时序进程的设计比较固定、单一和简单。

3. 主控组合进程:

主控组合进程的任务是根据外部输入的控制信号(包括来自状态机外部的信号和来自状态机内部其它非主控的组合或时序进程的信号),或(和)当前状态的状态值确定下一状态(next_state)的取向,即next_state的取值内容,以及确定对外输出或对内部其它组合或时序进程输出控制信号的内容。

4. 普通组合进程

用于配合状态机工作的其它组合进程,如为了完成某种算法的进程。

5. 普通时序进程

用于配合状态机工作的其它时序进程,如为了稳定输出设置的数据锁存器等。一个状态机的最简结构应至少由两个进程构成(也有单进程状态机,但并不常用)即一个主控时序进程和一个主控组合进程,一个进程作“驱动泵”,描述时序逻辑,包括状态寄存器的工作和寄存器状态的输出;另一个进程描述组合逻辑,包括进程间状态值的传递逻辑以及状态转换值的输出。当然必要时还可以引入第3 个和第4 个进程,以完成其它的逻辑功能。

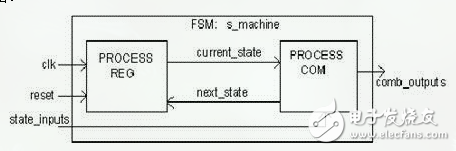

从一般意义上说进程间是并行运行的,但由于敏感信号的设置不同以及电路的延迟,在时序上进程间的动作是有先后的。在设计中,如果希望输出的信号具有寄存器锁存功能,则需要为此输出写第3 个进程,并把clk 和reset信号放入敏感信号表中。用于进程间信息传递的信号current_state 和next_state ,在状态机设计中称为反馈信号。状态机运行中,信号传递的反馈机制的作用是实现当前状态的存储和下一个状态的译码设定等功能。在VHDL中可以有两种方式来创建反馈机制,即使用信号的方式和使用变量的方式,通常倾向于使用信号的方式。附图8-1为一般状态机结构图。

图8-1 一般状态机结构框图工作示意图

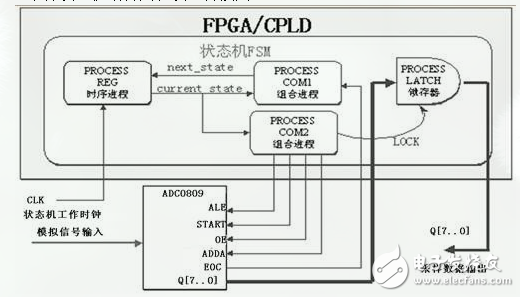

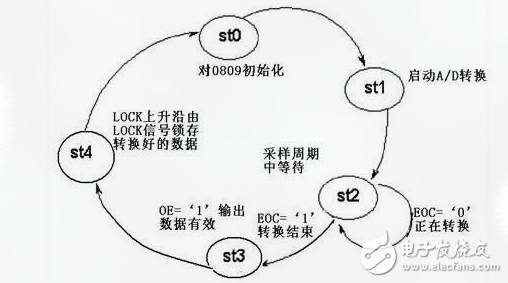

附图8-2和8-3为控制ADC0809采样状态机结构图和状态转换图

图8-2 采样状态机结构框图

设计提示:

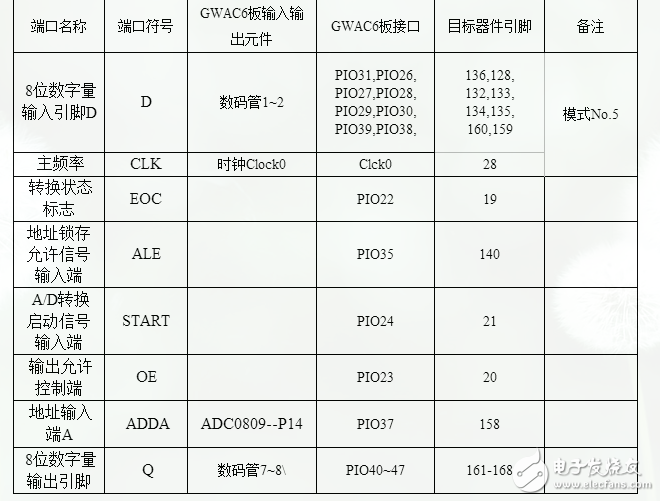

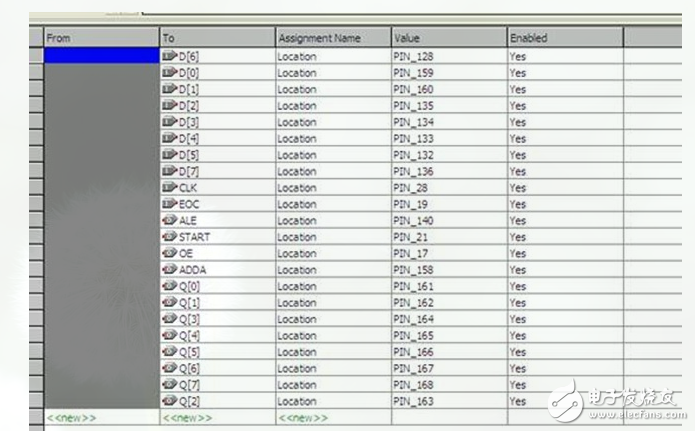

设目标器件是EP1C6Q240C8,建议选择实验电路结构图No.5(即结构图No.5A,附图1-14,由该图可见,ADC0809的转换时钟CLK已经事先接有750KHz的频率),将实验系统左下角选择插针处的“转换结束”和“A/D使能”用跳线帽短接。下载目标文件后,可用螺丝刀旋转实验系统左下角的电位器,以便为ADC0809提供变化的待测模拟信号,这时数码管8和7将显示ADC0809采样输出并被锁存的数字值(16进制)。

图8-3 控制ADC0809采样状态图

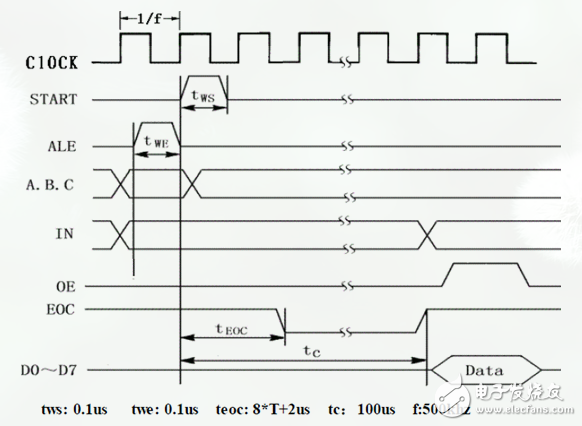

图8-4 控制ADC0809采样时序图

五、实验要求

根据以上的实验内容写出实验报告,包括程序设计、软件编译、仿真分析、硬件测试和实验过程;设计程序、程序分析报告、仿真波形图及其分析报告。

1. 设计思路

6. 由题意知,我们要设计一个电路与A/D转换器ADC0809相连,通过接受时钟输入来决定状态,通过对不同状态输出不同的控制信号,实现对ADC0809的采样控制,最终输出稳定的采样电压。本实验中将设计如下进程。

设置两个信号Current_State、Next_State,以便实现状态的通知。

① 主控时序进程REG

总体设计思想:用REG控制整个采样控制电路的状态,是整个电路的总指挥。

通过监测ADC0809输出的信号,实现不同状态的转换,进而控制不同不同的进程Process。

主控时序进程REG只输出状态,只接收ST1。

当状态为ST0的时候,开始新一轮的采样;

当接收ST1的时候,通知COM2将采样数据锁存,输出。

进程REG对信号:CLK、Next_State信号敏感

② 组合进程COM1

总体设计思想:用COM1实现COM2对REG的通知,是整个电路的传令兵;用COM2控制整个电路,是整个电路状态改变的具体执行者。

。

当EOC=1的时候,通知REG,以便改变电路状态。

进程COM1对信号Current_State和EOC敏感

③ 进程LATCH

总体设计思想:用LATCH来锁存转换好的数据,并控制数据的输出。

进程LATCH对信号LOCK,REGL敏感

程序设计

LIBRARYIEEE;

USEIEEE.STD_LOGIC_1164.ALL;

ENTITY ADCINT IS

PORT(D :INSTD_LOGIC_VECTOR(7DOWNTO0);--来自0809转换好的8位数据

CLK:INSTD_LOGIC; --状态机工作时钟

EOC:INSTD_LOGIC; --转换状态指示,低电平表示正在转换

ALE:OUTSTD_LOGIC; --8个模拟信号通道地址锁存信号

START:OUTSTD_LOGIC; --转换开始信号

OE:OUTSTD_LOGIC; --数据输出3态控制信号

ADDA:OUTSTD_LOGIC; --信号通道最低位控制信号

LOCK0:OUTSTD_LOGIC; --观察数据锁存时钟

LED:OUTSTD_LOGIC; --用来指示仿真程序是否正确

-- LED2: OUT STD_LOGIC; --2用来指示仿真程序是否正确

Q :OUTSTD_LOGIC_VECTOR(7DOWNTO0)--8位数据输出

);

END ADCINT;

ARCHITECTURE behav OF ADCINT IS

TYPE states IS(st0,st1,st2,st3,st4); --定义各状态子类型

SIGNAL current_state , next_state : states := st0;

SIGNAL REGL :STD_LOGIC_VECTOR(7DOWNTO0);

SIGNAL LOCK :STD_LOGIC; --转换后数据输出锁存时钟信号

BEGIN

ADDA 《= ‘1’;--当ADDA《=‘0’,模拟信号进入通道IN0,当ADDA《=‘1’,则进入通道IN1

Q 《= REGL; LOCK0 《= LOCK;

------------------进程REG---------------------

--用REG控制整个采样控制电路的状态,是整个电路的总指挥。

PROCESS(CLK)

BEGIN

IF CLK=‘1’ and CLK‘eventTHEN -- 检测时钟上升沿

--LED《=’0‘;

IF next_state=st0 THEN -- 初始化状态机

current_state《=st0;

ELSIF next_state=st1 THEN --开始转换(st1)

current_state《=st1;

ELSIF next_state=st2 THEN --等待转化完毕,检测EOC是否为高电平

current_state《=st2;

ELSIF next_state=st3 THEN

-- LED《=’1‘;

current_state《=st3;

ELSIF next_state=st4 THEN

current_state《=st4;

ENDIF;

ENDIF;

ENDPROCESS;

------------------进程COM2---------------------

--用COM2控制整个电路,是整个电路状态改变的具体执行者。

PROCESS(current_state,EOC)

VARIABLE First_EOC :STD_LOGIC;

BEGIN

--LED2《=’0‘;

IF current_state=st0 THEN -- 初始化状态机

ALE《=’1‘;

START《=’0‘;

OE《=’0‘;

LOCK《=’0‘;

next_state《=st1;

ELSIF current_state=st1 THEN --开始转换(st1)

START《=’1‘;

ALE《=’0‘;

--IF EOC=’0‘ THEN -- 转换结束

next_state《=st2;

First_EOC:=EOC;--在状态1记录EOC,以便后面判断AD是否开始转换

--END IF;

ELSIF current_state=st2 THEN --等待转化完毕,检测EOC是否为高电平

START《=’0‘;

OE《=’0‘;

if ’1‘=(First_EOC XOR EOC)then

IF EOC=’1‘ THEN

-- IF EOC=’1‘ THEN

next_state《=st3;

-- END IF;

-- else

-- next_state《=st2;

ENDIF;

else

next_state《=st2;

ENDIF;

ELSIF current_state=st3 THEN

--LED2《=’1‘;

IF EOC=’1‘ THEN -- 转换结束

OE《=’1‘;

next_state《=st4;

ELSE

OE《=’0‘;

ENDIF;

ELSIF current_state=st4 THEN

OE《=’0‘;

LOCK《=’1‘;

next_state《=st0; --开启下一轮新的转换

ENDIF;

ENDPROCESS;

------------------进程LATCH---------------------

--用来控制电路的输出

PROCESS(LOCK,REGL)

VARIABLE cq :std_logic_vector(7DOWNTO0);--用来保存数值

BEGIN

IF LOCK=’0‘ THEN

cq:=D;

ELSIF LOCK=’1‘ THEN

REGL《=cq;

ENDIF;

ENDPROCESS;

ENDARCHITECTURE behav;

2. 仿真分析

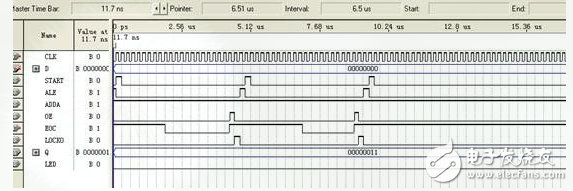

图8-5 仿真波形图

由8-5可知,仿真波形和图8-4控制ADC0809采样时序图一致。

3. 硬件测试和实验过程

表1-1 ADCINT在GWAC6板上目标芯片EP1C6Q240C8的引脚锁定信息

- 相关推荐

- 热点推荐

- ADC采样

-

ADC多次采样的实现思路2022-09-09 3196

-

连续信号控制电路教程2009-12-06 8158

-

电流控制电路2022-06-13 12259

-

控制电路图2009-07-17 4248

-

高音控制电路2009-10-09 3054

-

舵机反馈采样控制电路的设计及应用2012-06-11 1146

-

双环电流控制型PWM控制电路的谐波补偿与实现2017-09-11 768

-

基于FPGA的ADC0809控制电路2017-11-28 12481

-

FPGA如何实现对高速AD转换芯片的控制电路2018-09-21 2123

-

AN-1388: 使用AD7779 24位同步采样Σ-型ADC实现电能质量测量的相干采样2021-03-20 1081

-

用状态机设计A_D转换器ADC0809的采样控制电路实验2021-09-16 1240

-

利用FPGA控制ADC0809采样电压2021-09-28 1738

-

控制电路和工作电路的区别和联系2023-04-23 5651

-

运用 DMA 功能实现高级定时器和 ADC 的同步触发采样2022-06-06 1319

-

航空电源逆变控制电路设计与实现2023-11-08 583

全部0条评论

快来发表一下你的评论吧 !