基于专用数字下变频芯片GC5016的宽/窄带数据下变频系统设计及数据分析与解调

RF/无线

描述

数字下变频是无线通信链路层的重要组成部分,宽带信号和窄带信号的下变频由于信号带宽不同而抽取因子不同,使得同时具有宽带和窄带信号的系统采用基于FPGA的系统很难实现。本文提出采用专用数字下变频率芯片GC5016同时实现宽带和窄带信号的变频;采用FPGA实现对宽/窄带数据的接收和存储,存储后数据使用高性能DSP芯片C6455实现对这些数据的处理。文中详细介绍了该系统的软硬件设计方法。

引言

随着电子技术和信号处理技术的发展,宽带数据的应用越来越多,同时窄带数据通信也仍然广泛存在。同时对宽带和窄带数据进行处理是目前无线通信遇到的问题。由于数字接收机系统中,宽带和窄带数据的需求不是事先固定的,而是在信号分析和识别后,自适应地或者由用户现场下发命令,实现宽带或者窄带信号的监测。 在这种应用背景下,基于FPGA的数字下变频就面临现场编程问题,一般FPGA解决方法是将各种带宽的参数存储在其FLASH芯片中,随时根据命令来调用 不同带宽下的工作参数,但需要的存储空间较大,占用FPGA的资源也较多,基于此方法设计的系统需要大容量的FPGA芯片,系统的功耗较大,价格较高。

为此,本文提出一种基于专用数字下变频芯片GC5016的宽/窄带数据下变频解决方案,使用小规模FPGA实现对GC5016输出数据的读取和存储,应用高性能DSP芯片C6455实现对下变频后数据的分析和解调。

1 GC5016及其结构

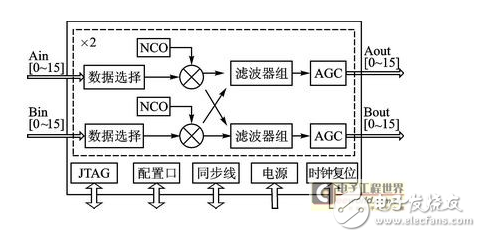

GC5016是TI公司推出的宽带4通道的可编程数字上下变频器,提供160 Msps输入速率,可以采用双通道联合处理最高320 Msps的输入速率,满足目前绝大部分A/D器件的速率要求。4个完全相同的通道可以独立配置成上变频、下变频或两个上变频、两个下变频的组合通道。本文 主要介绍其下变频功能。GC5016的内部结构如图1所示。图中给出了GC5016在接收工作模式下的结构图,其内部有4个通道,图中给出了A和B两个通 道的结构图,通道C和D具有和这两个通道完全一致的结构。

图1 GC5016内部结构图

输入数据经过数据选择单元进入混频器,数据选择格式有定点16位、浮点16位以及AB双路合成数据3种格式。数字混频器将按照软件配置对信号进行混频,为了便于后面的滤波,一般转换到零频为中心的基带数据。基带数据可以两路合成分别经过滤波器, 也可以每路单独进行滤波。滤波器组包括CIC滤波器和可编程滤波器:CIC滤波器可以实现1~256的整数抽取,降低了数据速率;可编程滤波器一般使用 FIR滤波器,对信号进一步抽取和整形,这里抽取可以为1~16,可见GC5016可以实现最大的抽取为4 096(16 256)。FIR滤波后的数据经过AGC功率检测和控制模块,数据最后经过输出格式化后输出。

图中配置口是一个并行数据接口,必须经过这个接口配置GC5016的寄存器,也可以通过配置口来读取芯片的寄存器,查看芯片工作是否正常、初始化是 否正确等;GC5016具有一个同步输入和同步输出口,可以用于多个GC5016的同步,也可以用于单个芯片内几个通道的同步;JTAG口用于芯片的测试,用户一般不需要连接;电源和时钟复位接口是芯片正常工作的基本配置。

2 硬件系统设计

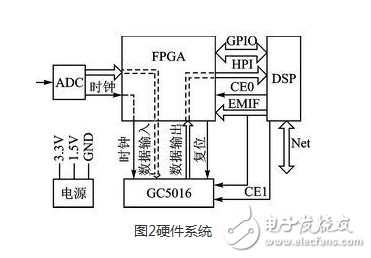

硬件系统主要由ADC、GC5016、FPGA和DSP组成,如图2所示。

图2 硬件系统

模/数转换芯片ADC采用ADI公 司的16位芯片AD9467,其采样频率高达200 MHz,具有75 dB的SNR和90 dB的SFDR,是一款性能较高的高速ADC。其对外接口是差分LVDS数据和时钟总线,差分输出不能直接连接到GC5016,需要采用FPGA将差分信 号转换成单端信号。FPGA以ADC输出的差分时钟为基准时钟对差分数据进行读取和转换,将处理好的单端信号数据仍然在该时钟基准下输出给GC5016。 由于FPGA的差分端口是相对应的,因此连接ADC的差分数据线和差分时钟线要注意不能随便连接,尽量安排在FPGA的同一Bank中,否则可能导致传输 路径不一致,在高速数据读写下容易产生相位畸变,使得输入和传输数据错误。

DSP和FPGA之间的数据通过HPI接口,由FPGA写入DSP,节省DSP的数据读写时间。DSP和FPGA之间还有EMIF接口,用于DSP 对FPGA的控制,DSP和FPGA之间的控制状态由GPIO总线传输。同时,DSP还连接一个EMIF接口到GC5016,用于DSP对GC5016的 控制和状态读取。

3 软件设计

3.1 GC5016的控制寄存器设置

GC5016的控制寄存器被划分为两部分:8个全局寄存器和总共88页的寄存器,每个页包含了16个寄存器。全局寄存器的访问地址是 0x00~0x0F。页寄存器的访问地址需先在全局寄存器的地址2写入页地址,然后再访问0x10~0x1F,就可以访问该页下的寄存器。每一个控制寄存 器在芯片内被分配唯一的地址。这样接口的设计就可以将GC5016作为处理器的一个外部存储器来访问。

3.2 GC5016的初始化

GC5016的初始化根据电路的不同可以分为三种情况:第一种是单个GC5016芯片,第二种是多个GC5016芯片配置由主GC5016芯片同 步,第三种是多个GC5016芯片配置由外部源同步。而此次设计中只用一块GC5016进行宽带下变频的验证,所以属于独立GC5016芯片的配置。其配 置步骤如下:

① 写0xFF00到地址0,复位芯片。

② 写0x0000到地址3,禁止所有输出。

③ 写0x0004到地址1,产生单触发脉冲。

④ 装载所有的配置寄存器。

⑤ 如果几个通道需要同步控制,需要选择一个同步源,可以通过在输入文件中加入如下程序来实现同步控制:

soB_sync 4; fir_sync 4; sck_sync 4; nco_sync4; cic_sync 4;

⑥ 写0x0100到地址0,清除复位。

⑦ 写0x0004到地址1,产生同步脉冲,完成GC5016的设置。

3.3 GC5016的cmd5016软件应用

可以使用专门提供的GC5016的配置软件实现对其寄存器的设置。这些配置包括以下内容。

(1) 关键字的类型

关键字的类型,共5种,分别是mandatory(M)、defaulted(D)、computed(C)、unused(X)、 expert(E)。其中M是需要用户进行选择的变量,D是初始化默认值,C是软件控制的变量,X是不用的变量,E一般是一个计算变量,不需要人为设置。

(2) 伪指令

在配置文件中,伪指令mode AB receive 和mode CD receive 可以使GC5016工作在4通道DDC模式。在此模式下需要设置的伪指令有:

◆ mode AB(CD) receive(定义DDC收发模式);

◆ rin_rate(全局变量,接收输入数据速率,0代表半速率,1代表全速率,2代表双速率);

◆ rin_cmplx(全局变量,接收输入数据,0为接收的为实数数据,1为接收的为复数数据);

◆ splitiq,splitiqAB,splitipCD(两通道或者4通道模式变量);

◆ freq,fck,bypass_mix(复数混频器freq_msb,freq_mid,freq_lsb的设置);

◆ bypass_cic,cic_dec(双CIC滤波器的抽取因子);

◆ bypass_fir,fir_dec,fir_diff,fir_nchan,fir_coef(PFIR模式和滤波器抽头);

◆ gain,overall_gain(手动增益设置);

◆ agc_cf,agc_mode,agc_tc(AGC增益设置);

◆ pwr_mtr_on(接收功率计设置);

◆ routf_tdm(接收输出格式控制通道D的TDM模式)。

3.4 DSP软件流程

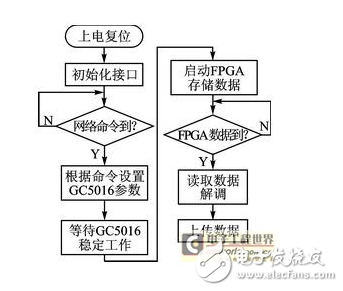

系统的DSP软件流程如图3所示。

DSP上电复位后,初始化相关接口,这些接口包括EMIF接口、HPI接口以及网络和 GPIO接口。初始化接口后,DSP等待从网口下发的控制命令,控制命令一般包括解调频率、解调带宽和解调方式等各种信息。DSP根据这些信息设置 GC5016的寄存器,并将这些寄存器值写入GC5016,使得GC5016可以正常工作,然后启动FPGA采集GC5016输出的数据,FPGA按照 1024个数据一帧进行存储,满一帧后通知DSP读取这些数据,DSP对这些数据解调后输出到上位机显示或者存储。

图3 DSP软件流程

结语

GC5016是一种理想的可编程4通道数字上下变频器,根据需要可配置为两路作为上变频、两路作为下变频。当接收或发射的数据量庞大时,还可以使用 多块GC5016并行处理。再加上它的高速率、宽带宽、高无杂散动态范围、低功耗和灵活配置等各种优点,使得GC5016的应用非常广泛,在CDMA/WCDMA、雷达及软件无线电中都有强大的生命力和很好的发展前景。

-

【设计进展】数字下变频模块2012-06-06 3924

-

基于fgpa的数字正交下变频2014-04-01 4741

-

下变频的设计问题2015-09-20 2725

-

数字下变频2017-02-15 4720

-

基于FPGA的高速数字下变频系统该怎么设计?2019-09-26 2837

-

请问怎样去设计一种GC5016的数字上下变频系统?2021-05-24 1602

-

数字下变频的FPGA实现2009-11-30 976

-

基于新型FPGA实现高速数字下变频2010-07-02 584

-

GC5016,pdf(Wideband Quad Digit2010-07-08 1078

-

基于GC5016的数字直放站设计2008-10-13 1226

-

数字下变频器GC4016及其在软件无线电中的应用2011-09-28 3260

-

基于FPGA的DDC数字下变频设计2016-04-27 986

-

myddc数字下变频程序2017-08-30 1247

-

基于FPGA的数字下变频器的设计与实现2017-11-22 6974

-

基于FPGA的数字下变频器(DDC)的设计2021-09-16 1397

全部0条评论

快来发表一下你的评论吧 !