74ls373和74hc573有什么区别

功率器件

描述

74ls373和74hc573都是八D锁存器(三态)。74ls373是TTL电路,电源电压是5V。74hc573是cmos电路,电源电压工作范围是2V ~ 6V。74ls373和74hc573的引脚编排不一样。

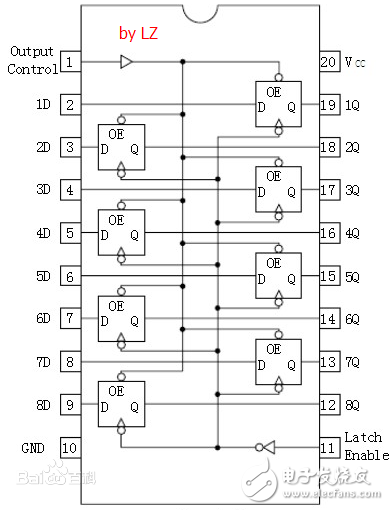

一、锁存器74hc573

74HC573是拥有八路输出的透明锁存器,输出为三态门,是一种高性能硅栅CMOS器件。SL74HC573跟LS/AL573的管脚一样。器件的输入是和标准CMOS输出兼容的,加上拉电阻他们能和LS/ALSTTL输出兼容。

当锁存使能端LE为高时,这些器件的锁存对于数据是透明的(也就是说输出同步)。当锁存使能变低时,符合建立时间和保持时间的数据会被锁存。

·I/O输出能直接接到 CMOS,NMOS 和 TTL 接口上·

工作电压范围:2.0V~6.0V·

最低输入电流:1.0uA·

器件的高噪声抵抗特性·三态总线驱动输出

置数全并行存取

缓冲控制输入

使能输入有改善抗扰度的滞后作用

编程时:

1.使能端置1,此时输出数据和输入数据一致;

2.使能端清0,输出端保持原有值,使得输出的数据锁定,防止误操作。

真值表及功能:

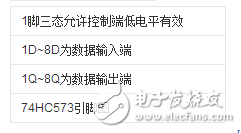

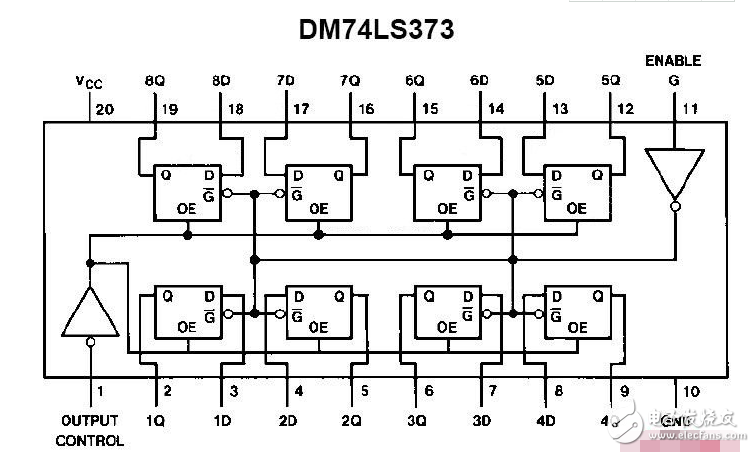

二、74ls373

74LS373是一款常用的地址锁存器芯片,由八个并行的、带三态缓冲输出的D触发器构成。在单片机系统中为了扩展外部存储器,通常需要一块74LS373芯片。

(1).1脚是输出使能(OE),是低电平有效,当1脚是高电平时,不管输入3、4、7、8、13、14、17、18如何,也不管11脚(锁存控制端,G)如何,输出2(Q0)、5(Q1)、6(Q2)、9(Q3)、12(Q4)、15(Q5)、16(Q6)、19(Q7)全部呈现高阻状态(或者叫浮空状态);

(2)。当1脚是低电平时,只要11脚(锁存控制端,G)上出现一个下降沿,输出2(Q0)、5(Q1)、6(Q2)、9(Q3)、12(Q4)、15(Q5)、16(Q6)、19(Q7)立即呈现输入脚3、4、7、8、13、14、17、18的状态。

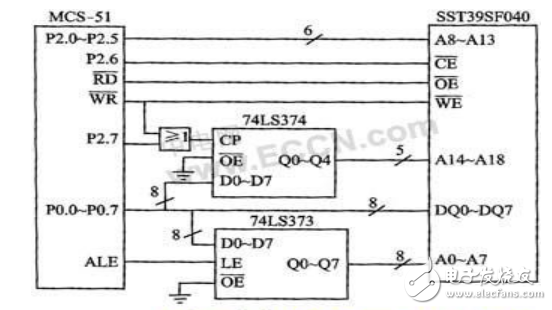

锁存端LE 由高变低时,输出端8 位信息被锁存,直到LE 端再次有效。 当三态门使能信号OE为低电平时,三态门导通,允许Q0~Q7输出,OE为高电平时,输出悬空。当74LS373用作地址锁存器时,应使OE为低电平,此时锁存使能端C为高电平时,输出Q0~Q7 状态与输入端D1~D7状态相同;当C发生负的跳变时,输入端D0~D7 数据锁入Q0~Q7。51单片机的ALE信号可以直接与74LS373的C连接。 74ls373与单片机接口:

1D~8D为8个输入端。1Q~8Q为8个输出端。

G是数据锁存控制端;当G=1时,锁存器输出端同输入端;当G由“1”变为“0”时,数据输入锁存器中。

OE为输出允许端;当OE=“0”时,三态门打开;当OE=“1”时,三态门关闭,输出呈高阻状态。

在MCS-51单片机系统中,常采用74LS373作为地址锁存器使用,其连接方法如上图所示。其中输入端1D~8D接至单片机的P0口,输出端提供的是低8位地址,G端接至单片机的地址锁存允许信号ALE。输出允许端OE接地,表示输出三态门一直打开

三、LS与HC的区别

1、 LS是低功耗肖特基,HC是高速COMS。LS的速度比HC略快。HCT输入输出与LS兼容,但是功耗低;F是高速肖特基电路;

2、 LS是TTL电平,HC是COMS电平

3、 LS输入开路为高电平,HC输入不允许开路, hc 一般都要求有上下拉电阻来确定输入端无效时的电平。LS 却没有这个要求

4、 LS输出下拉强上拉弱,HC上拉下拉相同。

5、 工作电压不同,LS只能用5V,而HC一般为2V到6V;

6、电平不同。LS是TTL电平,其低电平和高电平分别为0.8和V2.4,而CMOS在工作电压为5V时分别为0.3V和3.6V,所以CMOS可以驱动TTL,但反过来是不行的

7、驱动能力不同,LS一般高电平的驱动能力为5mA,低电平为20mA;而CMOS的高低电平均为5mA;

8、 CMOS器件抗静电能力差,易发生栓锁问题,所以CMOS的输入脚不能直接接电源。

-

74ls373引脚图及功能 74ls373是什么芯片2021-07-08 76283

-

74hc573和74hc595有什么不同?该怎样区分74hc573和74hc5952018-07-27 29072

-

74hc573怎么使用 74hc573可以仿真吗2018-07-26 17884

-

74ls04和74hc04有什么区别_74ls04/74hc04简介2018-04-08 29699

-

74hc573是什么_74hc573封装2017-11-27 15482

-

74hc574和74hc573区别2017-10-24 50093

-

74LS373锁存器资料2016-04-12 2029

-

74HC573功能说明2016-03-23 1456

-

使用2个74hc573加2个74ls138驱动四个***数码管的问题2014-11-13 3994

-

74hc573中文资料pdf2012-10-09 13584

-

74ls373使用2012-08-18 3362

-

74HC5732012-08-17 2407

-

74ls373引脚图2008-03-16 11382

全部0条评论

快来发表一下你的评论吧 !