利用降频和Burst Mode方法在提高待机效率并考虑出现的问题

电源设计应用

描述

随着能源效率和环保的日益重要,人们对开关电源待机效率期望越来越高,客户要求电源制造商提供的电源产品能满足BLUE ANGEL,ENERGY STAR, ENERGY 2000等绿色能源标准,而欧盟对开关电源的要求是:到2005年,额定功率为0.3W~15W,15W~50W和50W~75W的开关电源,待机功耗需分别小于0.3W,0.5W和0.75W。而目前大多数开关电源由额定负载转入轻载和待机状态时,电源效率急剧下降,待机效率不能满足要求。这就给电源设计工程师们提出了新的挑战。

2、开关电源功耗分析

要减小开关电源待机损耗,提高待机效率,首先要分析开关电源损耗的构成。以反激式电源为例,其工作损耗主要表现为:MOSFET导通损耗

开关交叠损耗,PWM控制器及其启动电阻损耗,输出整流管损耗,箝位保护电路损耗,反馈电路损耗等。其中前三个损耗与频率成正比关系,即与单位时间内器件开关次数成正比。

在待机状态,主电路电流较小,MOSFET导通时间ton很小,电路工作在DCM模式,故相关的导通损耗,次级整流管损耗等较小,此时损耗主要由寄生电容损耗和开关交叠损耗和启动电阻损耗构成。

3、提高待机效率的方法

根据损耗分析可知,切断启动电阻,降低开关频率,减小开关次数可减小待机损耗,提高待机效率。具体的方法有:降低时钟频率;由高频工作模式切换至低频工作模式,如准谐振模式(Quasi Resonant,QR)切换至脉宽调制(Pulse Width Modulation,PWM), 脉宽调制切换至脉冲频率调制(Pulse Frequency Modulation, PFM);可控脉冲模式(Burst Mode)。

3.1 切断启动电阻

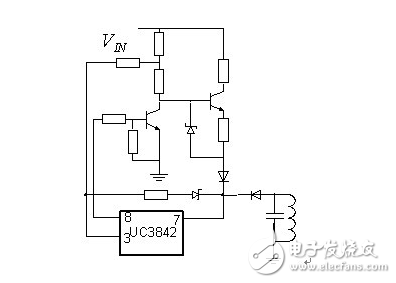

对于反激式电源,启动后控制芯片由辅助绕组供电,启动电阻上压降为300V左右。设启动电阻取值为47kΩ,消耗功率将近2W。要改善待机效率,必须在启动后将该电阻通道切断。TOPSWITCH,ICE2DS02G内部设有专门的启动电路,可在启动后关闭该电阻。若控制器没有专门启动电路,也可在启动电阻串接电容,其启动后的损耗可逐渐下降至零。缺点是电源不能自重启,只有断开输入电压,使电容放电后才能再次启动电路。而图1所示的启动电路,则可避免以上问题,而且该电路功耗仅为0.03W。不过电路增加了复杂度和成本。

图1 UC3842反激式电源启动电路

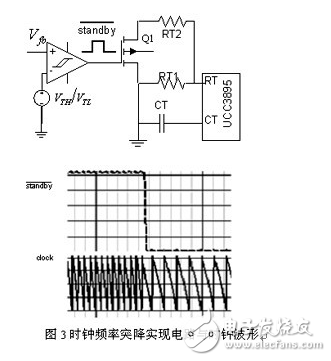

3.2 降低时钟频率

时钟频率可平滑下降或突降。平滑下降就是当反馈量超过某一阈值,通过特定模块,实现时钟频率的线性下降。POWER公司的TOPSwitch-GX和SG公司的SG6848芯片内置了这样的模块,能根据负载大小调节频率,图2所示是SG6848时钟频率与其反馈电流的关系。

即开关频率减小。开关损耗降为降频前的

(小于1)倍。L5991和Infineon公司的CoolSet F2系列已经集成了该功能。

3.3 切换工作模式

3.3.1 QR→PWM

IRIS40xx芯片就是通过QR与PWM切换来提高待机效率的。图4是IRIS4015构成的反激式开关电源,重载时,辅助绕组电压大,R1分压大于0.6V,Q1导通,辅助准谐振信号经过D1,D2,R3,C2构成的延时电路到达IRIS4015的FB脚,内部比较器对该信号进行比较,电路工作在准谐振模式。当电源处于轻载和待机时候,辅助绕组电压较小,Q1关断,谐振信号不能传输至FB端,FB电压小于芯片内部的一个门限电压,不能触发准谐振模式,电路则工作在更低频的脉宽调制控制模式。

图4 由IRIS4015构成的QR/PWM反激式电源电路

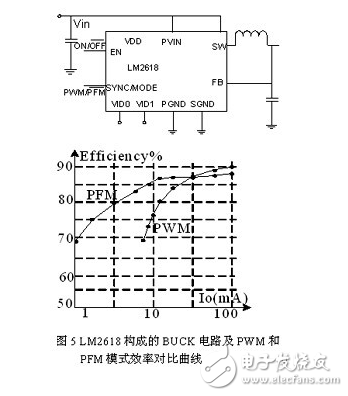

3.3.2 PWM→PFM

对于额定功率时工作在PWM模式的开关电源,,也可以通过切换至PFM模式提高待机效率,即固定开通时间,调节关断时间,负载越低,关断时间越长,工作频率也越低。图5是采用NS公司的LM2618控制的Buck转换器电路和分别采用PWM和PFM控制方法的效率比较曲线。由图可见,在轻载时采用PFM模式的电源效率明显大于采用PWM模式时的效率,且负载越低,PFM效率优势越明显。将待机信号加在其PW/引脚上,在额定负载条件下,该引脚为高电平,电路工作在PWM模式,当负载低于某个阈值时,该引脚被拉为低电平,电路工作在PFM模式。实现PWM和PFM的切换,也就提高了轻载和待机状态时的电源效率。

通过降低时钟频率和切换工作模式实现降低待机工作频率,提高待机效率,可保持控制器一直在运作,在整个负载范围中,输出都能被妥善的调节。即使负载从零激增至满负载的情况下,能够快速反应,反之亦然。输出电压降和过冲值都保持在允许范围内。

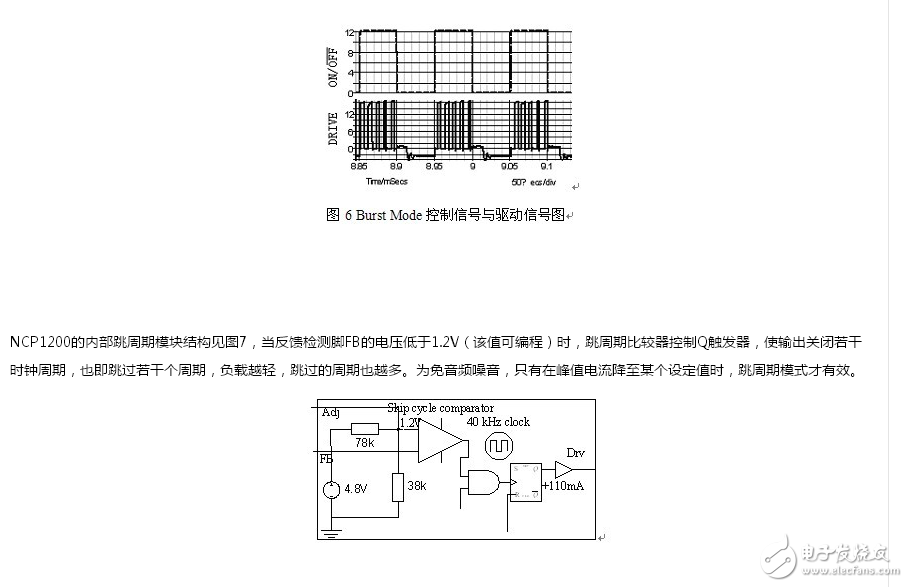

3.4可控脉冲模式(Burst Mode)

可控脉冲模式,也可称为跳周期控制模式(Skip Cycle Mode)是指当处于轻载或待机条件时,由周期比PWM控制器时钟周期大的信号控制电路某一环节,使得PWM的输出脉冲周期性的有效或失效,如图6所示。这样即可实现恒定频率下通过减小开关次数,增大占空比来提高轻载和待机的效率。该信号可以加在反馈通道,PWM信号输出通道,PWM芯片的使能引脚(如LM2618,L6565)或者是芯片内部模块(如NCP1200,FSD200,L6565和TinySwitch系列芯片)。

图7 NCP1200跳周期模块结构

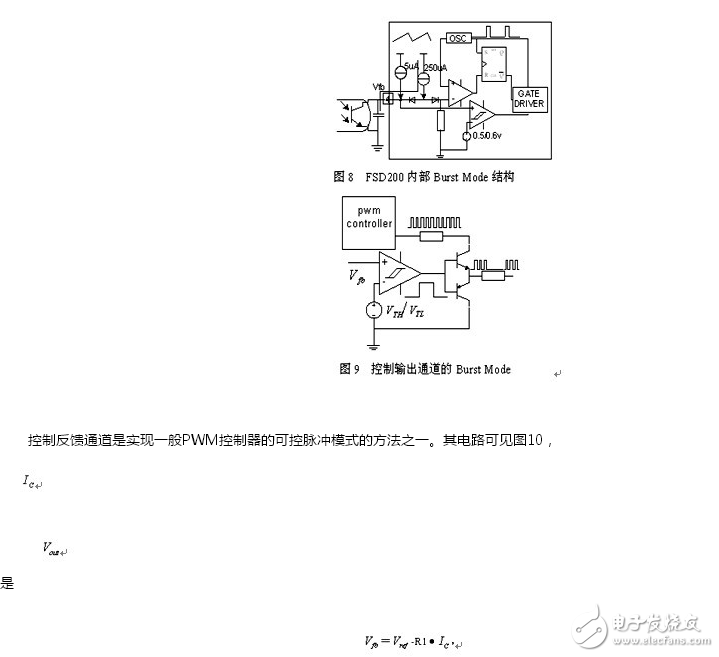

而FSD200则是通过控制内部驱动器实现可控脉冲模式,即将

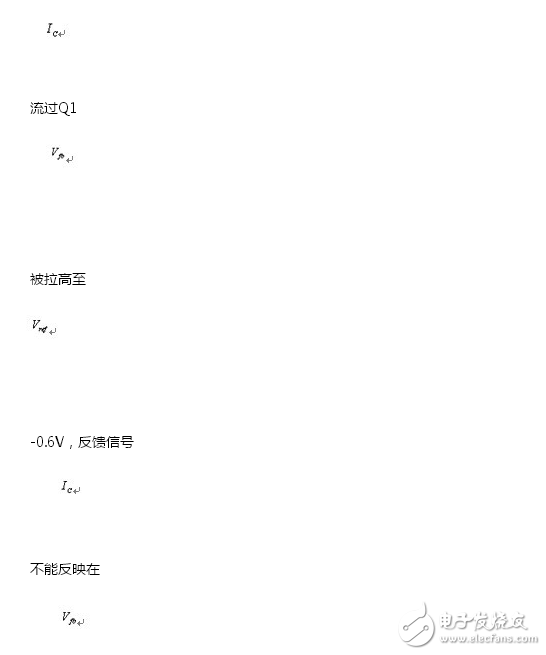

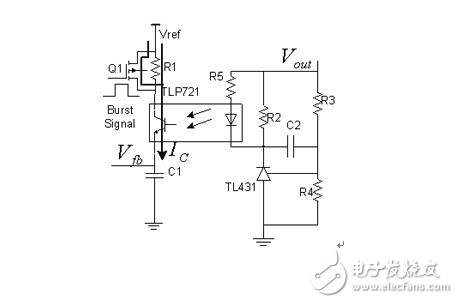

脚的反馈电压与0.6V/0.5V迟滞比较器比较,由比较结果控制门极驱动输出,其结构可见图8。我们可根据此原理用分立元件实现普通芯片的Burst Mode功能,即检测次级电压判断电源是否处于待机状态,通过迟滞比较器,控制芯片输出,电路如图9所示。

反馈信号,当Burst Signal为低电平时,Q1关断,

电路正常工作,当Burst Signal为低电平时,Q1导通,R1被短路,

上,控制器因此输出低电平。

另外对于有使能脚的PWM控制器,如L6565等,用可控脉冲信号控制使能脚使控制芯片有效或失效,也可以实现Burst Mode,上述Burst Signal可由图1中所示的迟滞比较器产生。

图10 控制反馈通道的Burst Mode

4 存在的问题

以上介绍的降频和Burst Mode方法在提高待机效率的同时,也带来一些问题,首先是频率降低导致输出电压纹波的增加,其次如果频率降至20kHz以内,可能有音频噪音。而在Burst Mode的OFF时期内,如果负载激增,输出电压会大大降低,如果输出电容不够大,电压甚至可能降低至零。如果增大输出电容,以减小输出电压纹波,则会导致成本增加,并会影响系统动态性能。因此必须综合考虑。

-

含SiC技术高压高频QR控制器在Fly back拓扑AC-DC快充产品(PD)效率更高性能稳定2025-09-25 1588

-

提高开关电源待机效率的方法2021-06-17 1041

-

利用μC/OS—II系统函数提高程序设计效率和代码质量的方法介绍2019-07-22 1424

-

降频和Burst Mode方法提高开关电源待机效率2019-04-15 3029

-

开关电源功耗分析和提高待机效率的方法2017-12-06 6987

-

burst mode flash哪些地方有详细介绍,page mode flash和burst mode flash的区别是什么2016-08-10 6358

-

怎么提高开关电源的待机效率2015-09-06 4000

-

揭秘怎样提高开关电源待机效率2011-12-14 7573

-

提高待机效率的方法2011-06-10 3594

-

如何提高开关电源待机效率2011-01-07 3443

-

Burst Mode电压控制电路图2010-08-31 3444

-

Switching power supply提高待机效率的方法2009-04-20 3932

全部0条评论

快来发表一下你的评论吧 !