S5935如何实现DMA传输的设计与研究

接口/总线/驱动

描述

摘要:文中介绍了具有PCI总线主控功能的专用接口芯片——S5935的基本结构,阐述了它如何实现DMA控制器的功能,并给出了用于实现DMA传输的WDM驱动程序。

1前言

计算机与外设之间有三种传输方式:程序方式、中断方式、DMA(DirectMemoryAccess)方式。其中,前两种方式都是CPU通过执行指令来实现主机与外设间的数据传输,传输速度较低;后一种方式是由DMA控制器直接实现外设和存储器之间的数据传输,它不通过CPU,传输速度较高。因此在高速数据传输系统中,常常利用DMA方式来实现计算机与外设间的数据传输。

由于个人计算机中的PCI总线具有总线主设备支持的特点(总线主设备支持的特点就是全面支持PCI总线主设备,允许同级PCI总线访问和通过PCI—PCI与扩展总线桥访问主存储器和扩展总线设备,并且,PCI主设备能够访问驻留于总线级别较低的另一个PCI总线上的目标)。所以,可以有两种途径来实现DMA传输,其一是利用计算机内部的DMA控制器;其二是利用具有总线主控功能的PCI接口芯片。由于后一种途径不占用计算机系统的DMA通道,节省了计算机的资源,因此,使用较多。

具有总线主控功能的PCI接口芯片主要有两种类型:一是可嵌入IP核的可编程逻辑器件,如Xilinx公司的Sparten系列等;二是专用的PCI桥接芯片,如PLX公司的PCI9054、AMCC公司的S5935等产品。前者设计较为灵活,但是要求开发者对PCI规范有较深入的理解,开发周期较长;后者设计较为简单,开发者只要正确配置接口芯片的配置空间,注意引脚的电气连接规范,就可以正确使用,开发周期较短。本文以专用PCI接口芯片——S5935为例,介绍其作为PCI总线主设备时如何实现DMA传输。

2AMCCS5935芯片

S5935是AMCC公司S59XX系列接口芯片中的一种,该芯片功能强大,可用于高速数据采集卡、视频加速卡、多媒体通信等。它既可作PCI总线主设备,也可作PCI总线从设备,应用较为广泛。它有三种工作方式:MAILBOX(邮箱)工作方式、PASS-THRU(直通)工作方式、FIFO(先进先出)工作方式。其中前两种工作方式只能是S5935作为PCI总线从设备时的工作方式,FIFO工作方式可以是S5935作为PCI总线主设备时的工作方式,也可以是S5935作为PCI总线从设备时的工作方式。

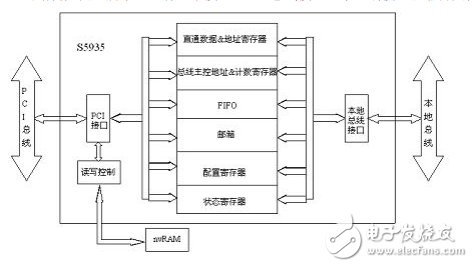

S5935的结构如图1所示,它有三个接口:PCI总线接口、本地端接口和非易失性存储

图1S5935结构框图

器接口。PCI接口用来实现计算机与S5935间的数据、地址、命令等的传输。本地端接口用来实现S5935与外部存储器间的数据传输以及与外部控制逻辑电路间的地址、命令等的传输。非易失性存储器接口有两种类型,它既可以与串行nvRAM相连,也可以与字节nvRAM相连,实现S5935头部空间的配置。

S5935的配置空间有256字节,分为头部配置空间和操作寄存器空间。头部占用64字节,它又可以分为两部份,前16个字节的定义在各种类型的设备中都是一样的,如厂商代码VID、设备代码DID,其余48个字节可以根据设备支持的基本功能情况进行不同的设置,如中断引脚的设置、PASS-THRU映射在存储器或I/O空间的大小设置以及PCI操作寄存器的基地址设置等。操作寄存器分为16双字的PCI操作寄存器和18双字的本地操作寄存器,前者只能通过PCI总线对其进行访问,后者则只能通过本地总线对其进行访问。它们的结构非常相似,其主要区别是本地操作寄存器比PCI操作寄存器多两个用于直通工作方式的直通地址寄存器(APTA)和直通数据寄存器(APTD),而少一个主控寄存器(MCSR)。

3S5935的DMA控制器特性

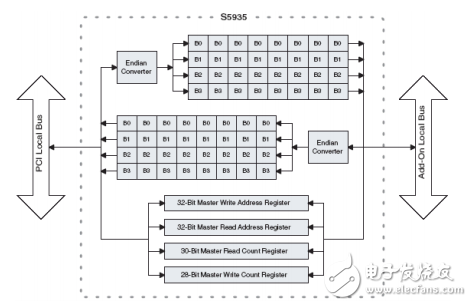

S5935的FIFO工作方式可以工作在总线主控模式下,此时S5935相当于一个带有数据缓冲区的DMA控制器,可以在不占用计算机系统的DMA通道的情况下,进行DMA传输。其内部结构如图2所示,它有两个单向FIFO:一个FIFO的数据传输方向是从PCI总线到本地总线,另一个用于本地总线到PCI总线的数据传输,每个FIFO的大小为8×32bit;还有两个地址寄存器和两个数据寄存器,分别用于存储DMA传输的首地址和传输所需的字节数。S5935的DMA传输可以设置为由本地总线发起,也可以由PCI总线发起的,它是在初始化时,通过设置nvRAM的45h单元的bit7实现的。下面以由PCI总线发起的DMA传输为例,介绍S5935的DMA控制器特性:

当需要进行DMA传输时,驱动程序通过设置MCSR寄存器的bit14或bit10,向S5935发出DMA请求信号(前者用于计算机内部存储器读,后者用于内部存储器写),S5935根据FIFO管理方案,如满足条件,使能REQ#信号,申请总线控制权。

当总线仲裁器收到总线控制请求信号后,如果允许,则使能GNT#信号,从而将总线的控制权传递给S5935。

S5935得到总线控制权以后,将存储在MWAR(或MRAR)内的地址信号发送到PCI地址总线上,并且每传送一个字节,MWAR(或MRAR)内的地址就会自动更新,以指向下一个要传送的字节。

S5935通过C/BE[3:0]#发送读/写控制信号,例如:发送的是0110,则为内部存储器读,发送的是0111,就为内部存储器写。

为了决定所传送的字节数,并且判断DMA传送是否结束,S5935利用MWTC(或MRTC)存储需要传输的字节数,每传送1个字节,字节计数器的值便自动减1,减为0时,则DMA过程结束。

当DMA过程结束时,S5935使REQ#信号为高,将总线控制权交还给总线仲裁器。由此我们可以看出,当S5935作总线主设备时,其功能类似于一个DMA控制器。当DMA传输由PCI总线发起,DMA控制器的初始化由驱动程序完成;当DMA传输由本地总线发起,其初始化由外部逻辑电路完成。

图2S5935的FIFO结构

4利用S5935实现DMA传输的应用实例

S5935的FIFO既可以同步方式工作,也可以异步方式工作。下面以PCI总线发起的DMA传输为例,介绍其在异步方式下的DMA传输。

4.1硬件设计

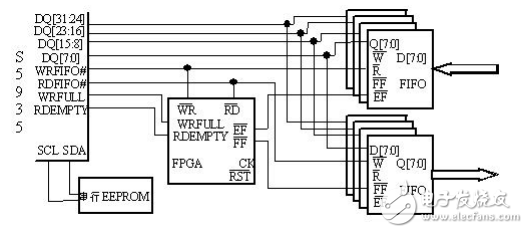

图3S5935与外部FIFO的接口

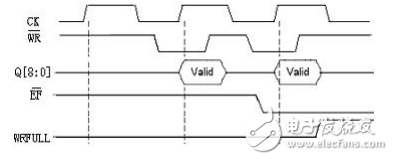

图3标示为S5935与外部存储器(异步FIFO)的主要信号引脚连接情况。由于该传输是由PCI总线发起的,所以外部可编程逻辑电路(FPGA)只需要满足S5935对外部FIFO的读写时序要求,DMA控制器的初始化由驱动程序完成。利用VHDL语言编程外部控制逻辑,其外部FIFO的读时序(也是S5935内部FIFO的写时序)如图4所示,外部FIFO的写时序(也是S5935内部FIFO的读时序)与它类似。

图4外部FIFO的读时序

4.2驱动程序的设计

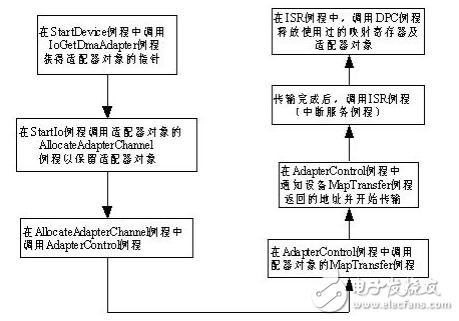

用于实现DMA传输的驱动程序的流程如图5所示。

图5驱动程序流程图

5结束语

随着三维动画、视频跟踪等新兴行业的快速发展,数据的传输速率要求越来越高,CPU任务越来越繁重,在计算机与外设之间采用DMA方式传输不仅可以提高数据的传输速率,而且可以减轻CPU的负担。采用专用的具有总线主控功能的接口芯片可以使设计更简单,开发周期更短,不失为一种经济的、高效率的办法。

-

STM32 DMA传输的问题分析2023-12-01 5603

-

一种高性能多通道通用DMA设计与实现2023-11-20 1064

-

DMA不产生传输完成中断2023-10-18 2678

-

VersaClock 5 5P49V5935/5933 评估板s 用户指南2023-05-15 480

-

DMA带中断的内存到内存传输2023-03-23 4495

-

如何去实现DMA传输的配置代码呢2021-12-10 1490

-

STM32F429芯片带FIFO的DMA传输实现过程2020-09-04 8893

-

STM32F4系列的DMA请求与DMA传输通道的映射关系多了些选择性,灵活性2020-06-04 14034

-

28335 ADC的DMA传输如何实现?2020-05-12 2155

-

DMA数据传输(源代码分享)2018-04-27 10305

-

DMA数据传输在SPEAR300实现高速串口驱动设计2018-04-04 2062

-

双通道DMA的研究与设计2010-04-13 659

-

利用S5935实现DMA传输的研究2010-02-21 598

全部0条评论

快来发表一下你的评论吧 !