可编程DMA控制器IP设计

控制/MCU

描述

1、简介

IPOntellectualPIDperty)是随着EDA(ElectroniDesignAn-tomation)技术发展而提出的新概念。随着微电子工业的飞速革命,集成电路的设计规模越来越大,以满足日渐复杂的电子系统的需要,同时又由于上市时间厂linetoMarket)的要求,必须花费尽可能少的时间来证明部件和系统的可靠性。所以,从共享的角度来看待问题,对已经过设计验证的功能模块的重用无疑是解决这个瓶颈的最佳方案。

当前的设计思想是类似软件的面向对象的概念,采用虚拟插座VS(VirtuaS0ckets)的概念,把多个不同来源的电路模块组合起来达到要求的功能,并将其集成在一块硅片上。IP就是实现这种功能模块的混合、吗配和重用以实现片上系统(SystemonACh响设计的最好方法。这将使系统级IC集成设计成为切实可行的技术方向。

IP就其本质来讲即是一个能提供正确接口信号的功能模块。MentorGraPhics所下的定义是可重用的部件(ReusableComPOnentS)。具体在ASIC/IC设计中,通常指的是一个软核,是一个通过具体电路验证(Silicon-Verified)的功能模块,它以可综合的寄存器传输级RWRegisterTranslationbevel)文件给出,通过库文件调用可实现它的重用。

2、可编程DMA控制器

DMA直接存储器存取脏制器是用于微处理器系统的外围接口电路芯片。它能够增强系统外部设备同主存储器之间信息传送的性能,从而增强数据吞吐量。

8237A是Intel公司推出的8位DMA控制器,提供了大量的可编程控制特性,同时可以允许程序动态编程控制而优化系统。它主要配合微控制器,完成外围设备与存储器之间的大量高速数据传输工作,并且它也提供存储器到存储器的传送功能。当前存在着大量采用8237A作为外围接口电路芯片的微控制电路,所以8237A的IP设计对于这些系统片上集成具有重要意义。

8237A的IP包含以下几个特点:

(1)包含了四个通道,每个通道可以有四种工作模式,可以单字节传送、块传送房求传送、级连工作。每个通道可以通过级连模式连接附加的控制器芯片而扩展成为任意通道数,其它的三个模式可以由用户编程为外围器件提供DMA传送服务。

(2)通道编程设置为自动初始化,每当传送结束或者EOP信号有效时,通道可以自动初始化。由于每个通道的地址和字寄存器都是16位,所以具有64K地址以及字计数能力。

(3)提供通道优先权控制,进行固定和循环优先权调度。8237A最突出的特点是具有对多种传输方式的控制。

3、电路功能模块设计

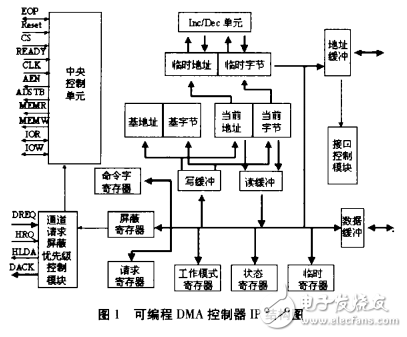

整个系统设计成为全同步电路。根据Intel提供的器件时序,设计在系统时钟CLK的下降沿将状态翻转,给出相应控制信号;而系统的数据通道在系统时钟CLK的上升沿进行数据传递。通过对文献间所进行的逻辑分析,所设计的IP电路划分为如下模块:接口模块、通道请求优先级及屏蔽控制模块。中央控制模块、通道地址和计数器控制模块、命令寄存器模块、状态寄存器模块。如图1。

3.1接口模块

接口电路的主要功能是实现与CPU和存储器以及外部设备的连接。接收CPU写入的命令字、地址、字节数、模式控制率等;向CPU提供状态字以及各个寄存器的内容。对于存储器和外设的接口一般都是提供传输数据的当前地址,在存储器至存储器传输工作模式下,还要使用临时寄存器Temp对传输的数据进行暂存。

3.2通道请来优先级及屏蔽控制模块

这个模块利用边沿检测器和或逻辑实现了对DREQ(DMARequest晴求的沿触发以及电平触发的检测。同时通过优先级设置和屏蔽寄存器的设置判定对应请求是否有效,之后将有效的请求送给中央控制模块,由中央控制模块对相应的通道进行处理,并且发送DACK(DMAcknowle吃小向应信号通知外设撤消DREQ请求。优先级可以用命令方式设置为固定优先级和循环优先级。

3.3中央控制模块

这是整个IP设计的核心部分,该模块作为DMA控制器的主要工作模块,相应地执行各种控制命令,负责在空闲(id由周期响应CPU操作;在执行(ActiVe调期,协调DMA内部的其它模块,接管总线控制,提供数据传输所需要的所有地址、数据暂存控制,并向外提供读写时序信号。

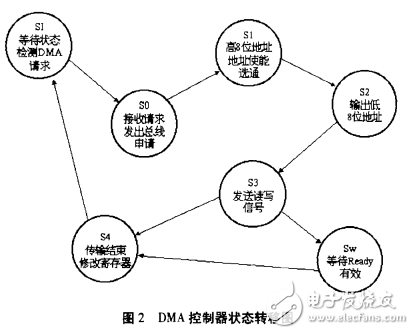

8237A的工作过程可以分为7个状态,即SI,SO,S1,S2,S3,S4和Sw。它的状态转移如图2所示。该模块的主要构成部分就是系统状态机,而其中的引,SZ,S4状态对于数据通道进行主要操作,8237A是一个同步电路,所以中央控制模块就设计成一个同步状态机,每个状态都是一个时钟周期的宽度。

3.4 Inc/Dec单元

因为在S1,S2,S4这三个状态,也就是三个周期中,8237A必须执行加载,地址改变,恢复这三个操作,而在部分情况下地址必须要求在S4改变,所以就不能保证一个周期一个操作。这样就必须以每个通道的当前寄存器作为Inc/Dec的源和目的操作数。

如果每个通道的地址和计数采用同步计数器,该同步计数器由每个通道的当前寄存器实现,这样的话,四个通道的地址和字数计算就至少需要四个同步计数器;那么这个设计与直接采用组合逻辑Inc/Dec单元的设计相比,就少了一个4路16位的多路选通器。如果按照ASIC库标准单元设计,该多路选通器将占用16X4个CMOS门,同时由于同步计数器的进位判断逻辑并本比直接的组合逻辑Inc单元少,所以在假设门的传输延迟满足工作频率的情况下,它们都可以采用每级一个与门的逻辑,应该为14个二输入与门与匕个二输入异或门,每个与门占用两个CMOS门,每个异或门占用四个CMOS门。这样采用同步计数器将占用Zx4xl4+4x4xls=352个CMOS门;采用组合逻辑Inc单元将占用16X4+Zxl4+4X15=152个CMOS门。即使在只有加1逻辑的情况下,同步计数器的进位判断逻辑比直接的组合逻辑Inc单元多。如果再加上减1逻辑,同步计数器占用的CMOS门将会以接近4倍的关系和直接的组合逻辑Inc/Dec单元一起增长,所以应该采用组合逻辑Inc/Dec单元。

当然以上的设计都是在采用ASIC标准单元库的情况下,由于采用FPGA实现时,没有可以直接利用的MUX单元,4路16位的多路选通器就会占用较多的逻辑资源,同时影响系统频率的提高,而且FPGA中提供专用的进位链逻辑来优化计数器设计,所以应该采用四个同步计数器的设计实现。所以在IP的设计中,考虑到实现目标工艺的不同,以及对于系统整体性能的需求不同,提供了可以参数化选择的实现方法。

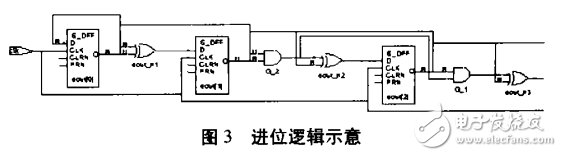

3.5先后触发器

在8237ADMA控制器中,先后触发器的作用就是在系统读写DMA中的16位寄存器时,提供高低8位寄存器部分的先后次序控制。

设计中,对于高低8位寄存器部分的读写要根据先后触发器的值进行判断操作。由于整个系统是同步设计,就不能采用利用读写信号的上升沿直接将先后触发器翻转的方法。所以,设计中对读写信号进行边沿检测,利用检测得到的读写结束信号,在时钟的上升沿将触发器翻转。而且,由于并不是所有的对内部寄存器的读写都需要翻转先后触发器,所以还要对地址的进行判断,但是如果在读写信号结束时进行检测,此时的地址可能已经改变。所以设计中在读写信号的开始时就进行检测,并将结果保存,以供在读写信号结束时判断是否翻转触发器。

所以系统中先后触发器有四个边治检测器,两个用来检测端口读写信号的开始,两个用来检测端口读写信号的结束。

3.6连续传输时SI状态加载高8位地址控制

在DMA连续传输时,当地址的低8位从ox00向oxFF变化时,或从oxFT向ox00变化时,需要进入引状态加载已经变化了的高8位地址。因为地址加1减1逻辑不是用计数器实现的,所以无法采用低8位的进位借位信号进行判断。设计中采用将高8位的最低位值与运算后得到的值进行异或(XOR),该值的作用就如同进位借位标志。

4、实现与验证

对于可编程DMA控制器IP的设计实现是采用TOp-down设计方法,首先建立了一个可供仿真的顶层模型,在仿真环境中确定了各种控制信号的时序关系,之后才使用具体的功能电路逐步细化整个系统。这种设计方法,可以在设计的初期就能够发现结构设计中存在的错误和瓶颈,以避免反复设计。由于可编程DMA控制器IP是同步电路,所以在设计中尽量采用各种同步信号,并且采用一些措施来减少组合路径的延迟,提高系统的工作时钟频率,同时消除毛刺,使电路性能更加稳定。

在设计中,作者采用VHDL(VHSIHaldDtSCriptionban-gUage)语言编写代码。利用SynoPsys的Design-Analyzer进行编译和综合。采用iii,nx验证IP正确性,采用Altera的MAX-Plus11进行布局布线,选择ALrFERA的Fled0K30器件,进行了片上验证。与ALTERA公司提供的8237AIP进行比较,资源占用基本一致,时序分析时性能较好。

在进行ASIC门级后仿真(P0st-simulation)时,采用的是标准的vrrsLtiny,采用cnosl艺,线宽为o.5微米,具有Sin-of性质。提取了布局布线后的各种延迟信息后,在Sn-0PSyS的VSS中进行仿真,验证了IP的正确性。

5、结论

可编程DMA控制器IP设计实现了IP设计的目标,即设计的重用,实现了一些相应单元模块的参数化设计。只需要进行很少量的参数修改工作,就可以重构一个适用于不同需求的DMA控制器,例如可以将四个通道进行裁减。而且可以根据实现工艺(ASIC或FPGA)的不同,设定相应参数,选择合适的设计。

国内对于IP的设计研究还是刚刚开始,通过可编程DMA控制器IP设计可以获得经验。在设计中作者基本按照TOP-down的设计方法。在实际验证时整个电路的各项参数都达到了Intel手册上提供的参数,电路工作正常,这说明高层设计方法在数字电路的设计工作中是有效的,这个设计也作为这方面的一个探索。

-

可编程控制器的组成 可编程控制器有哪些特点?2024-01-18 3648

-

可编程控制器PLC概述2023-04-19 2100

-

什么是可编程逻辑控制器?可编程逻辑控制器有哪些特点?2021-07-05 3294

-

可编程控制器的特点有哪些2020-10-06 9516

-

可编程控制器基本知识_可编程控制器原理及应用2018-04-25 62061

-

L82C37A可编程DMA控制器2017-12-07 3415

-

可编程序控制器基础与编程技巧2017-09-19 929

-

PLC-S7200可编程序控制器介绍2016-04-28 820

-

8237 可编程DMA控制器 altera提供2012-08-10 2030

-

可编程控制器基本指令2010-03-30 1561

-

8237可编程DMA控制器资料与程序代码2009-04-19 1429

-

可编程控制器原理及应用 PPT2008-12-30 1432

-

可编程控制器(PLC)2008-12-04 1255

-

可编程控制器概述 ppt2008-11-20 1069

全部0条评论

快来发表一下你的评论吧 !