stm8s gpio端口配置

嵌入式操作系统

描述

简介

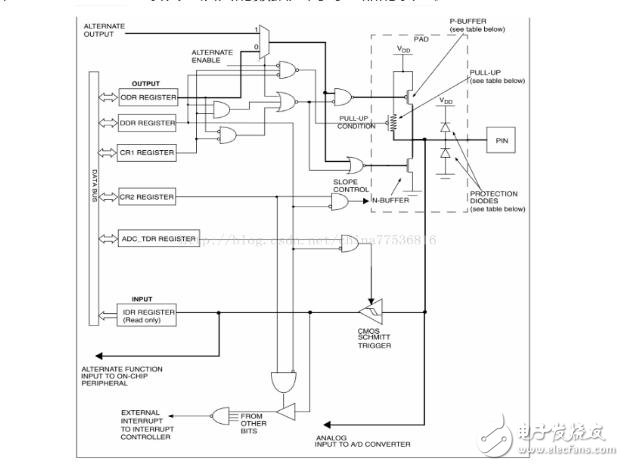

STM8的通用输入/输出口用于芯片和外部进行数据传输。一个IO端口可以包括多达8个引脚,每个引脚可以被独立编程作为数字输入或者数字输出口。另外部分口还可能会有如模拟输入,外部中断,片上外设的输入/输出等复用功能。但是在同一时刻仅有一个复用功能可以映射到引脚上。

复用功能的映射是通过选项字节控制的。请参考数据手册关于选项字节的描述。每个端口都分配有一个输出数据寄存器,一个输入引脚寄存器,一个数据方向寄存器,一个选择寄存器,和一个配置寄存器。一个I/O口工作在输入还是输出是取决于该口的数据方向寄存器的状态。

STM8S的GPIO主要功能

● 端口的各个位可以被单独配置

● 可选择的输入模式:浮动输入和带上拉输入

● 可选择的输出模式:推挽式输出和开漏输出

● 数据输入和输出采用独立的寄存器

● 外部中断可以单独使能和关闭

● 输出摆率控制用以减少EMC噪声

● 片上外设的I/O功能复用

● 当作为模拟输入时可以关闭输入施密特触发器来降低功耗

● 在数据输出锁存时支持读-修改-写

● 输入兼容 5V电压

● I/O口工作电压范围为1.6 V 到V DDIOmax

每个端口都分配有一个输出数据寄存器,一个输入引脚寄存器,一个数据方向寄存器,一个选择寄存器,和一个配置寄存器。一个I/O口工作在输入还是输出是取决于该口的数据方向寄存器的状态。

GPIO的每个端口由输出数据寄存器 (ODR),引脚输入寄存器 (IDR),数据方向寄存器(DDR)控制,控制寄存器1(CR1)和控制寄存器2(CR2)用于对输入/输出模式配置。

模式配置图为:

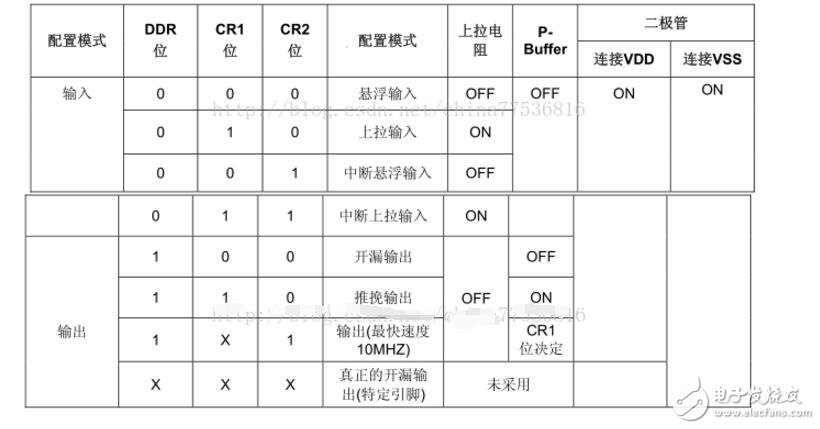

可以得出将 DDRx 位清零就选择了输入模式。在该模式下读IDR寄存器的位将返回对应I/O引脚上的电平值。将 DDRx 位置1就选择了输出模式。在该模式下向ODR寄存器的位写入数据将会通过锁存器输出对应数字值到I/O口。读IDR的位将会返回相应的I/O引脚电平值。通过软件配置CR1,CR2寄存器可以得到不同的输出模式:上拉输出,开漏输出。

复位后引脚状态为悬空输入。注意!!没有使用的I/O口要连接到固定的电平值,上拉或下拉。

另有三个寄存器 端口 x 输出数据寄存器 (Px_ODR), 端口 x 输入寄存器 (Px_IDR)(可读), 端口 x 数据方向 (Px_DDR)[0输入:1输出]。均为8位寄存器。

还有两个配置寄存器 端口 x 控制寄存器 1 (Px_CR1), 端口 x 控制寄存器 2 (Px_CR2)。

I/O的配置和使用

每一个端口都有一个输出数据寄存器(ODR),一个引脚输入寄存器(IDR)和一个数据方向寄存器(DDR)总是同相关的。

控制寄存器1(CR1)和控制寄存器2(CR2)用于对输入/输出进行配置。任何一个I/O引脚可以通过对DDR,ODR,CR1和CR2寄存器的相应位进行编程来配置。

寄存器中的位n对应于口的引脚n。各种不同配置总结如表18。

(表18:IO口配置表)

注意:连接VDD的二极管在实际开漏极状态引脚是无效的,在引脚和VOL之间的局部保护设备重要性是有效的。

没有使用的I/O引脚必须连接到一个固定的电平值。或者是上拉或者是下拉。

输入模式

将DDRx位清零就选择了输入模式。在该模式下读IDR寄存器的位将返回对应I/O引脚上的电平值。

如表18所示,理论上STM8可以通过软件配置得到四种不同的输入模式:悬浮不带中断输入,悬浮带中断输入,上拉不带中断输入和上拉带中断输入。但是在实际情况下不是所有的口都具有外部中断能力和上拉,用户应参考数据手册中关于每个引脚的实际硬件性能描述来了解更多细节。

输出模式

将DDRx位置1就选择了输出模式。在该模式下向ODR寄存器的位写入数据将会通过锁存器输出对应数字值到I/O口。读IDR的位将会返回相应的I/O引脚电平值。通过软件配置CR1,CR2寄存器可以得到不同的输出模式:上拉输出,开漏输出。

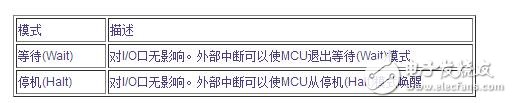

低功耗模式

表19低功耗模式对STM8S的GPIO口的影响

注意:如果PA1/PA2被用来连接外部谐振器,为了确保在HALT模式下有最低功耗必须配置PA1和PA2为带上拉输入。

-

STM8S怎么选择外设功能还是GPIO功能?2024-04-30 364

-

请问STM8S外设模块的GPIO引脚如何配置?2024-04-11 509

-

STM8S外设模块的GPIO引脚应该如何配置?2023-11-02 570

-

STM8S配置字节OPTION BYTE2023-10-10 782

-

STM8S的配置字节Option Byte2023-10-07 729

-

stm8s可外部扩展多少IO口 如何设置stm8的中断寄存器 STM8S单片机CC寄存器的作用2023-04-01 2875

-

如何在STM8S控制器上执行通用GPIO功能实现LED闪烁2022-08-11 7861

-

自学STM8S的方法2022-02-08 811

-

STM8S自学笔记-006 GPIO输入:按键输入 与 按键滤波2021-12-05 931

-

怎样去配置STM8S独立看门狗2021-09-26 954

-

STM8S新42BDLC电机第7章工程开发STM8S库2018-03-05 1140

-

STM8S开发入门2016-09-01 1284

-

STM8S寄存器重新映射2016-08-17 954

-

STM8S入门指引2016-05-09 1055

全部0条评论

快来发表一下你的评论吧 !