i2c总线的起始和终止的条件

接口/总线/驱动

描述

如何检测I2C的开始条件和结束条件:

开始条件检测:

(1)尽量选用带复位输人的I2C从器件,从I2C总线死锁产生的原因可以发现I2C总线死锁的一个必要条件是主设备复位了而从设备没有复位。

如果从设备选用带复位输入的芯片,将主从设备的复位信号连接在一起,当外部产生复位事件时,主从设备同时复位,这样就不会发生I2C总线死锁现象了。

这种方法的缺点也是显而易见的,首先,大部分I2C从器件都没有复位输入,器件选型受到了很大的限制;其次,这种对于主设备集成看门狗引起的复位也没有效果。

(2)将所有的从I2C设备的电源连接在一起,通过M0S管连接到主电源,而MOS管的导通关断由I2C主设备来实现一般来说,I2C主设备都是具有运算单元的处理器。控制功能可以通过处理器的GPIO来实现。

每次主设备复位时,运行程序控制GPIO关断MOS,使从设备失去电源。然后延时一段时间后再导通MOS管,给从设备上电,从而达到让从设备强制复位的效果。

这种方法能弥补第一种方法的不足,但是会增加电源设计的复杂性,影响Layout设计时电源的完整性;同时还需要更改处理器的底层boot代码,影响底层软件的通用性和可移植性。

结束条件检测:

在I2C主设备中增加I2C总线恢复程序。

每次I2C主设备复位后,如果检测到SDA数据线被拉低,则控制I2C中的SCL时钟线产生9个时钟脉冲(针对8位数据的情况),这样I2C从设备就可以完成被挂起的读操作,从死锁状态中恢复过来。

这种方法有很大的局限性,因为大部分主设备的I2C模块由内置的硬件电路来实现。软件并不能够直接控制SCL信号模拟产生需要时钟脉冲。使用此种方法可以使用IO模拟I2C,SCL时钟易控制。

I2C总线SDA\SCL以及开始终止条件

I2C只用两条线(SDA和SCL)在连接到总线上的设备之间传送数据。每一个设备都由唯一的地址来识别(不管是微处理器、LCD驱动器、存储器或者键盘接口),并且可以依照设备的功能作为发送器或者接收器使用.LCD驱动器可能只是个接收器,而存储器可以发送和接受数据。除了发送器和接收器,当传送数据时设备还可以作为主机或者从机。主机就是初始化数据传输和产生时钟信号的设备,在那个时刻,任何被寻址的设备都是从机。

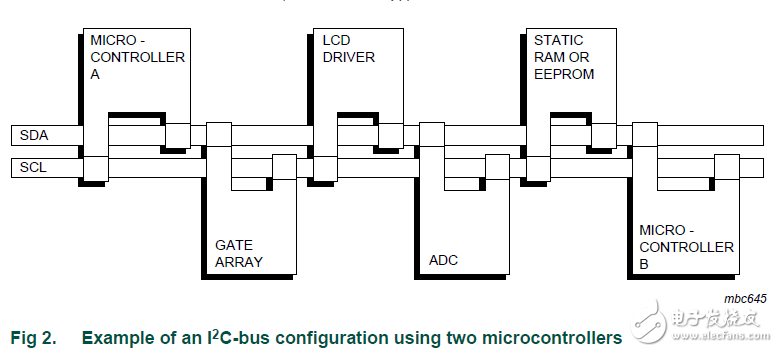

I2C总线是一个多主机总线。意味着可以连接多个可以控制总线的设备到总线上。主机通常是微控制器,我们可以考虑以下两个连接到总线上的微处理器之间的数据传输的情况。

这个例子中突出了I2C总线中的主从和接收器-发送器之间的关系。注意这些关系不是固定的,仅依赖于当前时刻数据传输的方向。数据传输的过程如下:

1.假定微控制器A向微控制器B发送数据

微控制器A(主机)寻址微控制器B(从机)

微控制器A(主机-发送器)发送数据到微控制器B(从机-接收器)

微控制器A结束数据传输

2.假定微控制器A从微控制器B接收数据

微控制器A(主机)寻址微控制器B(从机)

微控制器A(主机-接收器)从微控制器B(从机-发送器)接收数据

微控制器A结束数据传输

甚至在这种情况下,主机(微控制器A)产生时序并终止传输。

在多个微控制器连接到I2C总线上时意味着可能有多个主机尝试初始化数据传输。为了避免由此引发的混乱,设计了一个仲裁机制。它依靠线与逻辑连接所有I2C接口道I2C总线。

如果有多个主机尝试发送信息到总线上,在其它产生“0”的情况下,首先产生“1”的主机会丢掷仲裁。仲裁时的时钟信号是用线与连接到SCL线的主机产生的时钟的同步结合。

I2C总线上的主机设备通常负责产生时钟,当传输数据时每个主机产生自己的时钟信号。只有在低速从设备控制时钟线或者仲裁发生时,主机的总线时钟才会被改变。

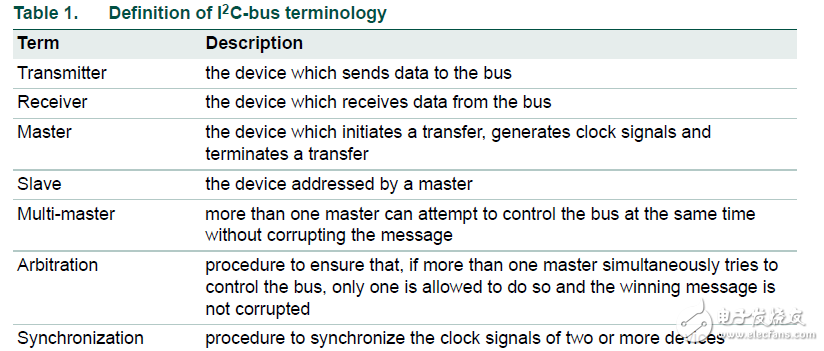

下表总结了I2C总线中的一些配置选择:

[1]这里也指被当作从机的主机

[2]时钟拉伸是部分从机的特性。如果在系统中没有从机可以拉伸时钟(将SCL拉低),主机一定需要设计处理程序

[3]‘Bit banging’(软件模拟)多个主机系统应该考虑START字节

SDA和SCL信号

SDA和SCL都是双向线路,通过电流源或者上拉电阻连接到一个正向电压。(见下图)当总线空闲时,两条线都是高电平。连接到总线的设备的输出级必须是OD(漏极开路)或者OC(集电极开路)门才能执行线与功能。在标准模式下I2C总线传输数据可以达到100kb/s的速度,而在快速模式下达到400kb/s的速度,快速plus模式下是1Mb/s的速度,告诉模式下是3.4Mb/s的速度。总线的电容限制连接到总线上的接口数量。

对于一个单一主机的应用,如果总线上没有设备可以拉低时钟那么主机的SCL输出应该是push-pull(推挽)驱动设计。

SDA和SCL的逻辑电平

由于有各种不同的工艺的设备(CMOS NMOS 双极性)可以连接到I2C总线,低电平和高电平不是固定的而是依赖于相对应的VDD的电平。

数据有效性

在时钟为高期间SDA线上的数据必须稳定。只有在SCL线上的时钟信号低时数据线才可以改变高低状态。每个数据位传输都需要一个时钟产生。

开始和终止条件

所有的传输都由一个START(S)开始,有一个STOP(P)终止。

START条件是当SCL高时SDA从高到低

STOP条件是SCL高时SDA从低到高

开始条件和终止条件一直由主机产生。在开始条件后总线就处于忙状态。在终止条件后隔上一个固定时间总线就处于空闲状态。如果没有终止条件产生,而是一个重复的开始条件(Sr),那总线依旧是忙状态。这种情况下S和Sr在功能上是一样的。

如果连接到总线的设备包含了必须的接口硬件那么开始条件和终止条件的检测时很容易的。但是没有这样接口的微控制器在每个时钟周期内至少要采样两次SDA线来识别有没有电平变化.

- 相关推荐

- 热点推荐

- I2C总线

-

I2C总线数据包结构详解2025-01-17 1517

-

I2C串行总线协议是什么?I2C总线有哪些优点?2023-09-12 2883

-

I2C总线的基本通信总结2021-08-26 19388

-

i2c总线用来做什么_i2c总线数据传输过程2020-11-24 7739

-

I2C 总线协议图解2019-08-01 2947

-

i2c总线协议标准与规范2017-12-06 27661

-

基于51的I2c总线2016-01-13 1086

-

使用GPIO模拟I2C总线进行通信2015-02-02 20017

-

基于CPLD的I2C总线接口设计2011-02-12 1261

-

i2c总线的特点2009-08-05 2594

-

I2C规范,I2C总线原理2009-04-09 9189

-

并口模拟I2C总线的设计2008-09-11 4513

-

i2c总线协议pdf2008-08-13 8330

-

什么是i2c总线2007-11-05 3181

全部0条评论

快来发表一下你的评论吧 !