L82C37A可编程DMA控制器

控制/MCU

描述

摘要:叙述了L82C37A可编程DMA控制器的主要功能、制造工艺和测试,并对其基本电路及设计方法进行了简要介绍。

1 概述

L82C37A可编程DMA控制器是一个高性能的可编程直接存取控制器,可在没有CPU干预的情况下进行内存与外设之间的数据直接传输。在微机系统中,通过使用DMA操作可大大提高系统的单个或多个I/O装置的数据传输速率。

该电路采用2.0μm硅栅CMOS全离子注入工艺制造,集成度为13500管位,芯片面积为25.12mm2,采用DIP 40 PIN 陶瓷封装。

该电路具有以下特点:

与NMOS 82C37A兼容;

具有四个可编程的独立DMA通道,每个通道具有自动初始化能力;

能到存储器到存储器间的传输;

有四种基本工作方式和三种传输方式;

任意扩展DMA通道数;

每个通道有64k地址和64k字节记数空间;

数据最高传输速率可达4MB/秒;

低功耗静态CMOS设计,IDDSB=10μA;

与TTL兼容;

单5V电源工作;

工作频率8MHz;

工作温度范围-55℃~+125℃。

2 逻辑结构和功能

2.1 L82C37A主要功能

L82C37A主要功能有以下七点:

(1)该电路有四个独立DMA通道;

(2)每个通道的DMA请求都可分别允许和禁止;

(3)每个通道的DMA请求优先权具有固定方式和循环方式;

(4)每个通道一次传送的最大长度64k字节的数据,可在存储器与外设间进行传送,也可在存储器的两个区间进行传送;

(5)有四种DMA传输方式:①单字节传输方式;②数据块传输方式;③请求传输方式;④ 级连方式。在每种方式下,都能在接收外设的请求信号DREQ后,向外设发送响应信号DACK后就可以占用总线,进行DMA传送。每传送一个字节,修改一次地址指针,当规定传送的字节数送完时,发出终端计数脉冲TC,结束传送或重新初始化;

(6)允许外设用EOP信号结束DMA传送或重新初始化;

(7)L82C37A可以级联,任意扩展通道数。

2.2 L82C37A逻辑结构

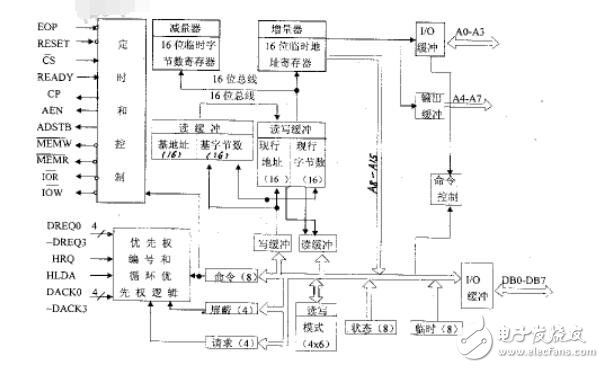

L82C37A的逻辑功能较为复杂,其逻辑框图如图1所示。图中的通道部分只画出了一个通道的情况,即每个通道都有一个基地址寄存器(16位)、基字节数计数器(16位)、现行地址寄存器(16位)和现行字节数计数器(16位),每一个通道都有一个6位的模式寄存器,用以控制不同的工作模式。

图1 L82C37A逻辑框图

L82C37A的结构中包含了三个基本的控制逻辑块。

时序控制逻辑块:根据编程规定的DMA的工作模式,产生包括DMA请求、DMA传送及DMA结束所需要的内部时序和外部信号。

程序命令控制块:对在DMA请求服务之前,CPU编程对给定的命令字和模式控制字进行译码,以确定DMA服务的类型。

优先权编码逻辑:对同时有请求的通道进行优先权编码,确定哪个通道的优先权最高,优先权可以是固定的,也可以是循环的。

另外,L82C37A的数据引线都有三态缓冲器,因而可以占用也可以释放总线。

2.3 L82C37A的工作周期

L82C37A有两种主要的工作周期,即空闲周期和有效周期,每一个周期由若干个时钟周期组成。

(1)空闲周期

L82C37A在完成了一个DMA服务之后,若没有新的DMA请求,或在主清零或硬件复位后,将进入空闲周期执行SI状态。在每个时钟周期它都要对通道的请求线DREQ进行采样,在没收到DREQ前,它将始终处于SI态。

在此状态中,CPU可以查询其状态或对其进行编程。若 ,则CPU可以对其进行读写操作,可以对其基地址、基字节数、当前地址、当前字节数等寄存器进行读/写。此时,需通过数据总线和地址总线以及

,则CPU可以对其进行读写操作,可以对其基地址、基字节数、当前地址、当前字节数等寄存器进行读/写。此时,需通过数据总线和地址总线以及 和来选择寄存器并改写数据。由于这四组寄存器均为16位,而数据总线是8位的,则由内部高/低位寄存器控制,将数据分成高8位和低8位,分两次写。另外还有些软件命令,不通过数据总线,仅由地址A0-A3和

和来选择寄存器并改写数据。由于这四组寄存器均为16位,而数据总线是8位的,则由内部高/低位寄存器控制,将数据分成高8位和低8位,分两次写。另外还有些软件命令,不通过数据总线,仅由地址A0-A3和 等信号的译码来设置。

等信号的译码来设置。

(2)有效周期

当外设或CPU发出DMA请求时,将跳出SI状态进入DMA服务的第一状态S0。此时,虽收到SREQ并发出HRQ,但在收到CPU返回HLDA信号后,L82C37A才进入由S1-S3组成的工作状态,若外设的工作速度较慢,DMA传送不能在S4状态之前完成时,则可用READY线在S2或S3与S4之间插入SW状态,直到本次传输结束。SW状态是等待周期,主要是为适应慢速外设,以延长传输时间。

在存储器至存储器传输时,要作存储器读和写操作,所以每一次传输需要8个时钟周期,其中4个周期S11-S14完成存储器读,另外4个周期S21-S24完成存储器写操作。

2.4 L82C37A的工作模式

L82C37A在DMA传送时有四种工作模式:

(1)单字节传送方式

一次只传送一个字节,每次传输后,字节计数器减1,并修改地址,HQR变为无效,并释放系统总线,当字节减到0时,产生一个IC脉冲结束DMA传送或重新初始化。

在这种模式下,DACK有效前,DREQ必须始终保持有效。但是,如果DREQ的有效时间比单字节传输所需时间还长,那么,在传输完一个字节后,L82C37A首先释放总线,然后再产生一个DREQ,完成下一个字节的传送。

(2)块传送方式

一经DREQ启动,并在其发出响应信号DACK后,便进行连续的数据传输,直到字节计数器减到0,产生终端计数器脉冲TC,或由外部输入一个有效的 信号,传输才结束。

在这种方式下,DREQ信号仅需要维持到DACK有效,在数据传输完了之后,由程序决定是结束操作还是重新初始化。如果不需要自动初始化,则数据传送完,便自动停止操作,释放总线。

(3)请求传送方式

在这种方式下,L82C37A可连续地传送数据,直到产生终端计数脉冲TC,以表示要传送的数据传完。此时,DREQ无效,使传输结束。L82C37A释放总线,传输结束后,字节计数器和当前地址寄存器中,仍保持该通道传输结束前的最后一个值。只要外设准备好要传递的数据,并发出DREQ信号,则可继续传输。

(4)级联方式

这是为扩展通道数而设的一种工作方式。第二级的DRQ和HLDA信号与第一级的DREQ和DACK分别相连,第二级各片子的优先权和与其相连第一级的通道相对应。此时,第一级只起优先权网络的作用。除了由某一个二级的请求信号通过它向CPU输出HRQ信号外,并不输出任何其它信号。实际的传输操作则由二级片子完成。若需进一步扩展通道,则同样还可以级联三级等等。

2.5 L82C37A内部基本电路

(1)基地址、字节数、当前地址、字节数寄存器组电路

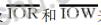

在器件中,基地址、当前地址、基字节数和当前字节数寄存器的电路形式基本相同,如图2所示。

图2 基地址(字节数)当前地址(字节数)寄存器

在图中,左半部分为基地址或基字节数寄存器,右半部分为当前地址或当前字节数寄存器,寄存器单元中数据的出入由IDS控制。在CPU对其进行写时,内总线上的数据,在IW控制下进入到寄存器,并写到寄存器中。

在图中看出,基地址和当前地址(基字节和当前字节数)寄存器,具有相同的初始值,因为它们是在同一时刻由同一控制信号写入的。

CPU对寄存器组的读操作却只限于当前地址和当前字节数寄存器。因为基地址和基字节数寄存器只写不读。图中IDS是通道寄存器选择线,由A0-A3译码形成,Q是复位线,由系统复位线RESET或主清零等软件命令控制。D和V是自动初始化控制线,当其有效时,其寄存器的内容被重新写入当前寄存器中。每完成一次传输地址和字节数都将被修改,由R线送到寄存器中。

(2)模式寄存器

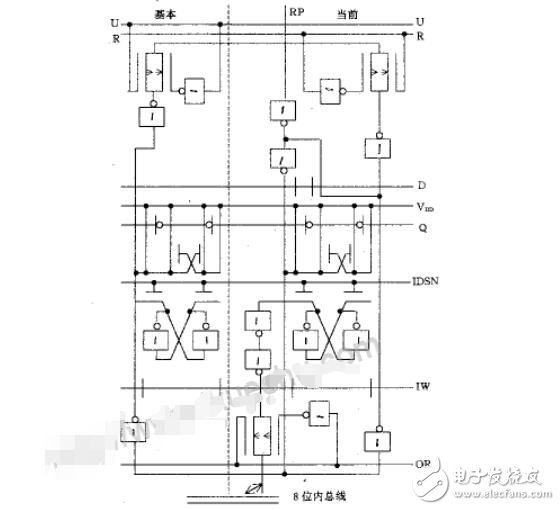

L82C37A 内部每个通道都有一个6位的模式寄存器,其结构如图3所示。

图3 模式寄存器

该寄存器是确定工作模式的,这是一个D触发器,其输入/输出均与数据总线相连。在输入控制信号ME=1时,总线数据写入寄存器。ME=0时数据锁存。MS有效时,模式寄存器的数据送往相应控制的控制端。如果CPU查询模式寄存器则可使EMR有效,将其内容读到数据线上。

模式寄存器由A0-A3和D0、D1来选择,当A0-A3为1101,D0 D1为00时,则选中通道0的模式寄存器。此时CPU可以对其进行读/写操作。

在DMA控制器中,还有命令寄存器、状态寄存器、请求寄存器、屏蔽寄存器、暂存寄存器等。在此不赘述。

2.6 L82C37A版图设计

L82C37A的版图是采用2.0μm硅栅CMOS单层金属布线规则进行设计的。

主要的设计规则如下(单位:μm):

(1)N/P管沟道长度 2.0/2.5

(2)多晶硅最小条宽/间距 2.0/3.0

(3)多晶硅包孔 1.25

(4)多晶硅在场区出头 2.0

(5)有源区最小宽/间距 3.0/2.5

(6)P阱包N管有源 3.0

(7)P阱距P管有源 7.0

(8)P+包有源 2.0

(9)孔最小尺寸 2.0×2.0

(10)铝最小宽/间距 4.0/4.0

(11)铝线包孔 1.0

(12)钝化窗口尺寸 100×100

L82C37A控制电路部分的版图均由标准单元电路版图构成,在版图完成之后,对版图进行了DRC、ERC、LVS检查,以确保其正确性。

2.7 L82C37A工艺研制

L82C37A采用2.0μm硅栅CMOS全离子注入工艺制造。衬底材料为N型硅,晶向为〈100〉,电阻率为6~9Ω.cm。

(1)工艺流程

选片→一次氧化→光刻P阱→P阱注入→P阱推进→预氧化→LPCVDSi3N4→光刻有源→P管场注入→光刻→N管场注入→场氧化→预栅氧化→沟道→调整注入→栅氧化→多晶硅淀积→多晶硅掺磷→光刻多晶→光刻 P+区→P+注入→光刻N+区→N+注入→淀积二氧化硅→源漏区推进→光刻电极孔→溅射Al-Si膜→光刻→合金→钝化→光刻→蒸金→中测→压焊→封装

(2)工艺参数和器件物理参数

一氧:100 nm

P阱结深:≥3.5μm

预氧:50nm

Si3N4:150nm

场氧:900nm

一栅:50nm

栅氧:450nm

多晶:400~450nm

掺磷:R□单晶≤8Ω/□ R□poly≤2.5Ω/□

LPSiO2:600 nm

Si-Al:1.4 μm

钝化(LPSiO2/PESi3N4): 300/500 nm

VTN:0.6~0.9V

ΒVDSN≥16V

VNTL Al/Si≥16V

VTP:0.8~1.2V

ΒVDSP≥18V

2.8 测试

2.8.1 测试程序

L82C37A的工作方式比较复杂,时序要求比较繁琐,测试脉冲的调制也比较严格。对于不同的输入端,根据时序的要求,进行7种不同时序调制,并同时进行两次分级调制。对于I/O读和I/O写分别采用150ns和100ns的归零取反调制,地址线A0-A3采用双向的归零调制。对于数据总线D7-D0也采用归零调制。其它输入采用不归零调制。

2.8.2 测试码点

L82C37A由于功能比较复杂,时序要求又比较严格,测试码点的产生比较长。根据L82C37A的功能特性要求,分成4种不同类型的测试码点图形,有利于进行测试分析。

2.8.3 交、直流参数测试

L82C37A电路的交、直流参数测试是按照参数手册的交、直流参数要求进行测试的。

3 结束语

L82C37A电路在DIC-8032大型测试系统上完全按照手册要求,进行全功能、全参数测试。测试结果表明,各项参数指标均达到国外同类产品的性能参数规范,可替换使用。L82C37A能在-55℃~+125℃全温区、8MHz频率条件下可靠地工作,达到了用户要求,可批量生产.

-

什么是可编程逻辑控制器?可编程逻辑控制器有哪些特点?2021-07-05 3302

-

使用AT89C51实现的微型可编程控制器的讲解2020-10-06 3600

-

可编程控制器基本知识_可编程控制器原理及应用2018-04-25 62173

-

可编程序控制器基础与编程技巧2017-09-19 931

-

高性能的CMOS可编程DMA控制器82C37A2017-09-15 838

-

8237 可编程DMA控制器 altera提供2012-08-10 2037

-

高性能可编程DMA控制接口82C37A-52009-06-12 741

-

8237可编程DMA控制器资料与程序代码2009-04-19 1436

-

82C37/82C37A的内部结构图和引脚功能管脚定义说明2009-03-25 4726

-

82C37A pdf datasheet (CMOS Hig2009-01-08 526

-

可编程控制器(PLC)2008-12-04 1318

-

可编程控制器概述 ppt2008-11-20 1117

全部0条评论

快来发表一下你的评论吧 !