基于AXI总线的DMA控制器的设计

控制/MCU

描述

引言

随着微电子技术的飞速发展,集成电路规模按照摩尔定律(微芯片上集成的晶体管数目每18个月翻一番)飞速提高,片上系统(SvstemOnChip,简称SOC)技术成为国际超大规模集成电路的发展趋势。在SOC系统设计中,为了能够快速、稳定的形成产品,IP核积累和复用技术逐渐成为各个芯片厂商的首选。在这样的背景下,IP复用技术成为了集成电路设计的一个重要分支,很多设计厂商在购买其它公司的IP核的同时,也越来越重视本公司的IP核设计和积累。

DMA控制器是常见的总线设备之一,很多厂商都有自己的DMA控制器IP核。比如嵌入式处理器的龙头ARM公司就有自己的DMA控制器解决方案提供给客户,另外像Freescale,Fuiitsu等芯片制造厂商都有自己的解决方案。本文通过介绍一种基于ARM总线之一的AHB总线的DMA控制器的IP核设计,简述了IP核设计的流程和需要重点注意的地方。

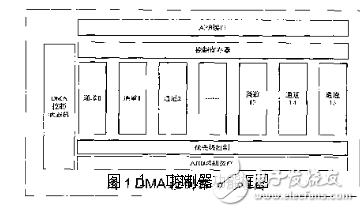

DMA控制器

功能描述

一般而言,DMA控制器的功能与结构是由本单位特定的系统结构决定的。但是作为IP而言,DMA控制器又要有其一般性。DMA是指外部设备直接对计算机存储器进行读写操作的I/O方式。这种方式下数据的读写无需CPU执行指令,也不经过CPU内部寄存器,而是利用系统的数据总线,由外设直接对存储器写入或读出,从而达到极高的传速率

现在DMA也可以在。内存之间或是外设之间直接进行数据操作。DMA技术的重要性在于,利用它进行数据存取时不需要CPU进行干预,可提高系统执行应用程序的效率。利用DMA传送数据的另一个好处是数据直接在源地址和目的地址之间传送,不需要是中间媒介。

通用的DMA控制器应具有一下功能:

1.编程设定DMA的传输模式及其所访问内存的地址区域。

2.屏蔽或接受外设或软件的DMA请求。当有多个设备同时请求时,还要进行优先级排队,首先响应最高级的请求。

3.向CPU或总线仲裁设备提出总线请求。

4.接收总线响应信号,接管总线控制。

5.在DMA控制器的管理下实现外设和存储器、外设和外设或存储器之间的数据直接传输。

空则自动停止写数据。当读数据部分完成了此次DMA传输要求的长度后,状态机进入下一个子状态,等待写数据部分将数据全部写完。当完成全部操作后,DMA控制器会向发起DMA传输请求的设备发出信号,告知DMA传输顺利完成,要求该设备撤销DMA传输请求,并归还总线控制权。至此DMA控制器回到空闲状态,等待下一次DMA传输请求。

一般而言,DMA控制器在总线仲裁器中是优先级最低的设备。因此,当有其它更高优先级的总线主设备要求总线资源时,DMA控制器会被剥夺总线使用的权利,此时DMA控制器将进入等待状态,直到优先级更高的总线主设备释放总线控制权后再进入传输状态。当软件提出申请,完成内存之间的大量DMA传输时,一般会使用LLI功能。LLI功能针对的虚拟内存空间

与物理内存空间映射的不一致性,为了提高传输性能而引入的一种传输机制。作为LLI传输,ARM需要编程给DMA控制器,告知LLI列表的地址,并启动DMA传输。当DMA控制器发现是LLI传输时,它会到LLI列表中读取第一次DMA传输的源地址、目的地址、传输长度以及下一个LLI列表的地址并存入寄存器。当此次DMA传输结束后,DMA控制器会自动到下一个LLI列表中读取下一次DMA传输的信息。这个链表传输过程直到LLI寄存器中的内容为“0”时中止。

基于ASIC的考虑

关于总线

根据AMBA协议,AHB总线支持字节、半字和全字操作。因此DMA控制器在这点上符合AHB协议的要求。DMA控制器默认32位数据线,因此需要根据读写地址以及读数据操作类型将读入的数据放入32位的FIFO中,写出的时候再根据地址和写数据的操作类型将数据从FIFO中放到写数据总线上。如字节操作时,根据读地址从读到的一个字的数据中选取合适的字节放到FIFO中的最低字节;写的时候从FIFO最低部分取数,根据写地址将此字节放到写数据相应的部分,其余位补零。

作为ASIC而言,一般情况下,三态只用于输入输出的管脚上。即使是总线在芯片内部也是将读数据线与写数据线分开使用的。本设计秉承这一原则,将读写数据线分开。

作为DMA传输,地址的变更需要灵。有时候读写地址需要增加,有时候地址需要不变。当增加的时候,也要根据传输的类型决定地址增加1、2或4。

关于复位

复位是ASIC设计中最容易出问题的一环。DMA控制器主要有两种复位方式,一种是上电复位,即异步复位,另一种是软件复位,即同步复位。

异步复位通过将全部D-触发器的Reset端接到复位信号线上,无需时钟就可以实现的复位。一般情况下在上电的时候作一次。而根据功能的需要,当系统出现故障,或软件需要强行中止一次DMA传输的时候,则需要软件通过配置寄存器实现复位功能。此时就需要同步复位。

关于综合

由于DMA控制器工作在高速总线上,总线时钟最高可以达到200M,故在做前端设计的时候要特别注意。

以优先级判断为例。优先级判断本质就是16个数字比大小。为了使时间复杂度最小,不采取经典的“冒泡排序”,而是对半排序法。这样比较4次就可以得到需要的数据。四级MUX对于低频而言不算很困难,但是对于高频而言,为了能够满足时序要求,就需要在第二次比较之后插入一组触发器。

结语

本文讨论了一种基于AMBA总线的DMA控制器的IP核设计,结合这个实际的设计,讨论了IP复用技术的设计方法。这个设计不依赖于具体的FPGA或ASIC型号或工艺,因此其可移植性被大大增加。另一方面本设计综合出来的DMA控制器是20K门,比起ARM公司的DMAC控制器的68K门,在面积方面也有很大的优势。

IP复用技术越来越成为嵌入式系统的发展趋势。这种设计方法顺应了超大规模集成电路的发展潮流,必将成为这一领域发展的方向。

-

一文详解AXI DMA技术2025-04-03 2108

-

ZYNQ基础---AXI DMA使用2025-01-06 3639

-

PCIe控制器(FPGA或ASIC),PCIe-AXI-Controller2024-02-21 2048

-

ZYNQ中DMA与AXI4总线2020-11-02 4990

-

你必须了解的AXI总线详解2020-10-09 8877

-

一文详解ZYNQ中的DMA与AXI4总线2020-09-24 7099

-

dma控制器是什么_dma控制器工作方式2019-11-15 14116

-

dma控制器的组成2019-04-01 12084

-

可提高系统响应速度的DMA控制器SoC系统架构2018-08-24 2426

-

NiosⅡ系统中DMA控制器的原理及应用2017-12-07 3042

-

基于AMBA总线的DMA控制器IP核设计2017-12-06 4332

-

Adam Taylor玩转MicroZed系列67:AXI DMA II2017-02-08 516

-

DMA控制器介绍2015-11-04 4459

-

DMA与DMA控制器2008-12-09 993

全部0条评论

快来发表一下你的评论吧 !