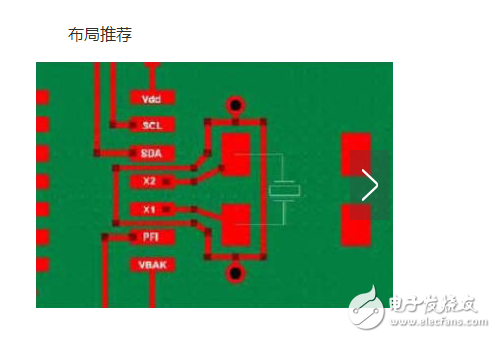

晶振pcb布局布线参考

晶振

描述

晶振 PCB设计

印制电路板(PCB)是电子产品中电路元件和器件的支撑件.它提供电路元件和器件之间的电气连接。随着电于技术的飞速发展,PCB的密度越来越高。PCB设计的好坏对抗干扰能力影响很大.因此,在进行PCB设计时.必须遵守PCB设计的一般原则,并应符合抗干扰设计的要求。首先,要考虑PCB尺寸大小。PCB尺寸过大时,印制线条长,阻抗增加,抗噪声能力下降,成本也增加;过小,则散热不好,且邻近线条易受干扰。在确定PCB尺寸后.再确定特殊元件的位置。最后,根据电路的功能单元,对电路的全部元器件进行布局。

时钟源通常是系统中最严重的EMI辐射源,如果接长线,其结果是长线就成了天线,这在很多应用中是不准许的,所有时钟源都必须尽量靠近相关器件,必要时用多个时钟源,不得以下可以采用多层PCB将时钟连线屏蔽(但这种方法只有在不得以下为之,而且成本未必低于多时钟(多层PCB的价格明显高于双面板),要过某些强制标准的产品尽量不要这么干)。有源晶振的输出一般是标准TTL规格,至于能驱动多少芯片要看这些芯片的特性。

晶振和芯片的距离一般要尽量靠近,一般指的是无源晶振,那么有源的晶振布线有什么要求吗?有源晶振能驱动多少个芯片呢?

有源晶振也不能输出接长线

时钟源通常是系统中最严重的EMI辐射源,如果接长线,其结果是长线就成了天线,这在很多应用中是不准许的,所有时钟源都必须尽量靠近相关器件,必要时用多个时钟源,不得以下可以采用多层PCB将时钟连线屏蔽。有源晶振的输出一般是标准TTL规格,至于能驱动多少芯片要看这些芯片的特性。

时钟布哪一层?

夹心层,其上下都是覆地

但这种方法只有在不得以下为之,而且成本未必低于多时钟(多层PCB的价格明显高于双面板),要过某些强制标准的产品尽量不要这么干。

1. Crystal下不可走線,電路儘量靠近chip端。

2. trace儘量短,與其他信號需20mil間距,最好使用ground trace與其他信號隔離。

3.Crystal底下儘量不要走線。 如果實在要走線的話, 不能走線進Crystal pin腳周圍50mil之內。 尤其避免高速訊號。

晶振信号线尽可能短,需要包地(因为有噪声,本质就是怕它影响到别人,或者怕别人影响到他)。尽可能不穿孔,以为一个过孔会有0.5pF的寄生电容,另外,走线粗细要一致

晶振的选择和PCB布局(一)

晶体的选择和PCB板布局会对VCXO、CLK发生器的性能参数产生一定的影响。选择晶体时,除了频率、封装、精度和工作温度范围,在VCXO应用中还应注意等效串联电阻和负载电容。串联电阻导致晶体的功耗增大。阻值越低,振荡器越容易起振。

负载电容是晶体的一个重要参数,首先,它决定了晶体的谐振频率。一般晶体的标称频率指的是其并联指定负载电容后的谐振频率。应当指出,此处的标称频率是当CL等于指定负载电容时利用公式(1)计算出的值,但不是利用计算出的值。

因此,VCXO的调谐范围与CL的值紧密相关。当负载电容值较小时,VCXO的调谐范围限制在上端;同样,电容值较大时,调谐范围将限制在下端。负载电容的适当取值取决于VCXO的特性。例如,MAX9485设计中,为了均衡调谐范围、调谐曲线中点、同时简化电路板设计,我们选择Ecliptek (ECX-5527-27)具有14pf负载电容的27MHz晶体。

使用这样的晶体时,MAX9485具有±200ppm的牵引范围。应该指出,封装会导致晶体牵引范围的差异。一般金属壳封装比表贴器件(SMD)的牵引范围更大。但是最近DAISHINKU公司生产的一款新SMD晶体可达到与金属壳晶体近似的牵引范围。我们测试了这款SMD晶体(DSX530GA),发现外接两个4pf的并联电容时可以实现±200ppm频率牵引范围。

晶振的选择和PCB布局(二)

为了限制VCXO的调谐范围,可通过改变外部并联电容设置向上的调节范围。并联电容取值范围为4 - 7pf,取决于电路板寄生电容。另一方面,向下的调节范围取决于内部变容二极管值,不能由外部改变。为了降低寄生电容对向上频率调节范围的影响,在电路板布局中应尽可能的减少晶体引脚对地的寄生电容,保证引脚与地层和电源层之间的清洁。

1. X1 和X2 晶体引脚均为高阻引脚,必须小心处理。需确保晶体与X1,X2 引脚之间的连线距离最短,必须小于5mm。

2. 确保VDD引脚具有良好的退藕性。(VDD与地之间连接一个0.1uF电容)

3. 即使信号位于板内层,也不能允许信号线靠近X1 和X2 引脚。在晶体引脚周围使用接地保护环。在内部或板反面使用接地保护敷铜。目前有很多表面封装晶体可用。应当注意:通过图中示意的孔将保护环与地相连。

1. Crystal下不可走線,電路儘量靠近chip端,并且与其输出时钟相关的时钟线走线等长,等阻抗。

2. trace儘量短,與其他信號需20mil間距,最好使用ground trace與其他信號隔離。

3.Crystal底下儘量不要走線。 如果實在要走線的話, 不能走線進Crystal pin腳周圍50mil之內。 尤其避免高速訊號。

系统中最复杂的部分是时钟,100M频率对时钟来说是200M。

FPGA的时钟输入要使用全局时钟引脚。高热下时钟漂移,要加锁相环同步电路。FPGA全部用同步设计,不直接用组合逻辑。

晶振参考最小化设计,电源部分需要加磁珠和小电容去耦,输出加始端匹配(频率不高就不用加匹配,远端有时也要加匹配,防反射,PCI除外),晶振下面铺数字地,多打孔,孔挨着pin。

时钟走线要看你采用什么分配方案。是公共时钟同步还是源时钟同步,要不要加时钟分配器件,加几级驱动。

实际走线长短根据分配方案和拓扑结构具体计算(尽量偏短),时钟分配器件下要铺铜,未用引脚用1K电阻下拉到地。多级驱动要加PLL补偿(补偿值需要计算)。

国产133M及以上晶振不可靠,可以从33M倍频产生133M,这样好选材。要么选日本货等。

时钟输出最好不分叉,实在不行最多分两路(特指低速,高速必须点对点),其他情况必须加时钟驱动。时钟驱动最多带2个负载,分叉后相位可能跑偏。

在布局上,时钟电路周围走低速低压信号电路,远离电源,约束在同层走线,保证阻抗连续,尽量走在少受干扰的内层,晶振不要靠近板边。走等长线的部分周围要留出足够的空间(注意3W规则,100M以上时钟线必须拉圆弧线)。点对点、菊花链结构最常用。晶振下最好不走线,尤其是高速信号线。注意大电容焊盘的特殊处理,要求保证大电流供电能力。

总之,时钟是关键信号线,所有安排一律从优,要特殊照顾。

1.有正弦波输出的贴片晶振,输出负载为10k;如果10k的负载能力不够,必须加缓冲电路,使PLL的参考与单片机的时钟相隔离;

2.晶振输出到PLL的信号线不能长,再加上TTL电平,辐射太厉害了;

3.晶振PCB表面铺地,周围通过过孔与底层大面积地相连;

4.晶振输出接带通滤波器,PLL输出接带通滤波器;

5.对两个PLL分别进行屏蔽;晶振输出接两个PLL,很难把信号线走短,最好是用同轴线从底层连接。

6.主要是做好屏蔽,尤其是接收电路部分,不光要屏蔽,还要考虑接地;

a)缓冲电路是指在你的晶振负载能力很弱的情况下使用,提高驱动能力,还起到隔离的效果,由于你现在使用TTL输出电平的晶振,驱动能力强,而且能改善PLL的带内噪声,所以可以不加缓冲放大器,主要是要解决辐射干扰问题;如果有板子上地方,也可以加一个简单的晶体管限幅放大器,会有点好处。

b)一般超短波频段和微波频段,射频前端均是收发开关或双工器-滤波器-LNA-滤波器-混频模式;短波一般是收发开关-滤波器-混频模式。

c)晶振输出,我做过实验,采用普通的陶瓷滤波器进行滤波,效果是有改善,不过还是不是很理想。 所以我才采用电容强拉波形.

-

晶振的PCB布局设计2022-09-08 5620

-

晶振的布线——设计案例分析2014-10-20 7414

-

晶振PCB布局设计2018-09-13 2999

-

PCB布局时怎么布局好?2019-09-29 2213

-

PCB的布局布线2023-04-24 872

-

PCB布局布线2016-03-22 1136

-

晶振电路PCB布线 晶振问题不可缺少的三要素2020-11-25 5290

-

晶振电路常见问题,晶振电路PCB布局2021-03-14 10960

-

晶振常见问题分析以及对应PCB布局的讲解2022-04-06 7538

-

PCB布局布线技巧104问2023-05-05 1018

-

简述无源/有源晶振的布局布线要点2023-08-15 20086

-

如何优化晶振布局与连接?2023-12-18 1836

-

晶振在pcb布局中注意事项2024-09-19 2595

-

104条关于PCB布局布线的小技巧2025-01-07 1809

全部0条评论

快来发表一下你的评论吧 !