基于SystemC的可配置多通道DMA控制器的设计

控制/MCU

描述

1、引言

在计算机系统里,为了加快传送大批量数据的速度,常采用DMA方式,通过集成片上DMA控制器接口部件实现,在存储器和外设之间开辟直接传输数据通道,DMA控制器的访问策略跟控制协议的好坏,直接影响着整个处理器系统性能的好坏14。文中采用SystemC系统级设计语言,实现了一个快速的可配置多功能DMA控制器。

SystrmC语言是在1999年推出,并由OSCI负责支持。维护和发展目。它是建立C++基础上的开放的系统级设计语言,可同时支持软件级和硬件级的建模,能够实现软硬件协同仿真,还可以将系统逐步细化至用于综合的寄存器传输级,可以有效地简化设计过程,降低设计所需时间,节约成本。

2、DMA控制器的基本组成

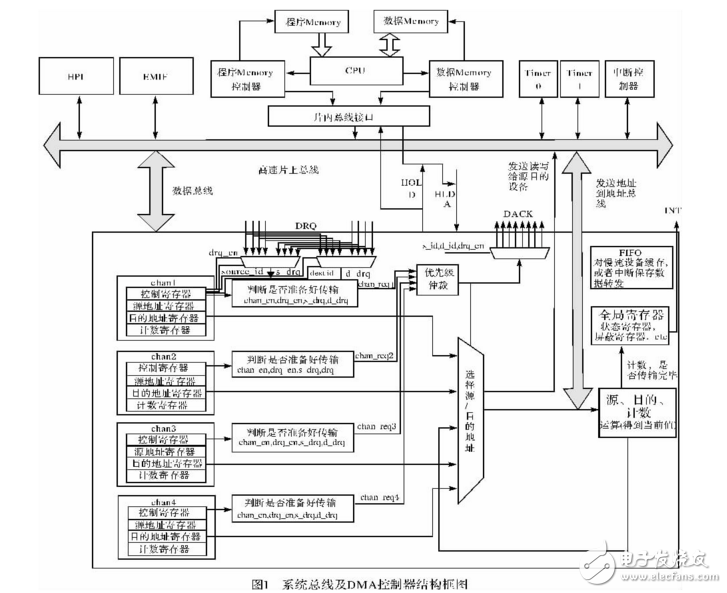

外围设备跟内核进行数据传输或者发送控制信息是通过不同类型的总线实现的O.为了提高整个系统的效率,在处理器中往往存在着不同级别的总线,分别用于连接不同的设备。一级内部总线往往用来实现内核对内部存储器的直接访问;二级系统外设总线用于实现高速的外设跟内部存储器之间的访问; 三级总线则用来连接较低速的外设,并通过桥接器连接到二级总线上。DMA控制器也相当于一个外设,跟中断控制器定时器。外部存储器接口、主机接口。片内有储器接口一起连接在二级外设总线上。

DMA控制器主要由以下几部分组成: 寄存器状态寄存器、控制寄存器、地址寄存器。计数寄存器和屏蔽寄存器) 。数据缓冲器用于接收从源设备发送来的数据,等待转发给目的设备) 。地址计数器运算单元、优先级仲裁逻辑。中断控制逻辑。外设总线DMA控制器的具体结构如图1所示(图中画出的是仅四通道DMA控制器,更多通道的DMA控制器架构与此类似)。

#p#3、DMA方式的工作流程e#

3、DMA方式的工作流程

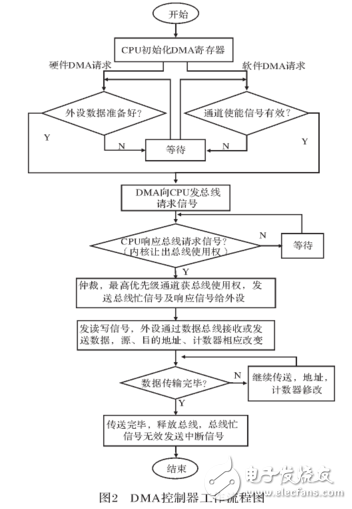

DMA工作方式下的流程见图2具体可以划分为如下4个:主要部 分。

1) DMA传送开始前的准备工作

内核开始进行DMA传送之前,首先执行一系列的IO指令用来检测外设的状态,初始化寄存器。根据设备传输速度的不同。在控制寄存器中设置是否需要等待外设请求信号进行同步。

在设计中,采用两种请求方式来开启DMA传送:软件DMA请求和硬件DMA请求。软件DMA请求一般用来进行速度较快的设备之间的数据传送,假定设备一直处于准备好状态可以随时进行数据的传输,比如存储器;硬件DMA请求则需要等待外设的请求信号到来时才能进行DMA传输,一般用于速度较慢的设备之间的数据传输。在这种方式下,DMA响应设备的请求之后,还会发送响应信号给等待的外设。通过在控制寄存器里面设置一个信息位,预先设置好当前通道的传输是否需要硬件请求信号,即可实现这两种方式的传输。寄存器还设置地址改变的方式。数据传送的大小等等信息,初始化完毕后,内核维续执行其他操作,等待外设数据准备好或者等待DMA控制发送总线请求信号。

2) 获取总线使用权

DMA跟CPU共用一套总线,并且二者都可以作为总线的主控设备,因此,在进行访问的时候,需要考虑到总线使用权的问题,获得总线使用权的设备占用总线进行传输,其余设备等待。DMA通道使能信号有效或者外围设备发送DMA请求信号的时候,DMA发送总线请求信号给内核。要求获得总线的使用权。

内核响应总线请求信号以后,如果存在多个模需要先进行优先级模块同时请求DMA访问的时候,判断。通道之间的优先级可通过寄存器编程,具有最高优先级的通道获得总线的使用权,发送响应信号给对应外设,并发送总线忙信号告知其他模块总线正在被占用。这时,CPU的操作仍可继续进行,遇到需要使用该总线就进入等待。

3)驱动地址、数据总线进行DMA传送

获得总线使用权的通道通过地址寄存器驱动地址总线,选择源设备与目的设备,并发送读写控制信号,同时通过数据总线发送或者接收数据。

DMA的数据传输方式有两种:存储转发方式和直接数据传输方式。对于慢速的设备,采用存储转发的模式,即先将数据接收到控制器中的数据缓冲器,然后再将数据发送到目的设备;对于高速的外围设备,当源地址跟目的地址指向的不是同一设备时,可以采取直接数据传输的模式,数据直接从源设备读出并写往目的设备,这样可以有效地节省时间,最佳的使用方案是将这两种方式有效结合起来进行传输。

每传输完一次数据,源地址。目的地址相应改变。计数器递减,如果数据没有传输完,维续进行传送,否则,转入下一步操作。DMA传送完毕后的处理工作

4)通道上的数据传输完毕后,DMA控制器释放总线,总线请求信号。总线忙信号无效,并采用专门的机制向内核提出中断,以便内核处理器重新获得总线的使用权并执行相应的操作。

但是,中断提出并被响应以后,处理器就要转向执行中断服务子程序,需要占用处理器的执行时间。一种有效的方法是对每个通道设置中断屏蔽寄存位,数据传输完毕的时候,在不要处理器响应时禁止通道提出中断请求。每一个通道都有对应的状态寄存器,用来表示当前数据是否传输完毕。只有通道的数据传输完毕,并且该通道对应的屏蔽位无效的时候,该通道的中断请求信号才有效,,各个通道中断请求信号相或,如果结果有效,就向内核发送中断请求,否则DMA传输继续进行。

4、DMA控制器设计实现

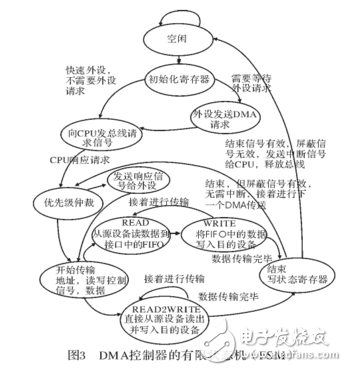

基于前面对DMA控制器工作流程的详细分析。运用SystemC 语言,建立DMA控制器的Cye le-Accurat级参考模型。控制器由以下几个模块组成:寄存器赋值、状态转换。输出模块和顶层模块。具体工作过程可以参考如图3所示的有限状态机。

5 结束语

设计完毕,采用Mode1Sim61进行系统功能仿真验证。片内存储器采用工具生成的SRAM模块,输入激励中需要的地址。数据均采用随机生成的方式进行,对各个通道的寄存器进行随机的初始化赋值后,发送DMA传送请求信号,分析读写的数据是否正确,进行验证。结果表明,文中设计的DMA控制器功能正确并且具有较好的性能。

-

Dialog最新CMIC产品 提供可配置多通道低压差线性(LDO)稳压器2019-05-15 2042

-

关于ADC多通道DMA配置的顺序2021-08-04 1615

-

stm32的dma控制器有多少个通道2021-08-05 984

-

ADC多通道DMA配置的顺序是怎样的?2021-10-21 2648

-

一文读懂DMA控制器2021-12-13 1703

-

基于Avalon总线的可配置LCD控制器IP核的设计2010-02-09 582

-

高数据速率视频完全适合多通道流媒体DMA控制器2017-02-09 509

-

Crossbar的多通道DMA控制器设计2017-12-07 5778

-

ADC—多通道(DMA)2017-12-13 1793

-

dma控制器的组成2019-04-01 12398

-

面向多电源轨系统的 8 通道可配置 1A 降压型 DC/DC 稳压器2021-03-18 839

-

LTC3208: 高电流软件可配置型多显示屏 LED 控制器 数据手册2021-03-21 782

-

LTC3372:60V低智商降压控制器加4通道8A可配置降压DC/DC产品手册2021-04-27 911

-

AT32 MCU DMA通道的灵活配置2023-10-26 2608

-

探索TEA6017AT:数字可配置LLC与多模式PFC控制器的卓越性能2025-12-25 550

全部0条评论

快来发表一下你的评论吧 !