随机脉冲信号采集卡的设计

控制/MCU

描述

在雷达、声纳及工业控制领域中的故障监测系统中,往往需要采集雷达、声纳的回波信号或故障监测系统中的故障信号。由于这些信号是随机出现的,并且这些信号的幅度、脉宽及形状相差较大。有些信号脉宽可能很窄,有的可能较宽,且占空比不均匀。若采用传统的固定采样速率采集方式则不能满足实时处理要求。因为,对窄脉冲采样,要求采样速率很高,若采用连续采样方法,则采集数据量太大,采集数据不能及时处理,不能满足采集信号的实时分析或故障的实时处理的要求。为此研制一种随机脉冲信号采集卡,其基本工作原理为:随机脉冲信号出现时,高速采集电路工作,无脉冲信号时,高速采集电路停止工作。由于在上述方面应用中要求采集的随机脉冲的平均占空比很小,因此采用该随机脉冲信号采集卡采集的数据量不是很大,能够对采集的数据进行实时处理和分析,并满足上述领域的特殊需要。

1 随机脉冲信号采集卡

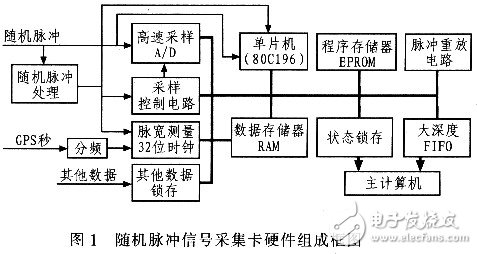

随机脉冲信号采集卡硬件组成框图如图1所示,它主要分为输入输出接口、幅度采集和控制、单片机运行和控制、主机接口控制、信号重放等5个模块电路。

1)输入接口电路 该模块电路主要包括随机信号输入及处理、高速A/D采样、GPS信号输入及分频,其他数字信号输入等电路。

2)随机脉冲处理电路 该模块电路可对随机脉冲进行放大和限幅,放大倍数不小于200倍,确保大于25 mV的随机脉冲信号通过放大后其峰值电平接近5 V,达到TTL电平信号的要求。该信号作为采样控制电路、脉宽测量32位时钟电路及80C196单片机的HIS输入电路的触发脉冲信号,控制脉冲的采集和停止及脉宽测量电路的计数。

3)幅度采集和控制电路 该电路主要包括高速A/D采样电路和采样控制电路等。此外80C196内部也含一个信号幅度采集电路。

4)高速A/D采样电路 该电路对随机脉冲进行高速采样,其采样频率由单片机设置。

5)GPS信号输入及分频电路 该电路是为系统提供标准时间,同时也给脉宽测量的32位时钟提供一个整点的复位脉冲信号。

6)脉冲重放电路 该电路可将采集的脉冲信号数据再转化为对应的脉冲信号输出,用于显示或听音。

7)其他数字信号输入电路 该电路包括主机给单片机提供的一些控制参数(如高速A/D的采样率)和其他输入的一些数字信号(如雷达脉冲的方位和载频等数字信号)。

8)输出接口电路 该电路主要包括大深度的FIFO电路及状态锁存电路等,用于采集卡与主机接口。

2 工作模式

随机脉冲信号采集卡有2种工作模式:一种是采用单片机完成的单一脉冲幅度的测量模式:一种是对特殊脉冲波形测量使用的脉冲幅度高速采样模式。第1种工作模式下,脉冲幅度的测量由80C196单片机内部的A/D转换电路完成,每个脉冲仅采样测量一次。脉冲宽度及脉冲到达时间等虽然可由80C196单片机的HIS(高速输入通道)电路等测量,但因为其测量精度达不到要求,因此,外加了一个32位时间计数器及其相应的2套锁存器等电路用于脉冲宽度及脉冲到达时间的测量。第2种工作模式下,脉冲幅度的测量由外加的高速A/D转换电路完成.高速A/D采样测量电路由每个脉冲的上升沿启动,由脉冲的下降沿触发一个延时电路。延时一段时间后由延时电路的下降沿停止高速A/D采样测量电路。高速A/D采样测量电路的采样率可由主机根据需要设定,最高采样速率可设定为20 MHz。脉宽及到达时间的测量与第1种工作模式相同。

3 系统硬件电路设计

该系统硬件电路主要包括单片机主系统中的随机脉冲放大及限幅电路、脉冲幅度、脉冲宽度测量电路、高速信号采集及存储电路及由EPLD等构成的控制信号电路等。

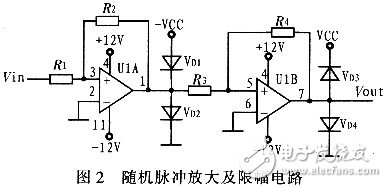

3.1 随机脉冲放大及限幅电路

随机脉冲放大及限幅电路完成脉冲信号的放大、限幅及整形,以满足TTL输入端信号的要求。图2为随机脉冲放大及限幅电路,采用高速运算放大器OPA603,其特点是频带宽且转换速率较高,适用于脉冲放大类电路。输入的脉冲信号通过两级放大及限幅后。输出的脉冲信号送到80C196的高速输入器件的输入端。

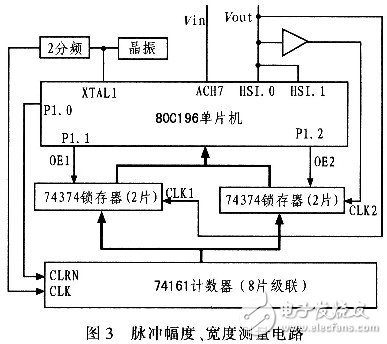

图3为脉冲幅度及宽度测量电路示意图。单片机(80C196)内置的10位A/D转换电路完成脉冲幅度的测量。由74LSl61构成的脉冲计数电路测量脉宽。主系统电路负责整个系统的控制、采样频率的设置及相关的数据处理及控制传送等。其工作原理为:随机脉冲信号(Vin)送入80C196的模拟信号输入端ACH6,然后由80C196的内部的10位A/D转换器进行采样和转换同时该随机脉冲信号经放大、限幅并整形后的脉冲信号(Vout)送高速输入器件的HSI0、HSIl端,作为脉冲前后沿的触发事件,启动中断处理程序。HSI0输入端作为脉冲信号的前沿(上升沿)事件触发输入端,用于读出并记录脉冲前沿到达的时刻及启动A/D转换器进行采样和转换;HSIl输入端作为脉冲信号的后沿(下降沿)事件触发输入端,用于读出并记录脉冲后沿到达的时刻及读取A/D转换器的值。另外整形后的脉冲信号(Vout)有一路信号(CLKl)送到一组7415374(4片)的CLK端,用于锁存74Lsl61计数器的计数值(即脉冲前沿到达的时刻)。通过反相器输出的另一路信号(CLK2)送到另74LS374(4片)的CLK端,用于锁存74LSl61计数器的计数值(即脉冲后沿到达的时刻)。脉冲信号的宽度即为2个计数值的差值。

3.2 高速信号采集及存储电路

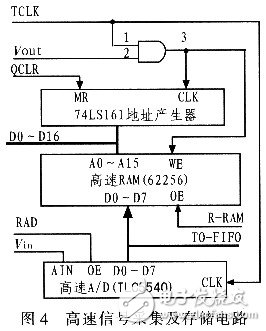

高速信号采集及存储电路用于采集卡在采集方式下时采集输入脉冲的脉内波形数据。采用8位高速A/D转换器TLC5540,其最大转换速度40 MS/s,模拟输入带宽大于75 MHz,具有内部采样和保持功能。

TLC5540进行转换所需时钟信号频率可由单片机设置。A/D转换后的数据自动存储在外接的62256存储器中,其地址信号由4个74LSl61产生。其工作原理为:首先QCLR输出一个负脉冲,将74LSl61计数器清零,然后再设置采样时钟信号(TCLK),启动TLC5540进行转换,同时将RAD信号设为有效(低电平),产生的数据在脉冲信号(Vout为高电平)出现时按顺序写入外接的62256存储器中,脉冲信号(Vout为低电平)消失则自动停止写入。高速RAM的地址信号由74LSl61地址产生器提供。对每个脉冲信号期间采样的次数可根据2个脉冲信号最后写入地址的差值进行来计算,即由单片机读出的该脉冲信号下降沿时刻74LSl61的计数值(即最后写入的RAM的地址),再减去上一次读出的值,即为该脉冲的采样次数。连续采样一群脉冲的波形数据后需暂停采集,将采集的每个脉冲的波形数据与该脉冲的其他参数(如脉冲宽度、脉冲到达时间等)按规定的格式组合后送到与主机交换数据的FIF0高速存储器中,供主机读取和处理,数据送完后再启动采集下一群脉冲。一群脉冲的数量由用户根据实际情况确定,以连续采集的波形数据存入高速RAM中不产生溢出为最大限。图4为高速信号采集及存储电路。

4 系统软件设计

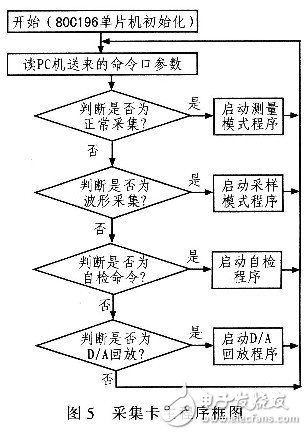

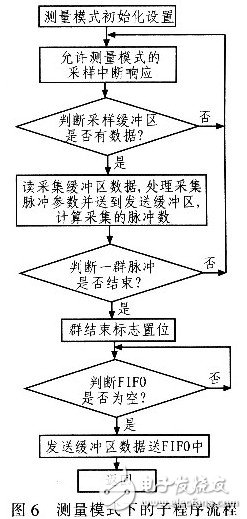

信号采集卡由单片机80C196控制,其中单片机除负责随机脉冲信号的采集外,还承担着将相关的数据(如雷达中的载频数据和方位数据)与随机脉冲数据组织成一个完整的信号数据结构的任务。图5为采集卡主程序框图,其工作流程为:首先80C196通过读取主机(PC机)送过来的命令字,设置采集卡工作模式,执行相应的工作子程序。图6为其中的测量模式下子程序流程,其工作过程为:首先初始化设置测量模式,允许HIS中断。在脉冲出现时,启动测量中断处理程序(HIS中断)工作,启动80C196内部的A/D转换器,对输入的随机脉冲的幅度进行测量,同时读取脉冲到达的时间及脉冲宽度等数据并送到采样缓冲区,退出HIS中断。然后将采集到的随机脉冲数据和同时采集到的其他相关数据(如雷达中的载频数据、方位数据等)存入发送缓冲区,最后按照约定的数据格式组织成数据块存入大深度“先进先出(FIF0)”缓冲器,再通知主机读取这些数据。为保证数据传输的完整性,大深度FIF0被组织成双缓冲区结构,以流水线方式轮流写入和读出信息,从而避免了信号录取卡的CPU和主机CPU同时读/写FIF0时可能出现的数据丢失现象。在采集模式下则需启动高速A/D采集电路工作,并按照波型显示的要求组织数据,然后再送到主机处理。

5 结论

该采集卡设计采用80C196单片机、8位高速A/D转换的TLC5540及EPLD器件实现计数、锁存和其他逻辑电路,并巧妙利用80C196单片机的高速输入通道(HSI)的中断特性,不仅实现了对随机脉冲信号的幅度测量或脉内波形数据采集,同时还记录脉冲到达时间及脉宽,解决了数据采集卡在采集随机窄脉冲信号存在的采集数据量大且不能实时处理的问题。该采集卡已成功应用于某型雷达侦察设备中的信号录取,完全可实时采集、处理接收到的雷达脉冲信号并送往主机,通过主机进一步对采集的信号进行分选和处理,可完全实时显示采集到的雷达脉冲波形。实际应用表明设计的采集卡工作稳定可靠,可采集的最窄脉冲不小于O.1μs,对周期不大于25 kHz的连续脉冲在测量方式下可实现不间断采样。

STM32/STM8

意法半导体/ST/STM

- 相关推荐

- 热点推荐

-

信号采集卡有什么用,信号采集卡支持信号格式有哪些2025-01-29 1998

-

如何使用图像采集卡2024-12-13 1842

-

数字信号采集卡有什么用途2024-05-31 2683

-

数据采集卡怎么用 数据采集卡怎么读取数据2023-12-15 3493

-

如何选择图像采集卡2023-06-27 1722

-

关于图像采集卡的一些基本知识2023-05-25 2237

-

NI 采集卡可不可以变频率输出脉冲信号?2020-04-10 4434

-

有没有技能采集模拟信号又能采集脉冲信号的数据采集卡啊?2016-05-31 4979

-

模拟采集卡和数字采集卡2015-12-09 3547

-

NI数据采集卡可以采集光栅尺输出的脉冲信号吗2012-12-10 12383

-

1394卡与视频采集卡的区别2012-02-13 1784

-

NI USb9234采集卡能否采集差分脉冲信号2011-10-24 9114

-

随机脉冲信号采集卡的设计2010-07-21 625

全部0条评论

快来发表一下你的评论吧 !