PCB布局布线的基本准则及设计考量

PCB制造相关

描述

采用晶圆级封装(wafer-level package;WLP)可降低解决方案的整体尺寸及成本。然而当你使用晶圆级封装IC时,印刷电路板(PCB)将变得较为复杂,而且若未仔细规划,则将导致不稳定的设计。本文章将针对在应用上选择使用0.4或0.5毫米间距的晶圆级封装时,有关PCB设计上的考量及一般的建议事项。

设计系统级线路时,印刷电路板的面积是相当珍贵的。一个降低设计所需PCB面积的方法就是使用较小的IC封装,例如晶圆级封装(wafer-level package;WLP)。若您能依照以下准则进行设计,则PCB将能释很多面积,同时也可节省许多成本。

晶圆级封装体积较它们的前一代技术小很多,这是因为此封装是直接建立在矽基板上,而且毋需使用焊线,如此能缩短周期时间并节省封装成本。然而,为了让PCB的成本维持在最低水准,还是必须采取一些布局方面的考量。此篇文章提出在使用晶圆级封装设计时,一些需遵循的PCB布局通用准则。在进行PCB布局设计时,这些准则能协助增加设计被可靠生产的机会。

SMD与NSMD焊垫

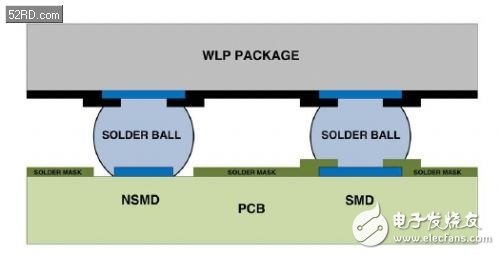

在开始任何布线之前,首先要考虑的应该是WLP占板空间的设计。WLP的设计图将会提供用以建置PCB占板空间的大部分讯息(包括封装尺寸、误差、接脚间距等)。此外,在建置WLP占板空间时,还需要考量用於IC接脚的焊垫类型。焊垫的选择包括焊罩定义型(solder mask defined;SMD)及非焊罩定义型(nonsolder mask defined;NSMD),图1显示了这两者的分别。

图1:在建置WLP的占板空间时,需考虑用於IC接脚的焊垫类型,这可以是焊罩定义型(solder mask defined;SMD)或非焊罩定义型(nonsolder mask defined;NSMD)。

焊罩定义型(SMD)焊垫,顾名思义,就是利用焊罩来定义焊球将会被焊接的焊垫面积。此种方法可减少焊垫在焊接或是除焊的过程中被拉高的可能性。然而这种方法的缺点是,它减少了可以用来作为与锡球连接的铜表面面积,以及减少了相邻焊垫间的空间。焊垫间走线(trace)宽度受到限制,如此可能会影响导通孔的运用。

非焊罩定义型焊垫是利用铜来定义与焊锡凸块焊接的焊垫面积。这种方法提供了较大的表面面积来与锡球连接,同时也提供了焊垫间较大的绝缘距离(与焊罩定义型相较),因此可以允许有较宽的走线宽度,且导通孔的使用上较有弹性。这种方式的缺点则是在焊接与除焊的过程中,比较容易造成焊垫被拉高。

最获推荐采用的焊垫型式是焊罩定义型焊垫。这种形式的焊垫会有比较好的焊锡连接性,可让焊锡与焊垫结合在一起而整个封住。当开始进行晶圆级封装的PCB设计时,必需将这两种型式的焊垫都列入考量,同时针对应用标的来衡量其中的利弊得失。请注意,此两种方法都可被使用在单一的晶圆级封装的占板空间。

间距尺寸是指在IC上,锡球(就是指接脚)之间的距离。这个距离是量测两个相邻锡球中心线到中心线的距离。这个间距越大,则焊垫之间可以用来布线走线的空间也就越大。

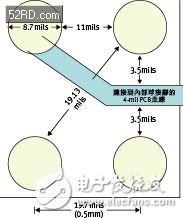

0.5毫米间距的设计比起0.4毫米的设计,提供了稍微多一点的空间。0.5毫米间距的设计可以提供给您的锡球中心线到中心线的空间是19.7密尔(千分之一英寸)。一个典型的焊垫尺寸是8.7密尔,所以在焊垫到布线走线间,有11密尔的空间。在采用走线到锡球(trace-to-solder-ball)间的绝缘距离是3.5密尔的规范时,可以轻易符合在两个定义好的锡球焊垫间的走线最大宽度必须在4密尔以下的要求。在4密尔宽度的走线之下,使用1盎司的铜,你可以把流经走线的电流限制在大约220毫安培。如果使用2盎司的铜,则可以在走线上驱动380毫安培的电流。图2显示了一个0.5毫米间距的晶圆级封装的空间与尺寸。

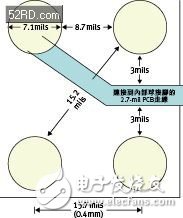

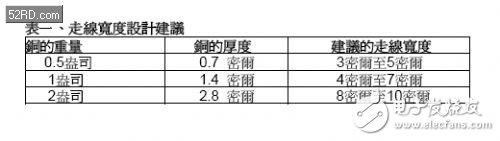

0.4毫米(15.7密尔)间距的设计与0.5毫米设计想较之下有一点棘手,在锡球间可以布线走线的空间少了许多,这也意味着有着较多的限制及较少的弹性。当一个典型的焊垫尺寸是7密尔时,这将留下只有8.7密尔的空间让你在焊垫之间来布线走线。当使用了3密尔来作为每一边与走线内侧距离时,你的走线最大宽度将仅剩下2.7密尔以下。图三显示了一个0.4毫米间距的晶圆级封装空间与尺寸。在2.7密尔的走线宽度下,使用1盎司的铜,将使得流经走线的电流会被限制在大约160毫安培左右。对於像这样0.4毫米的小间距,想要使用较厚的铜可能会有一些问题,因为走线的宽度会比铜的宽度来的小(例如,2盎司铜=2.8密尔)。这将会导致在蚀刻/电镀的制程之後,走线的净宽度会小於2.7毫米。表1提供了由一般印刷电路板制造商所建议的走线宽度与铜厚度的对应表。

布线的选择方案

假如在晶圆级封装焊垫之间采用较薄的走线,也无法符合您的设计需求,例如较小间距的晶圆级封装(例如:0.3毫米)时,则还有其他选择可供采用,但是这些选择也各有其缺点。其中一项选择是使用雷射钻孔式导通孔(laser-drilled via),但这会导致PCB的成本升高许多。必须采用雷射钻孔式导通孔的原因是,机械钻孔有设备上的限制性(像是钻孔器的尺寸最小都在10密尔以上),以及因为晶圆级封装相邻与对角焊垫间,占位空间有限所致。雷射钻孔是印刷电路板工厂的生产制程,在这里是把导通孔用雷射钻孔的方式,直接钻进去或是与WLP焊垫位置偏移,然後再回填,因此可让走线在内层导通。假如在你的应用中,PCB板已经使用了雷射钻孔式的导通孔(像是高阶的音响应用设备或是行动电话等),那麽PCB板的成本将不会是个问题。然而,假如你的应用必需使用较低成本的PCB板(例如液晶显示幕等),则这些额外的成本或许并不值得。

另外一种比较不常见的方法是使用交错锡球凸块阵列(staggered-bump-array)的WLP。藉由在WLP晶片将锡球交错,你可以产生较多的空间来布线较大的走线。不过,并非所有的WLP晶片都可提供豪华的交错锡球凸块阵列,而且这个方法必须在设计一开始的阶段就非常小心。另外一个方法就是你可以使用缺少一些内部/外部接脚的WLP锡球凸块阵列。这样也可以给你较多的空间来下这个导通孔,或是在内层来布线较大的走线。再一次提醒,这种方法也是必须非常仔细,在你设计的早期就必须考虑的非常透彻,同时也需要把备案需求考虑进来。

本文小结

这篇文章提供一些基本准则及设计考量,在您使用0.4及0.5毫米间距的晶圆级封装IC进行PCB布局设计时,这可提供您有用的协助。焊垫的形式(焊罩定义型及非焊罩定义型)、焊垫间所允许的最大走线宽度,以及焊垫间布线方式的选择方案(雷射钻孔式的导通孔、交错阵列式的WLP,等等),在此篇文章中皆有所讨论,提醒大家在使用WLP进行设计要多加注意。

- 相关推荐

- pcb

-

硬件开发的基本准则2012-08-20 0

-

PCB板布局原则和布线技巧2016-07-23 0

-

手机结构设计的基本准则2009-06-18 1249

-

PCB布局的准则和操作技巧2009-11-18 2651

-

PCB布局布线2016-03-22 1025

-

PCB工程师必看:105条布线设计基本准则!2018-01-09 16097

-

PCB布局布线的相关基本原理和设计技巧2022-02-12 5757

-

PCB技术硬件开发的基本准则(一)2021-03-31 2556

-

开关稳压器设计的PCB布局布线2021-11-08 655

-

混合信号PCB布局设计的基本准则分享2023-04-13 910

-

混合信号PCB布局设计的基本准则2023-04-14 1019

-

PCB布局布线技巧104问2023-05-05 699

-

PCB布局、布线、规则设计的高级技巧2023-09-09 3684

全部0条评论

快来发表一下你的评论吧 !