一文了解FPGA双端口RAM操作

电子说

1.4w人已加入

描述

如果需要重读,需要用ram,如果不需要重读的话就用FIFO

双buffer不太好实现错误重传机制!!!!

双buffer作用:

1、跨时钟域

2、完成数据位宽转换

3、完成数据缓冲

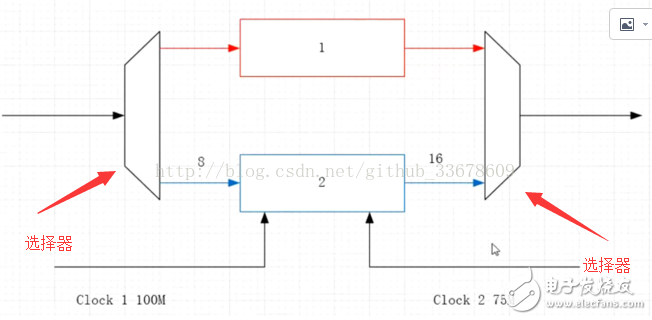

双buffer缓冲操作示意图,在操作工程中存在两个clock1 和clock2,但是输入输出的传输带宽不能相差太大,会出现数据覆盖的现象

1、如上图所示,输入端读数据比写数据速度要块,这样的话,在数据写完后让外部来读,这样在写的过程中,空闲的时间,读端,可以进行数据操作等操作(100MHz * 8bit 《 75MHz * 16bit)

2、写完一次数据就用选择器选择另外一个ram写,在下降沿时切换,读选择器类似。

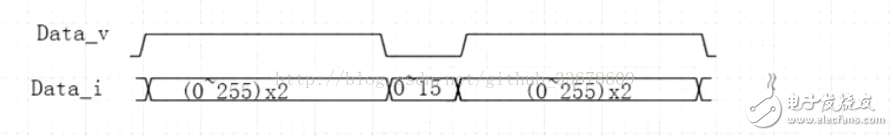

3、快时钟域向慢时钟域传输信号时,需要将写入的片选信号data|_v延迟两拍

testbeach中产生的数据思路

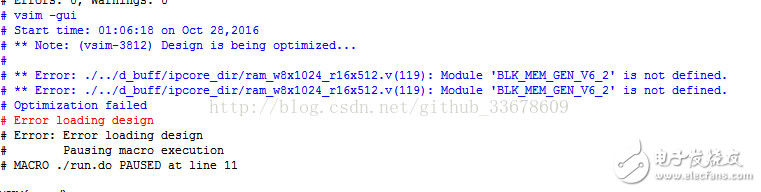

ISE产生的ipcore,不使用ISE自带的simulation仿真,直接用modulesim仿真时出现加入的ipcore找不到相关文件,如图所示

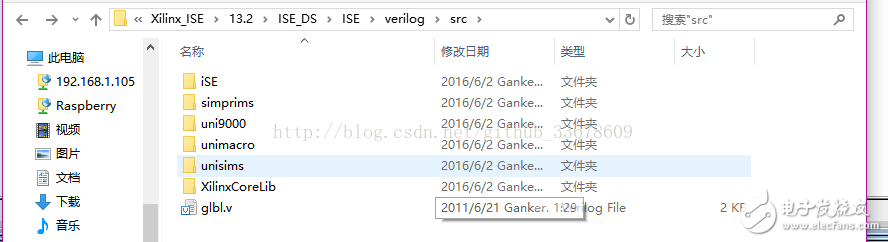

直接到该目录下搜索,然后copy出来到你的工程文件中

声明:本文内容及配图由入驻作者撰写或者入驻合作网站授权转载。文章观点仅代表作者本人,不代表电子发烧友网立场。文章及其配图仅供工程师学习之用,如有内容侵权或者其他违规问题,请联系本站处理。

举报投诉

-

fpga双口ram的使用2024-03-15 2414

-

一文带你了解FPGA直方图操作2024-01-10 1371

-

FPGA双端口RAM的使用简述2023-04-25 9137

-

什么是双口RAM? 基于FPGA的双口RAM有哪些应用?2021-05-06 1852

-

请问双端口RAM在高速数据采集中有什么应用?2021-04-14 1711

-

如何使用FPGA内部的RAM以及程序对该RAM的数据读写操作2021-01-07 4921

-

介绍FPGA开发板内部ram操作2020-09-10 2314

-

简单的双端口和真正的双端口RAM之间的资源使用差异?2019-06-10 3310

-

基于FPGA的双口RAM与PCI9O52接口设计2018-12-12 3230

-

【FPGA开源教程连载】第十三章A 嵌入式RAM使用之双端口RAM2017-01-02 6976

-

基于Actel FPGA的双端口RAM设计2010-11-15 907

-

利用FPGA实现双口RAM的设计及应用2010-04-16 11948

-

双端口RAM的并口设计应用2010-03-03 2137

-

基于FPGA的双口RAM实现及应用2010-02-11 692

全部0条评论

快来发表一下你的评论吧 !