基于边界扫描技术的难题提出了MERGE法边界扫描技术解决方案

RF/无线

描述

雷达,作为一种重要的军事武器装备,在军事上将其形象的比喻成作战指挥员的“眼睛”,在维护国家安全及领土完整中发挥着举足轻重的作用。但随着数字电路设计及制造技术的发展,特别是CAD设计软件的进步及完善,单一的测试方法如ICT(In-Circuit Test)测试、功能测试等已无法满足新型雷达数字电路测试及故障诊断的要求,边界扫描[1]测试将成为今后雷达装备数字电路故障诊断发展的主流技术。

基于对ICT测试、功能测试局限性的深入探讨,以及对边界扫描测试技术的研究与实践,本文提出了“MERGE(组合)”边界扫描测试模型的建立方法,并基于此方法,构建了数字电路便携式自动测试系统,实现了对新型雷达数字电路的高速、准确的测试。系统具有硬件设备小巧、便携,性能稳定、可靠,故障隔离率高等优点,适合于战地级实时维修保障,是大型在线测试、功能测试平台的有效补充,较好的解决了测试设备受制于人及战时应急抢修等问题。

自动测试系统实现

“MERGE(组合)”测试模型的建立

IEEE 1149.1标准明确的规范了边界扫描构建原理及相应的测试方法。在故障诊断过程中,可利用VLSI芯片自带的边界扫描结构及相关测试指令[2],有效的实现对VLSI芯片引脚固定型、开路、桥接等故障类型的检测。但待测试的数字电路模块通常包括边界扫描器件和非边界扫描器件,本文提出的MERGE测试模型可通过已有的边界扫描结构实现对非边界扫描芯片的测试,能够拓展边界扫描的测试范围,提高TPS的故障覆盖率。

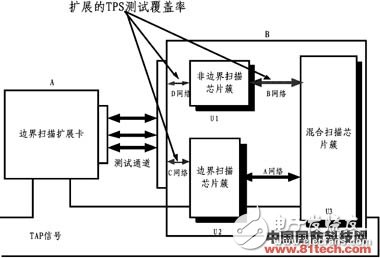

基于边界扫描测试技术的基本原理,构建测试系统过程中创造性的提出了“MERGE”结构测试模型,基本思想如图 1所示。

图 1边界扫描MERGE测试示意图

其中,B部分为待测数字电路BUT,A部分为独立于BUT外的边界扫描扩展卡,该扩展卡可看作是一块符合IEEE 1149.1边界扫描设计规范的数字电路。首先,集中将一个完整的数字电路BUT分为如下几个部分:非边界扫描芯片簇(U1),边界扫描芯片簇(U2),混合芯片簇(U3)。在这里“簇”的概念即将多个器件统称为一个“簇”,簇的范围可以根据具体电路规模来进行划分,可以小到单独的一个IC或 UUT(Unit Under Test),也可大到一个完整的BUT(Board Under Test)。

(1) MERGE非边界扫描芯片簇(U1):非边界扫描芯片是整个BUT网络中一个有序的子集,是具有特定功能的电路。在MERGE理念中,通过对非边界扫描芯片簇建立单独的功能模型,将其作为边界扫描芯片间的一个中间级信号传输模型,MERGE到边界扫描链路,结合EXTEST边界扫描指令,通过 Capture IR--》Shift IR--》Update IR--》Capture DR--》shift DR--》Update DR等相应操作,达到通过边界扫描链路实现对非边界扫描簇测试的目的。

(2) MERGE混合芯片簇(U3):混合芯片簇指既含有非边界扫描芯片,又含有边界扫描芯片的混合电路(还可以含有一些中间级的模拟电路)。MERGE的思路与(1)类似,模型的验证可通过将一组确定的测试矢量集APPLY至MI(Model Input),经过确定的时间延迟,通过在MO(Model Output)将采集(sample)到的响应信号与寄存器中存贮的期望值相比较的方法实现测试。

(3) MERGE BSEC(Boundary Scan External Card),通过BSEC实现对BUT边缘电路中非边界扫描芯片簇或不含边界扫描芯片的BUT进行边界扫描测试。测试时,将待测BUT作为非边界扫描簇或混合边界扫描簇,而将BSEC当作边界扫描芯片簇,通过MERGE方法,将BUT、接口电路、边界扫描扩展卡电路虚拟成为一个含边界扫描芯片的BUT,具体实现与(1)、(2)类似。

测试系统硬件设计

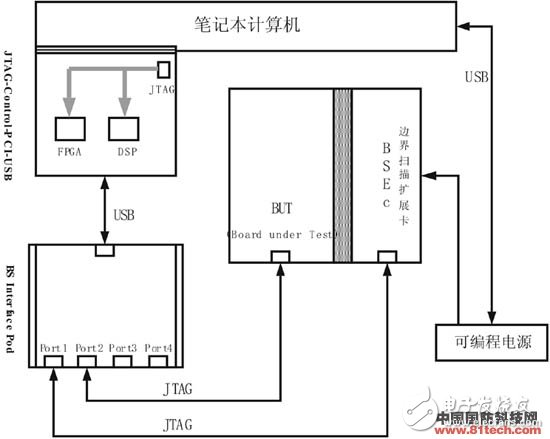

为了减轻系统整机的重量,便于运输及携带,本测试系统前端设备采用笔记本计算机作为主体来完成系统功能的实现和人机界面的交互[3],同时内配 GPIB-USB模块、JTAG-Control-PCI-USB控制器,分别控制可编程电源(Agilent 6600)及BS Interface Pod模块。整个硬件设计的核心为BSEC(边界扫描扩展卡)、JTAG-Control-PCI-USB控制器及BS Interface Pod模块。其系统硬件框图如图 2所示。

图 2系统硬件设计框图

BSEC(边界扫描扩展卡)

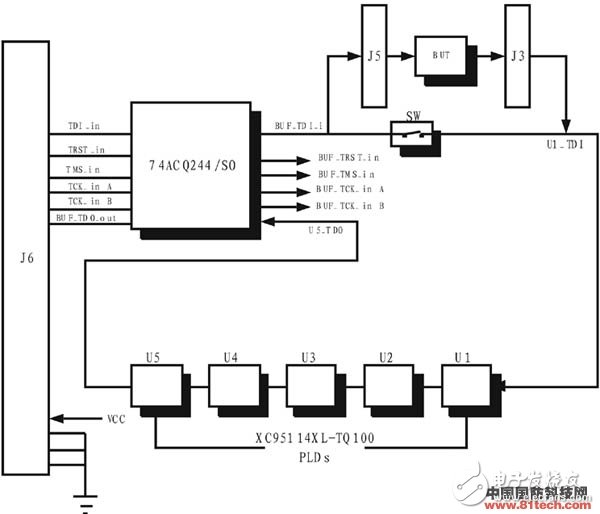

MERGE边界扫描扩展卡采用符合IEEE 1149.1边界扫描标准的可测试性设计方案,应用5片XILINX公司的XC95144芯片构建完整的从TDI至TDO的边界扫描链路,其中扫描链路的上游电路及下游电路采用74ACQ244对信号进行缓冲及整形,以增强上游电路的扇出能力,同时整板的边缘连接器采用了牢固可靠、抗腐蚀的欧式 Eurocard结构形式的连接器,保证测试信号稳定、可靠。原理图如图 3所示。

图 3 MERGE边界扫描扩展卡原理框图

JTAG-Control-PCI-USB控制器

JTAG-Control-PCI-USB控制器是测试系统笔记本记算机与被测试单元(BUT)进行信号控制的主要部件,实现工控机并行控制指令和数据向符合边界扫描测试协议的串行指令和数据的转换。电路采用DSP+CPLD的电路设计模式,DSP芯片采用TI公司的 TMS320LF2407A,运行速度可高达40MIPS(25ns)、具有至少544字的在片双访问存储器DARAM、2K大小的在片单访问存储器 SARAM,32K的片内程序存储器FLASH;CPLD选用ALTERA公司的MAX7000S系列的EPM71285,其集成度为600~5000可用门、有32~256个宏单元和36~155个用户自定义I/O引脚、其3.3V的I/O电平与DSP芯片端口电平兼容、并可通过符合工业标准的I/O引脚JTAG接口实现在线编程及调试。JTAG-Control-PCI-USB控制器是PCI/IEEE 1149.1标准的主控单元,当与BS Interface Pod结合使用时,控制IEEE 1149.1标准自适应测试总线及与之相适应的离散信号。同时,该控制器还可控制施加到测试总线上负责JTAG-Control-PCI-USB控制器与 BS Interface Pod进行通讯的低电压差分信号(基于TIA /EIA-644及IEEE 1596.3标准)。

BS Interface Pod模块

BS Interface Pod模块,作为测试输入/输出信号传输的中间级模块,主要实现JTAG-Control-PCI-USB控制器与BUT之间测试通道的扩展和信号的同步与缓存。FPGA(Altera公司,EP20K160EBC365-1)是本电路设计的核心,其功能是将前级JTAG-Control-PCI-USB 控制器发出的不同的控制信号转换成UUT测试终端能够识别的TAP控制信号,保证TDI、TCK、TMS、TRST准确施加到UUT的测试端,同时将采集到的TDO信号返回给测试前端控制模块。74LVC125(Buffer)则用来完成信号暂存,输出级的74LVC125还可增强信号的扇出能力。整个 BS Interface Pod模块采用抗EMI(电磁干扰)屏蔽封装,前面板预留4个20Pin的JTAG控制端口,另外设计了一个电源指示灯,用于上电确认。

测试系统软件设计

系统软件在Windows XP环境下采用Visual C++6.0及National Instruments公司的LabWindows 6.0集成开发环境完成。Visual C++ 6.0能够提供丰富的Windows程序开发功能,灵活性强、编程效率高;LabWindows 6.0提供了多种接口协议、丰富的控件及仪器驱动程序,其支持虚拟仪器技术的特性是其它开发环境无法比拟的,同时它提供了丰富的软件包接口,为软件开发提供了极大的方便[4]。

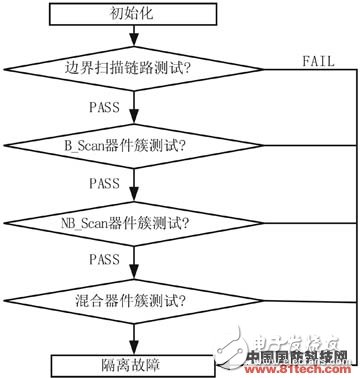

软件设计采取了软件模块化及自顶向下的设计原则,首先根据MERGE原则划分电路模块,将测试程序分割成不同的测试模块,其次采用宏的方式构建标准的测试模块并优化模块接口,然后将其它待测模块与该模块接口进行有效链接,再分别进行编译及调试,最后一起进行合并构建完整的测试体。在开发过程中,将该软件分为若干模块不但减少了软件的工作量,而且对于函数的公共部分进行了类的封装,提高了模块的复用性[5],同时提高了软件本身的可测试性。系统软件流程如图 4所示。

图 4 软件工作流程图

测试优化

为减少ATE在故障诊断中误判的概率,系统采用加权伪随机向量关系生成、插入间隔刷新测试矢量优化测试矢量和测试过程。

(1) 加权伪随机测试矢量生成:加权伪随机测试矢量生成能够利用较短的测试码长度(即较短的测试时间)达到较高的测试故障覆盖率。为了缩短测试码并改进故障覆盖率,这种测试矢量生成方式可以调节在输入端产生0或1的概率,有效检测到难检测的故障。在伪随机测试码中,每个输入端产生0或1的概率为50%。

(2) 插入式间隔刷新:由于数据线具有一定的电平保持特性,因此对于一组数据总线I/O而言,在BS-Cell处于读状态时(如处于Update状态),Cell单元的Output Enable Control Cell处于有效状态,测试矢量通过BS-Cell施加至I/O数据总线,如果下一个时钟节拍,BS-Cell处于写状态(如处于Capture状态),由于数据线的电平保持特性,则有可能在此时间,BS-Cell所Capture回读的数据为上一个时钟节拍的Update数据,造成测试不稳定。解决的办法是在每一次读状态结束后,系统根据读状态的间隔时间,随机产生一组与上一组测试矢量不同的数据,命名为*data,对I/O总线进行间隔刷新。

实验结果及分析

现以某新型雷达点迹处理数字电路为例进行系统功能验证。整个电路采用DSP+FPGA的设计架构,其主要芯片包括:5片 DSP(ADSP21060)、2片FPGA(Atlera Flex EPF10K系列)、8片双口RAM(QFP封装),其他E2PROM、HC244(SOP封装)、HC245(SOP封装)等。电路设计复杂,芯片多,PCB布局布线密度大,采用ICT、功能测试TPS开发难度大。

利用本边界扫描自动测试系统,结合MERGE方法,对上述电路板进行TPS开发实验及故障诊断,测试结果如图 5所示。

图 5 测试结果示意图

插入模拟故障(U8-6 stuck to 0),重新仿真:扫描链测试--》PASS--》B-Scan器件簇测试--》PASS--》NB-Scan器件簇测试 --》Failed (Report: Pin(s): U3-25, R26-2, U8-6, R26-1 possible stuck at low, the BS nodes is U31-21(R/W))。

上述仿真结果表明,融合MERGE方法所构建的基于边界扫描的板级自动测试系统,自动化程度高,故障隔离准确有效。

结语

边界扫描技术可以实现对数字电路的高速测试,不但可以减少ICT测试高昂的夹具开发成本,缩短测试时间,还能够满足时延故障和芯片性能测试的要求。本文主要针对基于边界扫描技术的测试系统实现难度大、故障覆盖率低等问题,创造性的提出了MERGE法边界扫描技术。通过对该方法的深入研究,构建了基于该技术的新型雷达数字电路便携式自动测试系统。经综合评定该系统性能可靠,符合我军新型雷达装备维修保障的要求,具有良好的发展前景。目前该ATE正担负着新型雷达装备数字电路的维修保障任务,其整体设计思路对同类型故障诊断平台的研发具有重要的借鉴价值和参考意义。

-

什么是边界扫描?JTAG边界扫描测试方案介绍2023-09-22 6313

-

边界扫描测试技术介绍2022-02-17 1227

-

高速边界扫描主控器设计2009-04-03 518

-

边界扫描测试技术在硬件实验中的应用2009-08-18 790

-

基于广义特征分析与边界扫描技术的混合信号测试系统2010-11-19 850

-

边界扫描与电路板测试技术2006-03-11 2157

-

基于USB总线的边界扫描测试系统2011-07-04 838

-

基于边界扫描技术的板级测试分析2012-05-30 1468

-

简述BSDL边界扫描语言,BSDL边界扫描语言的应用2017-04-19 9482

-

边界扫描测试的基本原理及其测试系统的设计2017-12-01 1353

-

边界扫描技术的详细资料描述2018-12-04 1283

-

边界扫描测试解决方案的原理及应用分析2020-04-13 14116

-

基于MERGE边界扫描测试模型实现雷达数字自动测试系统的设计2021-03-29 3421

-

JTAG(四) 边界扫描测试技术2021-12-20 1098

-

基于Xilinx FPGA的边界扫描应用2023-09-13 3043

全部0条评论

快来发表一下你的评论吧 !