机载SAR天线平台自动化测试系统的测试模块设计分析

RF/无线

描述

SAR(specific absorption rate, 电磁波吸收比值)天线平台从机载惯性导航设备获得飞机的即时偏流角、俯仰角、滚动角数据,利用这些数据控制天线平台的运动,使平台在方向位保持与飞行地速方向一致,在俯仰和滚动方向保持水平。天线平台的跟踪性能的好坏,将直接影响SAR的成像质量,所以有必要对天线平台的伺服性能进行测试。

本文介绍了一种基于 PXI总线技术的SAR天线稳定平台测试模块。该测试模块是SAR天线平台自动测试系统的主要子系统,主要完成仿真转台位置信号解码及输出、平台跟踪误差信号采集以及信号分析处理等功能。

PXI总线技术简介

PXI总线技术是NI发布的一种全新的开放性、模块化的仪器总线规范,是PCI总线在仪器领域的扩展。它将CompactPCI规范定义的PCI总线技术发展成适合于试验、测量与数据采集场合应用的机械、电气和软件规范。PXI总线与台式PCI规范具有完全相同的性能,是在 PCI总线内核技术上增加了成熟的技术规范和要求形成的。它通过增加用于多板同步的触发总线和参考时钟、用于进行精确定时的星形触发总线以及用于相邻模块间高速通讯的局部总线来满足试验和测量用户的要求。PXI规范在CompactPCI机械规范中增加了环境测试和主动冷却要求,以保证多厂商产品的互操作性和系统的易集成性。它定义Microsoft Windows NT 和Windows 95为其标准软件框架,并要求所有的仪器模块都必须带有按 VISA规范编写的Win32设备驱动程序, 使PXI成为一种系统级规范,保证系统的易于集成与使用,从而进一步降低最终用户的开发费用。

测试模块的结构

作为基于Windows平台的PXI总线测试卡,该仪器模块包括PXI插卡和主机驱动程序软件两部分。PXI插卡负责测试数据的处理,主机驱动程序负责通信。

PXI插卡的结构

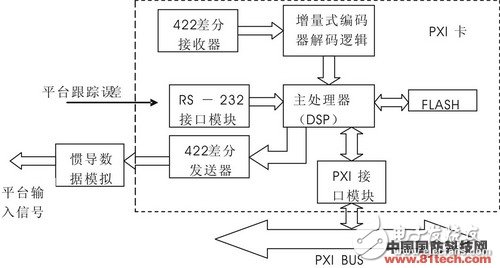

PXI插卡从功能上分为增量式编码器解码模块、RS-232接口模块、 DSP主处理器以及PXI总线接口三部分,该测试卡的结构如图1所示。增量式编码器解码模块与422差分接收器配合,用于天线仿真转台两轴位置数据的解码;DSP主处理器完成测试数据的处理,PXI接口模块主要完成PCI总线信号到本地总线的转换接口;RS-232接口模块接受PSD(光敏位置探测器) 的串行输出信号,PSD在测试系统中用于探测天线平台的跟踪仿真转台运动的误差。

PXI插卡的结构

图1 PXI插卡的结构

PSD串行输出信号的读取

测试系统采用PSD处理电路通过标准异步串口每5ms发送一帧数据,用TI TMS320VC5510作为主处理器,满足了数据存储空间的要求(内部有多达176KB RAM),但它只有用于同步通信的McBSP,不能直接实现异步串行通信,需要配合DSP的DMA通道通过软件实现异步通信。将PSD发送的每一个字节作为一帧数据,以起始位的下降沿作为帧同步信号,采用过采样的方法,将每一位(包括起始位)作为一个16位Word,停止位仅采8位WORD。将一个字节通过DMA通道缓冲到固定缓冲区,当一帧数据(10个WORD)全部采完之后,发送DMA中断通知DSP进行处理。对于串行通信普遍存在的开机错位乱码现象,通过对特殊位的判断进行丢弃处理。

增量式编码器解码模块设计

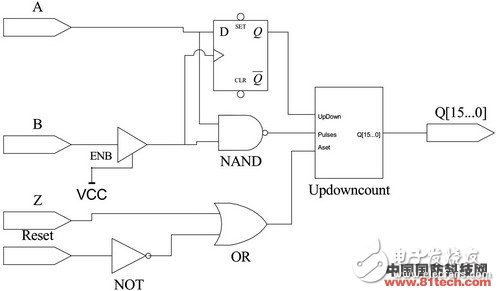

该测试模块需要从天线平台测试仿真转台接受平台的位置信息,在各类运动控制系统中,常采用增量式光电编码器作为反馈检测元件,其输出为相差90度的A、B 两相信号以及周期脉冲复位信号Z,A、B两相信号相差的正负决定运动的正反方向,A、B两相信号的脉冲输出计数决定位置运动的大小,Z为过零复位脉冲。整个解码逻辑设计如图2所示,由于该测试系统采用的仿真转台的位置信息有方位、横滚两个方向,需要两组解码器分别解码两个方向的位置信息。

解码逻辑设计

图2 解码逻辑设计

主处理器的工作流程

DSP是该测试卡的关键部件,担负着数据处理、存储、模拟惯导数据产生以及与上位机通信等任务。DSP以PSD发送数据为时间基准,接收到PSD每隔 5ms发来的数据并存储后,首先通过EMIF(Extern Memory Interface,外部存储器接口)从增量式编码器解码模块中读取计数器的计数值,经比例运算转换成两个16位角度量后,存储并通过EMIF接口发送给外部的惯导数据模拟模块,转换成惯导输出的自整角机信号发送给稳定平台。为了保证连续记录数据,数据存储在DSP的DARAM(Dual -Access RAM,双口RAM)中,并采用乒乓式的存储(即有两个存储区,当其中一个存储区满之后,通过PXI总线向上位机发中断,然后开始向另一个存储区写入数据)。我们设定每个存储区存储1000组数据(每组包括电控转台方位、横滚姿态以及平台在这两个方向上的跟踪误差4个数据),故每个存储区包括 4000Words。

PXI总线接口硬件设计

本测试卡使用DSP的16位EHPI(Enhanced Host-Port Interface,增强主机接口)与PCI 9030芯片的Local总线相连,EHPI可以通过DMA控制器在不干扰DSP系统正常工作的情况下读取DSP内部DARAM,内部 SARAM(Single-Access RAM,单口RAM)以及部分CE0片选的外部存储空间,多达1MB。这样上层计算机既可以通过PXI总线在DSP内部存储区获取所需要的测试数据,而不至于影响DSP的正常工作。

PXI总线接口驱动程序

该测试模块工作在Windows 2000操作系统中,需要开发相应的WDM驱动程序,该驱动程序主要完成访问PCI 9030配置空间、访问DSP内存空间以及中断处理、应用程序与驱动程序的通信3个功能。DSP采用两个存储区进行乒乓式的存储,当一个存储区内的数据准备好之后就通过PXI总线向计算机发出中断,驱动程序处理中断,并读取该DSP存储区中的数据。

考虑到采用面向对象的驱动程序框架,简化驱动程序的开发过程,这里选用基于Windows DDK作为底层支持的DriverWorks作为驱动程序的开发平台,其中的DriverWizard向导工具在VC环境中可以建立驱动程序的框架,这里主要介绍一些驱动程序中的几个功能模块。

(1)访问9030配置空间。在生成驱动程序框架的时候已为9030的配置寄存器声明了所需的存储器映射资源,产生一个KMemoryRange类实例 m_MemoryRange,这个类在驱动程序初始化时获得9030硬件寄存器配置空间的地址范围,这样就可以使用该实例的inb和outb分别实现对硬件寄存器的读写操作。

(2)访问DSP内存空间以及中断处理,即对DSP存储区进行读写操作。在生成驱动程序框架的时候已为9030的局部总线空间申明了所需的存储器映射资源,产生一个KMemoryRange类实例m_LocalAddSpace0,这个类在驱动程序初始化的时候获得9030的局部总线地质空间的系统地址范围;同时驱动程序也产生一个KDeferredCall类的实例m_DpcFor_Irq,用于调用中断延迟处理程序DpcFor_Irq()。当测试卡产生中断时,驱动程序捕获中断,作相应处理之后通过m_DpcFor_Irq调用DpcFor_Irq()。在DpcFor_Irq()中,通过 m_LocalAddSpace0的inb和outb对DSP存储区进行读写操作。把读到的数据存放在事先申请的系统缓冲区(这里只涉及到读操作)。

(3)应用程序和驱动程序的通信。首先应用程序通过操作系统提供的API函数调用驱动程序的读写例程Read()(这里只涉及到读操作)。由Read() 例程中调用StartIo()对读请求进行排队,以避免读写操作冲突。由StartIo()调用SerialRead()例程进行具体的读操作,即把事先申请的系统缓冲区中的数据转移到用户缓冲区,完成所要求的读操作。

结语

作为机载SAR天线平台自动化测试系统的核心,该模块以主流的仪器总线PXI总线为载体,保证了测试系统的稳定性和工业级要求,通过标准串行接口读取平台伺服系统的响应(误差),实现了对平台静态跟踪误差的测试和动态响应的实时数据采集。这些关键技术是该自动化测试系统实现设计功能的基础,同时也使该模块不仅具有独立于测试系统的通用性,而且具有对不同类型机载SAR稳定平台的通用性。实际测试证明,该模块实现了预定的功能,能够可靠的工作。

-

电源模块的短路保护如何通过自动化测试软件完成测试2025-09-03 1010

-

电源测试怎么自动化?电源模块自动化测试系统如何实现?2023-12-15 2235

-

什么是自动化测试框架2023-04-18 1696

-

智能天线S参数自动化测试系统NSAT-1000方案参数分享2022-03-15 3800

-

求一种基于PXI总线的SAR天线平台测试模块2021-05-12 1217

-

自动化测试系统问答2020-10-12 2581

-

如何使用PXI总线实现一个SAR天线平台的测试模块2020-08-12 837

-

一种基于PXI总线技术的SAR天线稳定平台测试模块介绍2019-07-17 2100

-

开关电源自动化测试系统的设计与实现2018-11-29 3762

-

出售蓝牙耳机PCBA成品自动化测试系统2018-09-25 2050

-

ATE自动化测试系统是什么_ATE自动化测试系统介绍2018-05-23 33343

-

基于PXI总线技术的SAR天线稳定平台测试模块2017-12-09 1145

-

一种SAR天线平台测试模块2011-08-01 1267

-

位置敏感探测器PSD在雷达天线稳定平台测试中的应用2009-07-16 919

全部0条评论

快来发表一下你的评论吧 !