PCIe闪存控制器技术解析

存储技术

描述

我们知道闪存磁盘是在HDD以后出现的,由于SSD优异的随机性能、越来越大的容量和越来越低的成本等优势,使得闪存热度上升、乃至大有替换HDD的趋势。由于历史继承性等原因,SSD在设计是也是借鉴了部分HDD技术,包含接口技术。

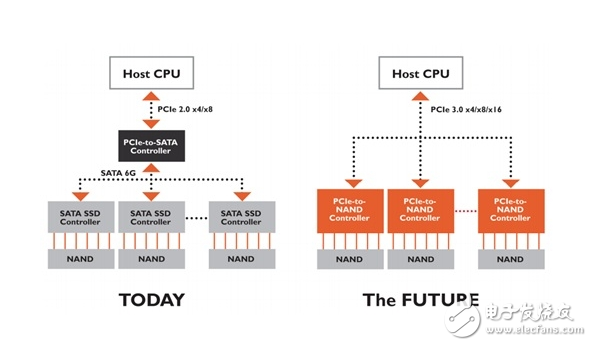

现在绝大多数SSD都是采用SATA/SAS接口,但是通用的SATA/SAS接口是针对HDD设计,但面对闪存速度上百倍的提升,接口的带宽就成为了I/O的最大瓶颈;随后PCIe接口的SSD也得到广泛应用来应对高性能要求;美光也开始探索串行NOR闪存接口。

到目前为止,大部分存储厂商都推出了对应的PCIe闪存卡(如 EMC XtremSF PCIe SSD卡 )和磁盘。

PCIe-SSD架构解析

PCIe作为CPU的局部总线,最大的特点在于数据传输吞吐量大和延迟低。对于NandFlash固态存储而言,传统磁盘存储领域存在的随机读写问题将不复存在,因此,整个存储系统的瓶颈从存储介质转移到了传输接口上来了。为存储而生的SATA/SAS接口在SSD上的表现不是那么理想了,非常影响IO的传输延迟。为此,显而易见,存储接口应该从传统的SATA/SAS往离CPU更近的系统总线PCIe或者DIMM方向发展。

大家其实很早就认识到了这一点,当年Fusion-io推出基于PCIe的闪存卡时,让整个业界为此眼前一亮,原来闪存也可以这么玩?为此,Fusion-io在前几年都一直非常的红火。NandFlash本身不是一个新东西,基于NandFlash的存储在电子设计领域,以及移动存储领域早就开始应用了。但是,将NandFlash作为数据中心的存储介质、在消费电子领域替代磁盘,也就发展了没有多少年。作为磁盘存储的第二选择,很多芯片厂商提供了基于SATA、SAS接口的NandFlash控制器,例如Marvell、LSI都有类似的芯片。

但是,为了能够充分利用NandFlash存储介质的特性,SATA、SAS接口本身就是一个性能瓶颈点。这两年基于PCIe接口的SSD存储一直在蓬勃发展,由于整个行业处于军阀混战的年代,nvme标准还没有充分的得到落实,所以,这方面的接口控制器也就五花八门,个具特色。

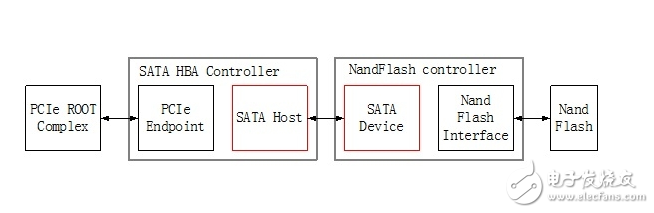

在市场早期,很多厂商为了能够快速进入市场,利用现有技术很快构建出了PCIe接口的闪存卡。典型的产品如上图所示,这是一款Oracle(SUN)的PCIe Flash卡,采用4个Marvell闪存控制器的SATA闪存模块,通过LSISAS1068E控制器连接到PCIe总线上。这种结构将已经成熟的HBA控制器和基于SATA/SAS接口的NandFlash控制器技术结合了起来,具体如下所示:

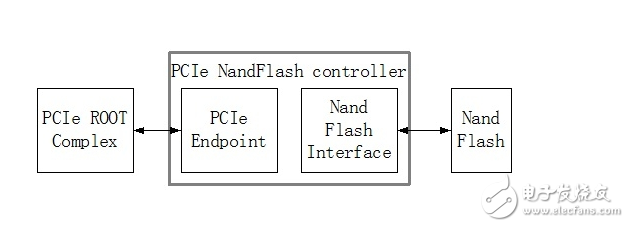

从技术的角度来看,采用这种方案显然引入了延迟,中间多了一层SATA/SAS接口的转换。所以,这种卡的性能往往会比Fusion-IO的性能要差。原因在于Fusion-IO没有采用这种简单的技术堆叠,而是采用FPGA自己做了一个基于PCIe的NandFlash控制器。采用这种技术方案的结构如下图所示:

上述方案最大的好处是降低了IO延迟,去除了无谓的SAS/SATA接口层,使NandFlash直接连到了PCI总线上。这种直接基于PCI总线的技术方案也被称之为Native PCIe方案,并且已经成为各个厂商公认的未来闪存存储的技术路线之一。所以,从芯片厂商的角度出发,急需需要研制基于PCI接口的闪存控制器,替代现有的接口转换方式。

如今以Intel为首的Nvme标准如火如荼的推进,并且慢慢的被各大厂商接受。一旦Nvme标准大范围的应用,基于该标准的控制器将会大量涌现,到那时,基于PCI总线的闪存存储将会和现在的SATA/SAS存储一样,成为应用主流。有时候在想,Fusion-IO为什么当年没有和Intel进行合作?或者为什么Fusion-IO没有自己来推动闪存控制器的变革,让更多的厂商一起加入到这个游戏圈中来?从短期来看,Fusion-IO的产品有很大的价值,但是,从长期来看,更大的价值在于控制器、基于Nandflash存储软件的标准化。Flash存储的市场空间巨大,标准化会是大势所趋。虽然Fusion-IO发展很早,但是,没有赶上标准化的快车,因此,标准化的集团军会对Fusion-IO进行围剿,从而导致Fusion-IO发展困难。

分析闪存控制器的架构,首先得了解SSD。一般来说SSD的存储介质分为两种,一种是采用闪存(Flash芯片)作为存储介质,另外一种是采用DRAM作为存储介质。我们通常所说的SSD就是基于闪存的固态硬盘,其采用FLASH芯片作为存储介质。SSD的基本组成结构包括Flash颗粒和Flash控制器,Flash控制器中有芯片,负责Flash的读写、磨损均衡、寿命监控等等。

Flash控制器的主要的工作任务包括三大方面:一是后端访问Flash,管理后端Flash颗粒,包括各种参数控制和数据IO; 二是前端提供访问接口和协议:实现对应的SAS/SATA target协议端或者NVMe协议端, 获取Host发出的IO指令并解码和生成内部私有数据结果等待执行;三是FTL层核心处理。下面我们具体来介绍一下Flash 控制器是怎样做这几件事的。

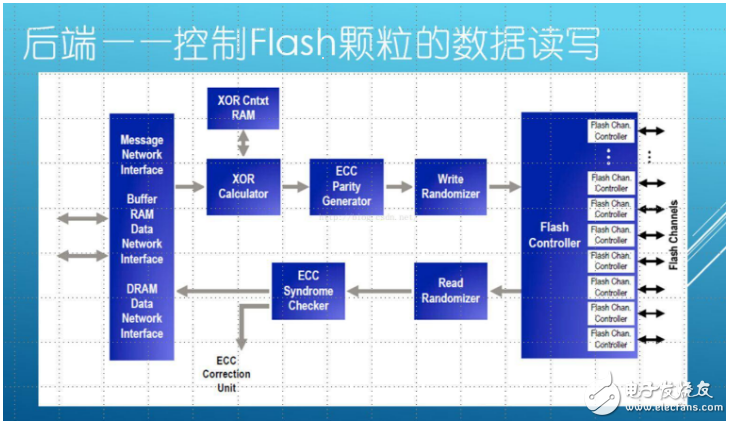

第一,后端访问Flash的操作内容

后端访问Flash首先必须提到的是闪存通道控制器。这个控制器里面有多个通道,每个通道挂多片Flash。它与后端Flash颗粒之间存在托管协议。数据写入Flash的时候,除了主机发送的数据或者原始数据,其他数据都必须进行ECC校验。ECC是通用的称谓,里面有多种算法,其中包括纠错率较低的BCH算法,LAPC低密度校验码等。数据读出的时候,通过扰码,加扰,解扰,看ECC是否出现错误,若有错则在纠错后将芯片发到内部,供后续的程序处理。因此,后端访问Flash的主要任务即是管理后端Flash颗粒,包括各种参数控制和数据IO。

第二,前端提供访问接口和协议

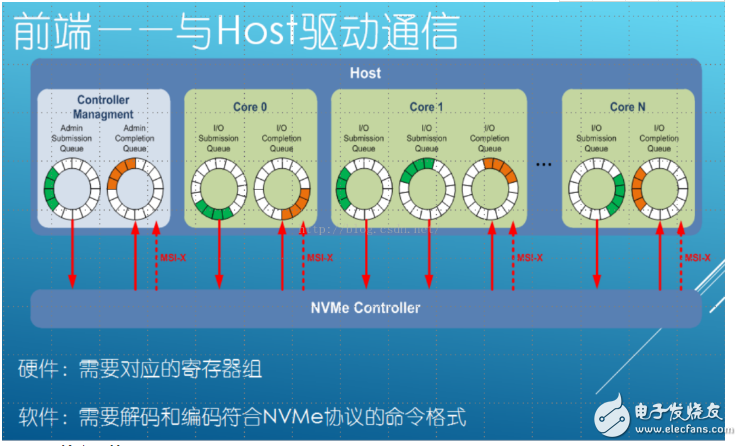

前端提供访问接口和协议,跟主机驱动通信,利用标准格式输配到系统里面,接收主机端发过来的指令,即完成、实现对应的SAS/SATA target协议端或者NVMe协议端,获取Host发出的IO指令并解码和生成内部私有数据结构等待执行。如果遵从NVMe标准,包括提交命令的方法、完成命令的处理方法等都定好了,包括各种队列、队列深度,Queue Pair的总体数量最大可以达到64K个,队列深度也可达64K个,所以,系统里同时可能存在64K×64K IO排着,但是目前的系统是用不到这么多Queue的,因为底下的介质速度还不足以支撑。

第三,FTL层——核心层处理

核心层FTL层,是一款Flash控制器的关键竞争力所在。它既可以是纯软件算法,包括元数据管理,数据布局影射、磨损均衡、垃圾回收、缓存策略、片间RAID和掉电元数据一致性保障等内容。同时,它也可以在进行重复性工作时辅以硬加速引擎。这是非纯软件的,辅有硬加速的成分在里面。硬加速涉及到所使用的芯片。有的芯片支持硬加速,比如说链表的维护。这是因为做垃圾回收时需要要用到链表,拿传统的软件算法,插入一个或者追加一些项目,所耗费的CPU周期较大,此时用硬加速并行,再加上一些硬逻辑的加速,则可节省开销。

Flash控制器的两种策略和方式:

现有的Flash控制器可采用两种方式:一种是少量的强核心加少量硬件加速。所谓强核心就是一个核心的性能高、频率高,分支预判、并行度、单元数量、执行管道,各种参数都高于一般水平。核心强了以后,硬加速就不需要这么多了,可以用少量的硬加速。

另一种方式则是大量弱核心+大量硬加速。比如说16个核心,每个核心比较弱,但是能够增加执行的并行度,有16个并发核心执行,跑16套处理程序,这是两种架构。这是一种多核心协作架构模式,其协作方式可以是同构协作也可以是异构协作

1. 同构协作就是每个核心做的事都是完全一样的,处理的步骤完全一样。如果你的控制器阵列里面有16个IO,有16个核心,每个核心都能处理一个IO,这是同构协作。

2. 异构协作则是多个核心做不同的事情。处理同一个IO,第一个IO第一步,第一个核心处理,这个核心处理完以后,把这个IO扔到下一个核心,再处理下一步,等这个核心空出来以后,处理下一个IO的第一步,这就是所谓的流水线了,所谓的异构就是如此。

不管怎么样,总体看一下基于PCIe的闪存架构,有些PCIe Flash厂商直接采用FPGA自定义闪存控制器;有些PCIe Flash厂商采用现有SATA/SAS闪存模块结合HBA控制器;有些PCIe Flash厂商直接采用最新的PCIe闪存控制器。个人认为第三种方案是未来的趋势,虽然,目前能够提供这种Native PCIe闪存控制器的厂商不多,但是,最近几年此类芯片将会被大量研发,并且符合Nvme标准的控制器将会成为发展趋势。下面对目前市场上出现的几款Native PCIe闪存控制器进行介绍。

Marvell PCIe闪存控制器

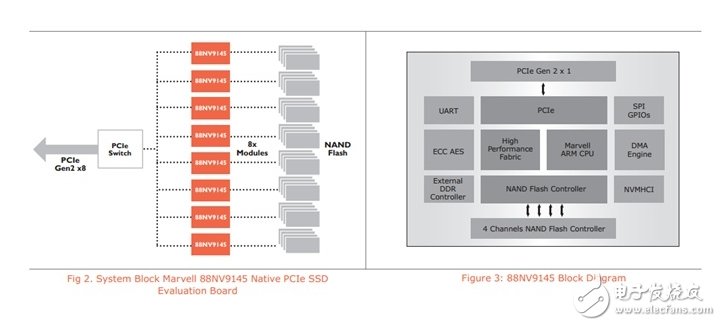

Marvell可以说是第一个(2012年初)推出PCIe闪存控制器的厂商。该闪存控制器可以支持4通道NandFlash芯片,并且可以外扩DRAM,内置ARM处理器。看起来,这款控制器的能力不是很强,管理的NandFlash数量有限。在个人电脑领域,基于这款控制器的存储卡可以替代现有SSD盘。但是,如何利用这款芯片构建存储容量更大的PCIe卡呢?

其实,采用一个PCI桥就可以将多个基于Marvell控制器的Flash模块组合在一起,从而形成一块容量巨大的PCIe存储卡。Marvell控制器88NV9145内部结构和PCIe卡结构如下图所示:

通常可以采用8个存储模块来构建一个PCIe板卡,每个存储模块采用Marvell控制器管理4个闪存芯片,然后通过一个PCIe switch将所有闪存模块连接起来。采用该方案实现的板卡如下图所示:

这种方案的优点是去除了SATA/SAS转换接口,将NandFlash连接到了PCIe总线上。缺点是Marvell的控制器管理能力有限,存储容量将会很受限制。另外,这种方案还增加一层PCIe总线。在控制器模式下,Marvell控制器能够提供的性能为9.3万随机读的IOPS和7万随机写IOPS。

另一个问题需要讨论的是FTL在何处实现?从理论上来讲,FTL可以在Marvell的控制器内部实现。但是,该控制器内部的只提供了一个ARM处理器和ECC校验引擎,处理能力似乎有限。因此,个人认为,采用该控制实现的Flash卡,FTL在host端实现最佳。在Host端的驱动程序中实现FTL,可以对板卡上的存储模块统一管理,从数据冗余角度来看,数据会更加安全,另外,FTL所管理的资源块也会更多,优化空间更大。

LSI PCIe闪存控制器

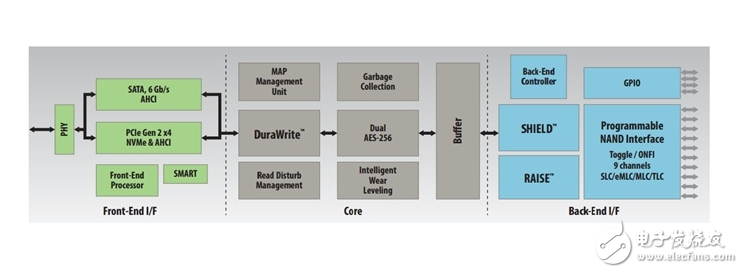

2013年年底的时候,LSI收购Sandforce,获得了闪存控制器芯片。收购后不久推出了Native PCIe控制器SF3700系列。该控制器的内部结构如下图所示:

和Marvell闪存控制器相比,LSI控制器显得更加的高端、大气、上档次。该芯片不仅可以支持传统的SATA接口,而且可以支持PCIe接口。因此如下图所示,采用该系列控制器,可以实现SATA或者PCIe SSD盘。特别在一些笔记本电脑中,可以直接采用PCIe接口的存储卡替代SATA-SSD盘。在企业存储领域,可以采用该芯片实现Native PCIe存储卡。

LSI控制器内部分成三大部分:第一部分是SATA/PCIe接口,包括一个前端处理器,实现PCIe和SATA数据传输的功能;第二部分是SSD控制器的核心,解决NandFlash的写放大、数据映射、数据加密以及垃圾回收(Garbage collection)功能;第三部分后端NandFlash控制器,包含一个后端处理器。该控制器内部的数据压缩算法可以减少NandFlash数据写入量,提高使用寿命。另外,其内部还提供了RAISE(Redundant Array of Independent Silicon Elements)技术,通过该技术增强数据可靠性。RAISE技术类似于RAID,因此会降低空间使用率,每个NandFlash芯片内部都会预留一些资源块作为数据冗余空间。另外,在单个NandFlash芯片内部采用了Shield错误纠正技术,该技术采用了LDPC(Low-Density Parity Check)编解码方式。Shield技术有意思的地方是自适应动态编解码。在正常情况下,采用少量的ECC码,当NandFlash内部的出错达到一定情况后,增加ECC冗余度。增加冗余度之后,IO延迟将会增大。所以,Shield技术是一种性能和可靠性的动态平衡技术。

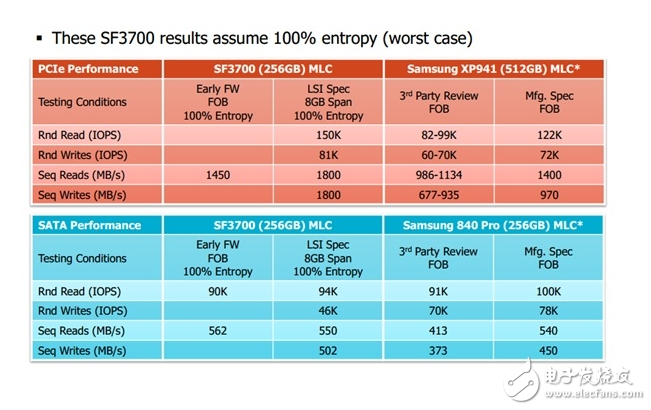

LSI闪存控制器在性能表现方面也不错,其公布的数据如下:

PMC闪存控制器

2013年中旬的时候PMC收购IDT公司的闪存控制器部门。使得PMC开始进攻闪存控制器市场。IDT公司推出的闪存控制器是业界第一款符合Nvme标准的PCIe闪存控制器。基于该控制器研制的PCIe闪存卡如下图所示:

通过IDT的控制器89HF32P08可以将Nand Flash芯片直接接入PCIe总线。和Marvell、LSI的控制器不同,PMC(IDT)的控制器显得更加强悍,其可以管理很多NandFlash芯片颗粒,即单芯片最多可以支持32通道NandFlash芯片。PMC的这款芯片主要的特点如下:

1,可订制的固件程序(Firmware)

2,支持SLC、MLC闪存芯片

3,支持第三代PCIe接口

4,标准的NVM Express控制接口

5,支持XTS-AES-256加密算法

6,防止电源故障、突然断电情况下的数据丢失或者损坏

7,数据完整性和可靠性:ECC数据纠错、闪存通道间RAID保护、端到端的数据保护

采用该控制器可以构建基于PCIe的存储卡和PCIe设备。一个Demo卡演示如下:

和LSI和Marvell的控制器相比,PMC的控制器很具竞争力。

产品实例:PMC的FlashtecTM NVMe 控制器

这是PMC的控制器,首先它有一个片上网络,网络承载16个CPU核心,每个核心里面有一个类似网卡的控制器,网卡连到网络上,多个CPU之间连起来。简单说就是4口路由器或者交换机连起来的网络,多个CPU之间连起来,此外还有硬加速模块。另外还包括以下几部分:

RAM控制器,因为芯片上需要有一定量的RAM放临时数据,写放大,读出来写进去,都要走RAM;

PCIe控制器,这个是跟前端PCIe对等的控制器,IO指令从这儿接收过来;

后端Flash控制器,通过一定数量的通道连Flash颗粒,

加速器(包括缓冲加速器),每做一个操作,都需要有相应的内存,把数据拷到内存里面,内存的维护很费时费力。比如在X86上运行的Linux,其管理内存时需要耗费很多的计算量。对于闪存,精打细算,必须把性能做到极致,因此需用到硬加速。

链表加速器,用链表来记录一些信息,哪块空着,哪块被应用,这块用软件维护很费力,所以需要在这里作加速;

XOR加速器,XOR要用硬加速

最后,来看一下软件的并行度。16个核心,PMC提供的参考的固件,当然SSD厂商会开发自己的固件,把自己优化的东西放进去,优化的算法放进去。基本上包含了这么一些程序,每个IO读的地址可能有重叠,重叠就需要有一个锁定协调,有管命令解析的,有管启动的,有管日志的,有管磨损均衡的,有管查表的,有管写数据的,管前端的PCIe Manager,还有负责boot loader的核心,初始化的配置,需要由它处理,data manager,这是主程序,分析IO指令需要干什么,生成一堆的后续步骤下发下去。其实每一块都可以跑在一个核心上,同一个角色可以复制多份,充分并行。16个核心,达到16份程序并行的运行,16个流水线的Stage,这样就可以屏蔽处理过程中的时延。

基于PCIe总线的闪存控制器是Flash存储的关键器件,也是未来的发展方向。个人认为基于Nvme标准的PCIe闪存控制器会是市场主力。

-

什么是闪存控制器架构?2019-09-27 2377

-

Flashtec NVMe 3108 PCIe第四代NVMe固态硬盘控制器怎么样?2020-11-23 2640

-

闪存控制器2021-07-22 1415

-

可以将多个PCIe设备连接到一般的单个PCIe控制器吗?2023-05-05 514

-

从高速微控制器系列向超高速闪存微控制器的升级2008-08-13 894

-

应用于闪存微控制器的“新闪存”架构技术2010-11-17 959

-

混合信号32KB ISP闪存微控制器2011-06-24 591

-

PMC斥巨资收购IDT的PCIe闪存控制器部门2013-06-03 1464

-

快闪存储器控制器选择技巧2018-03-07 1644

-

闪存驱动器控制器开源2022-08-02 563

-

芯盛智能发布基于RISC-V架构的PCIe4.0控制器芯片2022-08-04 3011

-

存储背后的大脑:NAND 闪存控制器实际上是做什么的?2022-09-05 2552

-

NAND闪存控制器有什么优势2022-10-25 2389

-

浅谈闪存控制器架构2023-08-29 1482

-

PCI11101 PCIe交换机集成USB3.2主机控制器技术解析2025-10-10 672

全部0条评论

快来发表一下你的评论吧 !