基于CMOS和DSA设计方法的数字步进衰减器设计

RF/无线

描述

采用CMOS技术的数字步进衰减器能提供较高的抗ESD能力、高线性度、低插入损耗、串联及并联逻辑接口以及专有的超低噪音负电压发生器。本文基于Peregrine(派更)半导体公司的单片数字步进衰减器(DSA,Digital Step Attenuator)产品系列,阐述了DSA通用设计方法、RF CMOS工艺以及这些器件的性能。

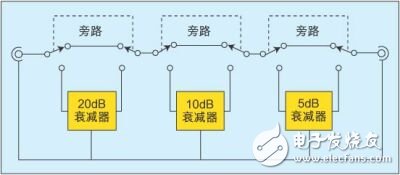

图1:典型的步进衰减器。

DSA通过一个友好的处理器接口控制RF信号强度,被广泛应用于多种RF产品,比如宽动态范围接收器、功率放大器的失真信号消除环路,以及各种有线电视分配系统。

DSA通常具有“线性增益”的特性,是ADC与外界之间的普通接口。与模拟的解决方案相比,它们能提供更高的精确度、更好的温度稳定性以及更小的失真,此外还具有尺寸小、功耗低、易于实现等特点,是一种富有成本效益的解决方案。

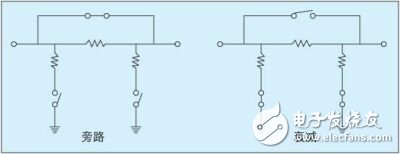

图2:带单刀串联开关的π型衰减器

本文的讨论虽然集中于Peregrine半导体公司的PE4302(50Ω)与PE4304(70Ω)这两种6位DSA器件上,但实际上这种DSA通用设计方法适用于所有类似产品。

单片衰减器的设计

图1是一个典型的步进衰减器,衰减器的每个管脚位于两个单刀双掷(SPDT)开关之间。机械式继电器或开关能提供几乎无损耗的接触,经过仔细设计,这种结构能提供很低的插入损耗和优良的隔离度。

要使一个集成的解决方案提供与此相当的性能,需要一个具有相同特性、导通电阻小以及关断电容在pF以下的固态开关。工作在线性区域的FET开关基本上可以满足这个要求。FET的导通电阻RON虽然为有限值,但是可以在较大的器件中接近0Ω。但是大器件的成本高,如果有办法将串联开关的数量减少一半,例如将每个单元的SPDT换成单刀单掷开关(SPST),则在性能和成本上都可以得到改善。

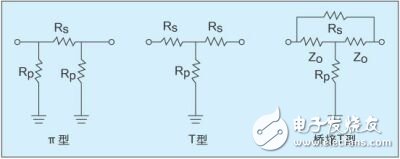

图3:π型、T型以及桥接T型电路。

图2是π型衰减器经过改进的单刀串联开关结构。在每个单元都由一个串联SPST和两个旁路SPST代替原来的两个SPDT。实际上,这一技术将每个单元的插入损耗(IL)降低了一半,SPST结构也比SPDT更简洁,同时性能更好,特别是在高频的时候。

由于所有无源衰减器均为三端网络,这种串联/旁路设计需要与其它拓扑结构一起工作,如T型和桥接T型(见图3)。可能是由于所受培训或者习惯上的原因,工程师似乎更倾向采用π型结构,但是在一个电阻值跨度很大的单片电路中,这可能并不是最好的选择。

设计分立电阻时,电阻值不是一个重要问题。然而在集成电路中,具有特定电阻系数的矩形面积决定了电阻的阻值,这种表面电阻在CMOS工艺中通常约为200Ω/square。集成电路设计面临的难题是,不管电阻值是多倍于200Ω还是远小于200Ω,电阻值都已经成为设计及制造过程中的一个棘手问题。

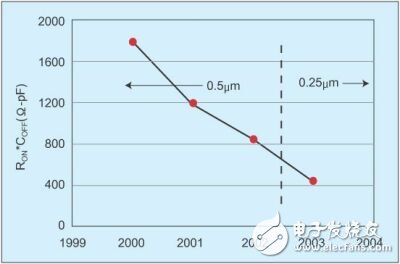

图4:UTSi (RON/COFF)技术的发展图。

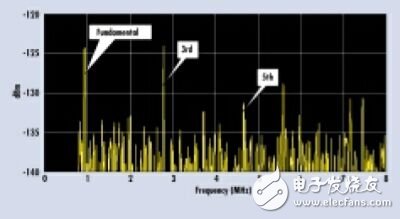

设计阻值非常大或非常小的电阻都需要很大的面积以及很高的成本。大阻值的电阻是长而薄的方形设计,而小阻值的电阻则具有很宽的外形以避免公差问题。表1给出了最低有效位(LSB)为0.5dB的50Ω 6位二进制衰减器的电阻值,其中Rp和Rs分别代表每一个网络中的旁路电阻和串联电阻。

在表1第一行,步进值为0.5dB,这时π型及T型网络所需的电阻比约为600:1(1738/2.9及868/1.4),而桥接T型网络所需的电阻比只有它的一半,约为300:1(844/3)。当步进值为1dB和2dB时,桥接T型网络仍然保持了较低的最大电阻值/最小电阻值的比率,它的电阻值范围缩小了一半,其代价只是增加一个电阻。

图5:典型的插入损耗与温度之间的关系。

当步进值等于或大于4dB时,T型网络的Rpp值较高而成为最佳选择。这形成了一个普遍策略:当步进值较小时使用桥接T型网络,当步进值较大时使用π型网络。

无论是哪种情况,要使DSA具有较高的准确度、优良的线性度、最小的工艺误差以及最佳的温度记录,就需要每一个电阻的阻值远远大于相应开关的导通电阻RON。对于较低的dB值,T型结构的Rp值较高,约为几百欧姆,相比之下旁路开关的RON(通常只有几欧姆)显得很小。同样,当dB值较大时,π型网络旁路电阻的阻值也较大,远远大于旁路开关的RON。

优化方法

图6:PE4302的1dB压缩点与频率的关系。

低RON和低关断电容COFF对于串联FET开关而言都是必不可少的。RON低意味着插入损耗小,但这也意味着需要使用COFF较大的大器件。但是高频工作环境却要求采用COFF很小的小器件,以便使串联阻抗和隔离度都很大。这种矛盾可通过采用能提供适当隔离度的最大器件来解决。例如,当步进值为1dB时,串联开关的隔离度为20dB就很好了。对于一个步进值为20dB的衰减单元而言,隔离度同样为20dB的串联开关,只有17dB为净变化,其余3dB则为误差。对于这点,有的工程师可能会说:“好吧,那就用更高的衰减值来补偿。”理论上这是可行的,但是在实践中,隔离度并不很具重复性,COFF只要有一点点变化,隔离度就会变化很大,因此必须确保对于每一个步进值都有合适的而非过大的隔离度。

电压额定值是另一个可进行优化的地方。每一个串联开关都必须有一个与其衰减值成比例的最高工作电压,例如,衰减步进值小则入射电压下降幅度也较小。旁路开关则完全不同,试想一下零dB结构中的衰减器,所有衰减器都被旁路,每一个旁路开关都必须能承受满摆幅输入电压。

图7:IIP3的对比(工作电压为3V,插入损耗为0dB)。

无论是串联开关还是旁路开关,任何一个特定开关都是由一个、两个、三个或更多串联FET器件组成。因为多个串联FET可以分担入射电压以达到所需的压缩及截取点,所以预期的电压值决定了FET器件的具体个数。随着串联器件数量的增加,晶体管的尺寸必须同步增加,以保持RON及COFF的组合值不变。

在最终DSA产品中,电阻阻值要略高于表1给出的值。每一个衰减器单元都在其设计值上增加了十分之几dB(每个衰减单元的插入损耗),以获得正确的净变化。最后,在旁路电阻旁边适当放上一些低值电容,就可解决其固有的高频性能问题。虽然这对回波损耗有轻微影响,但是可大大提高平整性和精确性。

工艺概述

PE4302及PE4304均为符合商业用途的数字步进衰减器,它们采用已取得专利权的在蓝宝石基底上实现超薄硅(UTSi)的技术制造而成。其几何尺寸目前为0.5微米,水平尺寸为0.25微米。在未来,采用UTSi技术的RF CMOS产品将挑战用GaAs及其它特殊材料制成的产品。表2列出了两种UTSi几何尺寸下的FT及FMAX值。

图8:典型砷化镓/CMOS混合DSA电荷泵的寄生能量频谱图。

蓝宝石基底有效消除了体积效应(基底电容),可提供出色的射频性能,并天生具有抗锁闭能力。采用这种绝缘基底制作出的大电阻和FET器件,几乎没有消耗功率及频率的旁路电容。此外,蓝宝石还为高精度、高衰减的DAS提供必要的隔离度。

RF CMOS还意味着可以在单芯片中集成多种混合信号。这些可集成并可验证的模块包括数字逻辑、EEPROM及SRAM存储器、接口、线性、数据转换、高IP3(三阶截取点)混频器、低噪音PLL、VCO、放大器、电源管理以及高Q值无源射频。新DSA产品的具体性能包括较高的抗ESD能力、接近DC的高线性度、低插入损耗、串联及并联逻辑接口,以及专有的超低噪音负电压发生器,所有这些功能都集成在一个芯片上。

更重要的是,高性能步进衰减器需要先进的射频开关,RON与COFF的乘积是射频开关一个度量指标。图4所描述的设计及工艺的快速发展使Peregrine公司的UTSi技术具有很强的竞争力。

PE4302 的性能测量

图9:PE4302 NVG的寄生能量频谱图。

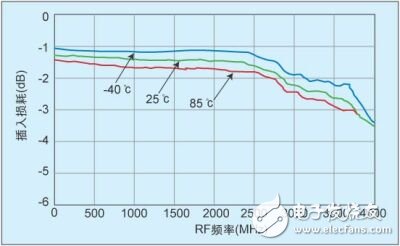

在-40℃到+85℃的温度范围内测出的PE4302典型插入损耗值如图5所示。这里假设将DSA模拟为一个串联电阻,并给DSA开关一个合理的近似值。

使用下列等式:

插入损耗为1.5dB的DSA等效总串联电阻REQ约等于18Ω,它代表6个开关的电阻总和,平均每个开关的电阻约为3Ω,这个数字与CAD模型的结果一致。与目前其它商用DSA产品相比,这种插入损耗为1.5dB的产品性能在同行处于领先地位。

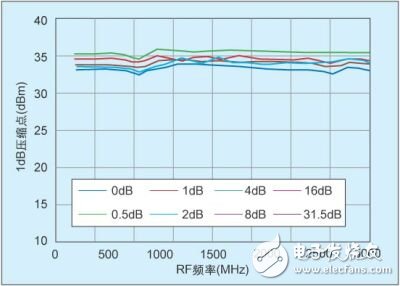

图6显示了主要步进值下的1dB压缩点(P1dB)与频率的关系。这些数值代表实际的瞬时性能,一般总是高于+33dBm。

考虑连续工作时发热及可靠性方面的因素,产品数据表中的最大功率限制会被定得稍微低些。这种做法对于峰值与平均值相差很大的无线电波形而言是很重要的,同时也是表征高线性度的一个更好的指标。

图10:扩大低频范围中的NVG的寄生能量频谱图。

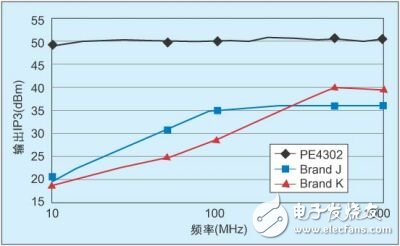

IP3几乎在每一种无线电及有线电视(CATV)应用中都是至关重要的。图7是不同器件(工作电压都为+3V)的IIP3(输入三阶截取点)值,可以看出某些产品的IIP3在低频时有所下降。在1GHz以上,大多数DSA确实都能达到市场需要的规格,但是许多DSA应用在10至300MHz频率的环境中,例如有线电视需要DSA从5MHz开始就具有高线性度。尽管这里提供的只是器件的采样数据,但是对于一般的砷化镓器件而言还是具有代表性的(请注意低端性能)。

回波损耗是另外一个重要参数。许多步进衰减器在无法容忍阻抗失配的混频器和滤波器的旁边工作,失配导致的反射波也会传输到相邻器件,并产生纹波、增益变化及其它问题。

负电压发生器(NVG)的设计

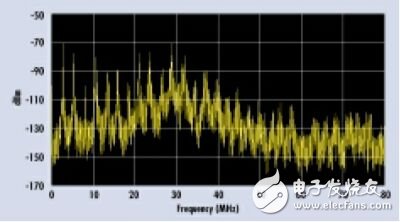

面向这种应用的器件(PE4302)包括一个可选择的片上逆变器,它可产生一个-3V的内部参考电压。与典型的咝咝响的电容电荷泵不同,Peregrine公司的产品使用改进的开关波形和电阻/电容低通滤波以降低噪声。结合这两种方法可设计一种被称为负电压发生器的电路。图8是带有常规电荷泵的GaAs

表1:电阻值与插入损耗、拓扑结构的关系。

DSA的寄生能量频谱图,在一个很宽的带宽上,毛刺高达-70dBm。

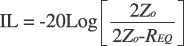

Peregrine产品在同样条件下的频谱如图9所示。试验装置包括一台频谱分析仪,RBW=VBW=10KHz,REFLVL=-70dBm, 在它的前面是一台惠普50MHz低噪音放大器(图形作了增益调整)。除了DC附近一个几乎看不见的元件外,该图形反映了测量到固有噪声电平。

图10显示的是采用更窄滤波器带宽的近距离低频频谱图。该图减去了器件关闭电源时的标称固有噪声电平(约为-135dBm)以便更好地显示NVG的寄生信号成份。在NVG启动并工作的情况下,整个器件的能量消耗仅为几十微安培(工作电压为3V)。只要在Vss/GND管脚加上-3V的电压,就可以完全关闭NVG。

新增的功能

表2:UTSi性能与几何尺寸的关系

在CMOS芯片设计的早期阶段,可看到两个没有使用的管脚:PUP1和PUP2,用它们将衰减器上电后的状态设置为四个值中的一个:0、8、16或31dB。这种预先设置为发射机的排列带来实际好处。设置上电状态为最大衰减值可以遏制输出,同时控制器以及各种环路还可以保持它们的正常工作状态。潜在的寄生信号在到达天线及A-I-R之前就被拦截。

由于实现这个功能的额外逻辑电路实际上是免费使用的,所以单片CMOS具有很大的优势。

本文小结

本文讨论的先进DSA设计方法能将宽带线性度及精确度提高到一个新的水准。与许多RF器件不同,这种电路设计还能扩展到在电路中包括多种接口和特性,想必这一定会引起数字和系统设计者的兴趣。

-

探索F1951数字步进衰减器:通信基础设施的理想之选2025-12-23 78

-

F1975数字步进衰减器:性能、编程与应用全解析2025-12-17 98

-

浅谈步进衰减器的使用方法2023-07-04 1666

-

什么是射频衰减器?2023-05-23 1717

-

什么是射频衰减器?如何为我的应用选择合适的RF衰减器?2023-01-24 1855

-

如何选择合适的RF衰减器?射频衰减器的分类有哪些?2022-09-28 5566

-

PULSAR数字步进衰减器的标准衰减范围2021-11-09 1446

-

PE4314数字步进衰减器2021-03-26 980

-

PE4312C-Z数字步进衰减器2019-05-08 1833

-

TQP4M9072数字步进衰减器的详细数据手册免费下载2018-07-30 1326

-

QPC3624数字步进衰减器2018-07-16 1132

-

RFSA3623数字步进衰减器2018-06-25 1078

-

RFSA3613数字步进衰减器2018-06-11 1328

-

基于CMOS工艺的数字步进衰减器的设计2010-09-17 637

全部0条评论

快来发表一下你的评论吧 !