利用AD574A设计基于FPGA的高速数据采集系统

FPGA/ASIC技术

描述

在自动控制与检测系统中,经常涉及到模拟信号的采集与处理,一般的做法是使用单片机和其他芯片将系统资源扩展进而实现期望的功能,但是这种做法会使得外部电路规模和系统成本显著增加,从而导致系统设计的复杂性,一般很难达到较高的采样速度。设计基于FPGA的高速采样控制系统,灵活方便,可以很大程度提高系统的整体性能。

1、系统构成及工作原理

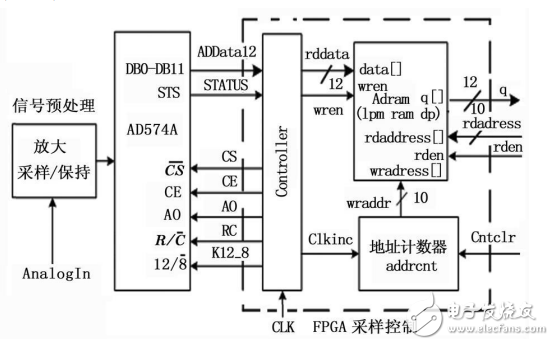

本文所设计的数据采集控制系统结构与工作原理如图1所示。该系统由FPGA采样控制模块构成系统的核心电路,该模块主要由控制器(Controller)、内嵌双口RAM(Adram)、地址计数器(Addrcnt)等三部分构成。系统工作原理如下:控制器(Controller)作用是对AD574A进行控制和对Adram执行写入操作。地址计数器(Addrcnt)作用分两种情况:(1)当计数器的清零端Cntclr为高电平时,其输出为0;(2)当时钟Clkclr的上升沿到来时,其开始计数,并提供存储地址保存采集数据。内嵌双口RAM(Adram)的作用是在FPGA内部实现的RAM,存储采集数据,与此同时外部设备(比如DSP、单片机等)可以读入其数据,以做进一步处理。在wren处于高电平时,采集数据就可以根据输入地址保存在相应的存储单元之中。

2、设计控制器(Controller)模块

2.1、AD574A主要特点和工作时序图

作为一种带有三态缓冲器的快速12位逐次比较式A/D转换芯片,AD574A可以直接与8位或16位微处理器相连,而不需要附加逻辑接口电路。其片内有时钟脉冲源和基准电压源,也无需外接时钟和参考电压等电路就可以正常工作。AD574A的转换时间为25μs,线性误差在±1/2LSB内。芯片内含有逐次STS逼近式寄存器SAR、DAC转换电路、控制逻辑、比较器及三态缓冲器等。采用单通道单极性或双极性电压输入和28脚双立直插式封装。AD574A由12位A/D转换器、控制逻辑、三态输出锁存缓冲器、10V基准电压源四部分构成,芯片具有两种工作模式:单一工作模式和全速工作模式(图1)。

图1 数据采集控制系统的原理结构

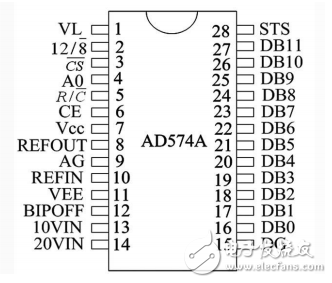

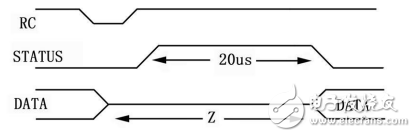

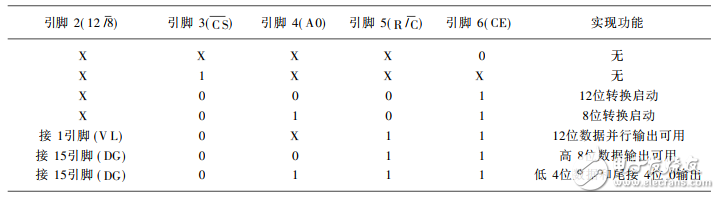

AD574A的封装形式双列直插式,共有28个引脚(图2),其中,CS为片选信号,低电平有效;CE为芯片允许信号,高电平有效;只有CS和CE同时有效,AD574A才能工作。R/C为读出或转换控制信号,用于控制ADC574A是转换还是读出。当为低电平时,启动A/D转换;当为高电平时,将转换结果读出。12/8为数据输出方式控制信号,当为高电平时,输出数据为12位;当为低电平时,数据是作为2个8位字输出。A0转换位数控制信号,当为高电平时,进行8位转换,为低电平时进行12位转换。其操作功能见表1,相应的工作时序图见图3。

图2 引脚图

图3 工作时序图

表1不同引脚状态组合实现的AD574A操作功能表

2.2、控制器(Controller)模块功能实现

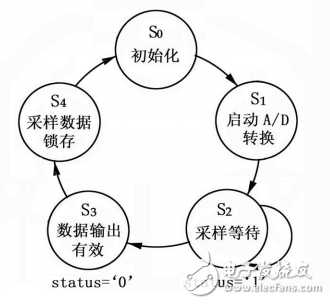

控制器(Controller)主要任务是对AD574A的控制和对Adram执行写入操作,这里采用VHDL语言来实现,VHDL是基于状态机的一种语言[2]。图3是AD574A的时序图,在此基础上可绘出控制器(Controller)的状态机状态转换图[3],如图4所示。

图4 控制器(Controller)模块的状态转换关系

通过对状态转换图的分析可看出,其5个状态的关系如下:

(1)S0初始化状态:AD574A尚未被选中,控制输出状态分别为CS=1,RC=1,CE=1,内部锁存信号为lock=0;

(2)S1启动A/D转换状态:AD574A芯片被选中并开始启动A/D转换,控制输出状态分别为CS=0,RC=0,CE=1,内部锁存信号为lock=0;

(3)S2采样等待状态:数据采样,控制输出状态分别为CS=0,RC=0,CE=1,内部锁存信号为lock=0;

(4)S3数据输出有效状态:数据输出有效,控制输出状态分别为CS=0,RC=1,CE=1,内部锁存信号为lock=1;

(5)S4采样数据锁存状态:采样数据锁存,控制输出状态分别为CS=0,RC=1,CE=1,内部锁存信号为lock=0[4]。

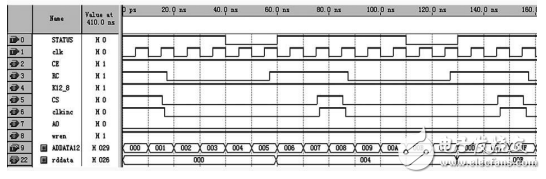

该模块利用VHDL语言来编程实现,并且在MAX+PLUSⅡ的环境进行仿真测试[2],图5为时序仿真结果。

图5 控制器(Controller)模块仿真结果

3、设计内嵌双口(Adram)

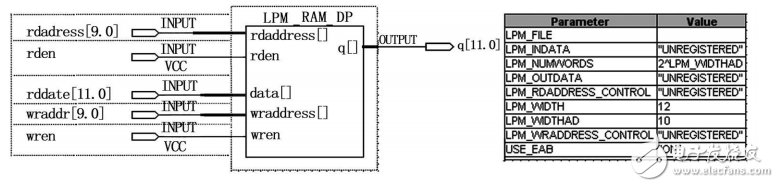

内嵌双口RAM由基于参数可设置模块库LPM(LibraryofParameterizedModules)实现,LPM中包含较多典型电路模块,可以通过图形或硬件描述语言的形式进行调用[5]。在MAX+PLUSII中可以很方便地调用LPM库函数,设计者既可以在直接图形输入法中调用,也可以通过HDL源文件调用,从而提高IC设计的效率。通过采用LPM标准,设计输入工具、综合工具[6]、实现工具,对于同一个逻辑功能在不同抽象层次的描述达成了统一[7],LPM输入法具备与图形输入法同等的高效率。在megafunction/storage库中提供3种RAM模块,分别为LPMRAMIO、LPMRAMDQ、LPMRAMDP。其中LPMRAMDP可用来构建双端口RAM,将输入、输出完全分开,即数据输入时使用输入地址总线,输出时使用输出地址线[8],这种设计充分发挥CPLD/FPGA处理速度高,以及并行处理的特点,进而提高数据的吞吐量。为实现设计要求,LPMRAMDP各参数按图6设定。

图6 LPMRAMDP参数设定

4、设计地址计数器(Addrcnt)

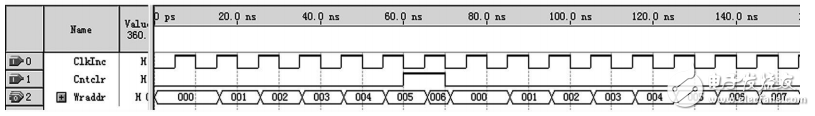

利用VHDL语言实现地址计数器(Addrcnt),图7为其时序仿真。

图7 Addrcnt模块仿真结果

5、结束语

利用一种高性能的12位逐次逼进式A/D转换器AD574A作为控制器,构建了一种基于FPGA的数据采集控制系统。系统包含

(1)内嵌双口,在FPGA内部实现的RAM用于写入操作;

(2)地址计数器,用于提供存储地址保存采集数据。测试结果显示,该系统不仅简化了电路,系统整体性能也得以提升,具备高采样精度、高集成度,并且速度快、灵活性强、可靠性高,易于升级与扩展。

-

AD574A:完整的12位A/D转换器数据表2021-04-22 1224

-

如何利用FPGA实现高速连续数据采集系统设计?2021-04-08 2415

-

基于FPGA的高速数据采集系统该怎么设计?2019-09-05 2366

-

基于AD574A的脑电信号采集及在线仿真2017-12-20 9024

-

基于FPGA的新型高速CCD图像数据采集系统2016-09-22 731

-

基于FPGA的高速数据采集系统设计_杨江涛2016-05-17 951

-

高速数据采集系统中的FPGA的设计2016-05-10 876

-

FPGA芯片在高速数据采集缓存系统中的应用2010-03-30 1228

-

AD574A与MCS-51单片机接口2009-10-25 4839

-

基于USB2.0与FPGA技术的高速数据采集系统的设计2009-04-22 2022

-

AD574A中文资料2008-12-21 2041

全部0条评论

快来发表一下你的评论吧 !