利用CPLD实现AD574控制器的设计

AD技术

描述

CPLD

CPLD(Complex Programmable Logic Device)复杂可编程逻辑器件,是从PAL和GAL器件发展出来的器件,相对而言规模大,结构复杂,属于大规模集成电路范围。是一种用户根据各自需要而自行构造逻辑功能的数字集成电路。其基本设计方法是借助集成开发软件平台,用原理图、硬件描述语言等方法,生成相应的目标文件,通过下载电缆(“在系统”编程)将代码传送到目标芯片中,实现设计的数字系统。

CPLD主要是由可编程逻辑宏单元(MC,Macro Cell)围绕中心的可编程互连矩阵单元组成。其中MC结构较复杂,并具有复杂的I/O单元互连结构,可由用户根据需要生成特定的电路结构,完成一定的功能。由于CPLD内部采用固定长度的金属线进行各逻辑块的互连,所以设计的逻辑电路具有时间可预测性,避免了分段式互连结构时序不完全预测的缺点。

发展历史及应用领域

20世纪70年代,最早的可编程逻辑器件--PLD诞生了。其输出结构是可编程的逻辑宏单元,因为它的硬件结构设计可由软件完成(相当于房子盖好后人工设计局部室内结构),因而它的设计比纯硬件的数字电路具有很强的灵活性,但其过于简单的结构也使它们只能实现规模较小的电路。为弥补PLD只能设计小规模电路这一缺陷,20世纪80年代中期,推出了复杂可编程逻辑器件--CPLD。此应用已深入网络、仪器仪表、汽车电子、数控机床、航天测控设备等方面。

器件特点

它具有编程灵活、集成度高、设计开发周期短、适用范围宽、开发工具先进、设计制造成本低、对设计者的硬件经验要求低、标准产品无需测试、保密性强、价格大众化等特点,可实现较大规模的电路设计,因此被广泛应用于产品的原型设计和产品生产(一般在10,000件以下)之中。几乎所有应用中小规模通用数字集成电路的场合均可应用CPLD器件。CPLD器件已成为电子产品不可缺少的组成部分,它的设计和应用成为电子工程师必备的一种技能。

如何使用

CPLD是一种用户根据各自需要而自行构造逻辑功能的数字集成电路。其基本设计方法是借助集成开发软件平台,用原理图、硬件描述语言等方法,生成相应的目标文件,通过下载电缆(“在系统”编程)将代码传送到目标芯片中,实现设计的数字系统。

这里以抢答器为例讲一下它的设计(装修)过程,即芯片的设计流程。CPLD的工作大部分是在电脑上完成的。打开集成开发软件(Altera公司 Max+pluxII)→画原理图、写硬件描述语言(VHDL,Verilog)→编译→给出逻辑电路的输入激励信号,进行仿真,查看逻辑输出结果是否正确→进行管脚输入、输出锁定(7128的64个输入、输出管脚可根据需要设定)→生成代码→通过下载电缆将代码传送并存储在CPLD芯片中。

7128这块芯片各管脚已引出,将数码管、抢答开关、指示灯、蜂鸣器通过导线分别接到芯片板上,通电测试,当抢答开关按下,对应位的指示灯应当亮,答对以后,裁判给加分后,看此时数码显示加分结果是否正确,如发现有问题,可重新修改原理图或硬件描述语言,完善设计。设计好后,如批量生产,可直接复制其他CPLD芯片,即写入代码即可。如果要对芯片进行其它设计,比如进行交通灯设计,要重新画原理图、或写硬件描述语言,重复以上工作过程,完成设计。这种修改设计相当于将房屋进行了重新装修,这种装修对CPLD来说可进行上万次。

AD574

AD574是美国核拟器件公司Analog Devices) 生产的12 位逐次逼近型快速A/D 转换器。其转换35us,转换误差为土0.05%,是前我国应用广泛,价格适中的A/D转换器。其内部含三态电路,可直接与各种微处理器连接,且无须附加逻辑接口电路,便能与CMOS 及TTL 电平兼容。内部配置的高精度参考电压源和时钟电路,使它不需要任何外部电路和时钟信号,就能实现A/D转换功能,应用非常方便。

利用CPLD实现AD574控制器的设计

基于PCI总线的汽车电子系统对传感器的信号进行采样分析和处理时,均需要利用A/D转换模块。本文选用AD574芯片实现汽车电子系统信号调理板上传感器信号的A/D转换。

传感器采集的模拟信号在信号调理板卡上经过放大、滤波后,通过AD574进行A/D转换后,经PCI总线读取到MCU中进行分析处理。设计中通过应用VerilogHDL硬件可编程语言在CPLD器件上实现对AD574的控制,节省了MCU的指令执行时间,提高读写速度,增强了可靠性和稳定性。

1.AD574工作原理

1.1AD574结构及特性

AD574是美国模拟数字公司推出的单片高速12位逐次比较型A/D转换器,内置双极性电路构成的混合集成转换芯片,具有外接元件少、功耗低、精度高等特点,同时具有自动校零和自动极性转换功能,只需外接少量的阻容器件即可构成一个完整的A/D转换器。

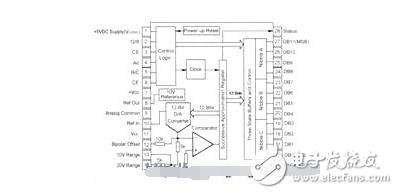

AD574内部结构及外部引脚如下图所示。

AD574的基本特点和参数如下:AD574带有内部采样保持的12位逐次比较型模/数转换器;转换速率达25μs,总线访问时间最大为150ns;非线性误差小于±1/2LBS或±1LBS;数据可采用12位或8位丙种模式并行输出;四种单极或双极电压输入范围分别为±5V、±IOV、0V~10V和0V~20V;采用双电源供电方式,模拟电路电压为±l2V或者±l5V,数字电路电压为±5V。

1.2AD574引脚功能及时序控制

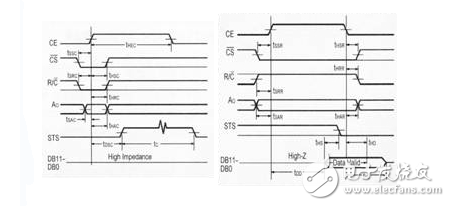

AD574的逻辑控制需要用到以下端口:数据输出位选择输入端12/8、片选信号输入端CS、读/转换状态输入端R/C、操作使能端CE、位寻址/短周期转换选择输入端AO以及转换状态输出端STS。

当CE=1且CS=0同时满足时,AD574开始正常工作。AD574处于工作状态时,R/C=0时,开始AID转换;当R/C=1时,读出数据。数据输出位选择输入端12/8和AO端用来控制启动转换的方式和数据输出格式。当AO=0时,启动转换方式按完整的12位AID转换方式进行;当AO=1时,按8位A/D转换方式进行。当R/C=1,AD574处于数据状态,此时AO和数据输出位选择输入端12/8控制数据输出的格式。当12/8=1时,数据以12位并行输出;当12/8=0时,数据以8位分两次输出;且当AO=0时,输出A/D转换数据的高8位;AO=1时输出A/D转换数据的低4位,转换数据的低四位占一个字节的高半字节,低半字节补零。

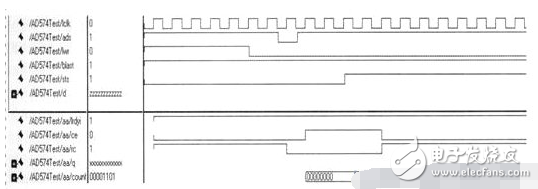

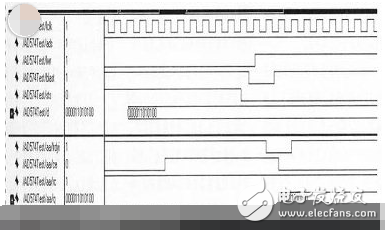

AD574的工作时序分别如下图所示。

1.3AD574与PCI的接口时序

系统设计中AD574与PCI接口芯片PCI9052相连进行数据传输。AD574的转换控制及读取数据控制信号均采自PCI9052的引脚,转换后的数据在PCI9052的控制下通过PCI总线传输到MCU中进行分析与处理。通过CPLD设计实现PCI9052对AD574的逻辑控制和时序控制,对应的时序如图4所示。

时序图中ADS#、BLAST、LRDYi和LCLK均为PCI总线接口芯片PCI9052的信号引脚。ADS#是PCI总线上发起一次访问的地址锁存引脚,用于控制AD574的采样时间;BLAST为PCI总线上一次访问的最后一个数据期,用于控制AD574的数据读取;LRDYi为从设备准备引脚,有效则表明PCI9052可以开始对本地端设备进行读写数据,文中用于控制AD574的数据转换完成的有效信号,以便开始读取数据;LCLK为PCI9052产生的一个局部时钟信号,用于控制时序逻辑。

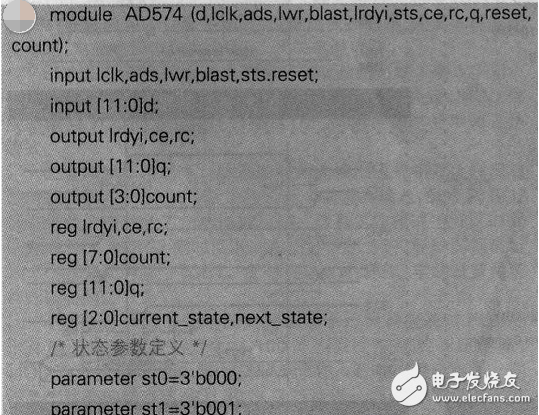

2CPLD设计与实现基于VerilogHDL硬件描述语言实现的ADC574采样控制设计源程序如下:

代码中信号定义与图 2时序图中引脚对应,同时设计了一个计数器用于控AD574的时序,以满足AD574的转换精度及读取要求。

QUARTus 11软件为可编程片上系统(SOPC)设计提供了一个工具齐全、功能强大的设计环境。在根据需要选择好CPLD器件系列后,采用Veilog HDL语言输入方式编写控制组合逻辑代码和测试激励代码,利用 Quartus 11 软件白带的工具分析综合代码,进行布线、布局、资源分配以及分析时序、波形仿真。Quartus11还为第三方 EDA工具软件提供了友好的接口,可以直接在Quartus 11 中调用 Modelsim软件进行仿真。

利用 Quartus 11 6.0 和 Modelsim6.1 软件系统在MAX3000A 系列可编程器件上使用了 50%左右的资源实现了对AD574 的采样、AID 转换及数据读取的控制。本文在 Mod-elsim6.1 软件中进行仿真的结果分别如下图所示。

经过验证,电路能顺利、方便地控制AD574 的工作和运行,转换过程和结果均符合AD574的时序逻辑和精度要求。

3. 结 语

利用 CPLD技术实现逻辑和时序的控制,在硬件电路上简化了设计的复杂度,基于CPLD 的可编程特点,可以在不改变硬件电路整体结构的情况下对设计电路进行改造、升级和维护;在软件程序上减少了操作指令,一定程度上提高了数据处理和读取的速度。

-

请问AD574怎么把模拟量转换为数字量?2023-12-11 474

-

利用MAX II CPLD实现LCD控制器2023-11-10 444

-

基于AD574的太阳能电池监测系统2018-10-18 2519

-

AD574在心电采集系统中的应用2017-12-20 6140

-

基于51单片机和AD574的简易电子秤的设计2017-12-18 18019

-

利用CPLD来替代微控制器的设计2017-09-12 891

-

高速A/D转换芯片AD574与单片机的配接2016-01-25 1198

-

新人问问题,关于AD5742015-03-25 5679

-

求有AD574的Altium Designer元件库,另外顺便问下AD574好还是AD16...2014-04-20 5948

-

求AD574芯片的中文资料2012-05-27 2313

-

基于EPM7128SLC84实现的AD574A采样控制器2009-10-13 2441

-

AD574在数据采集中的应用2009-04-28 799

-

12位A/D转换器AD5742009-01-14 5568

全部0条评论

快来发表一下你的评论吧 !